Ответы электроника. ответы электроника. 1. Контактные явления в полупроводниковых приборах, p n переход, виды полупроводниковых диодов 3

Скачать 2.83 Mb. Скачать 2.83 Mb.

|

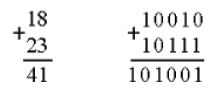

Сумматор. Сумматор параллельного типаР  ассмотрим принцип работы сумматора, для чего вначале сравним суммирование двух десятичных и двоичных чисел А + В: ассмотрим принцип работы сумматора, для чего вначале сравним суммирование двух десятичных и двоичных чисел А + В:По внешнему виду правила одинаковы: Сложение производится поразрядно - от младшего разряда к старшему (справа налево); В младшем разряде вычисляется сумма младших разрядов слагаемых А{) и В(). Эта сумма в данной системе счисления может быть записана однозначным числом S(), либо двухзначным числом P0S0. Число Р{) называют переносом в старший разряд или просто переносом. Во всех последующих разрядах находится сумма этих разрядов слагаемых Ai и Bi при Рi-1≠0 к этой сумме добавляется перенос: результат сложения в i-м разряде записывается в виде Si или РiSi,. Сумматор - это устройство, которое разряд за разрядом (начиная с младшего разряда) складывает «единицы» и «нули» первого и второго слагаемых. Таблица истинности для сложения двух одноразрядных двоичных чисел имеет вид:

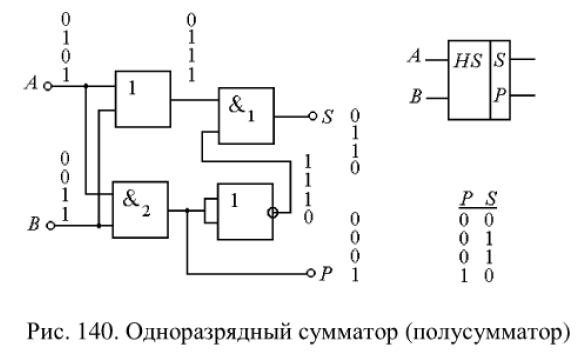

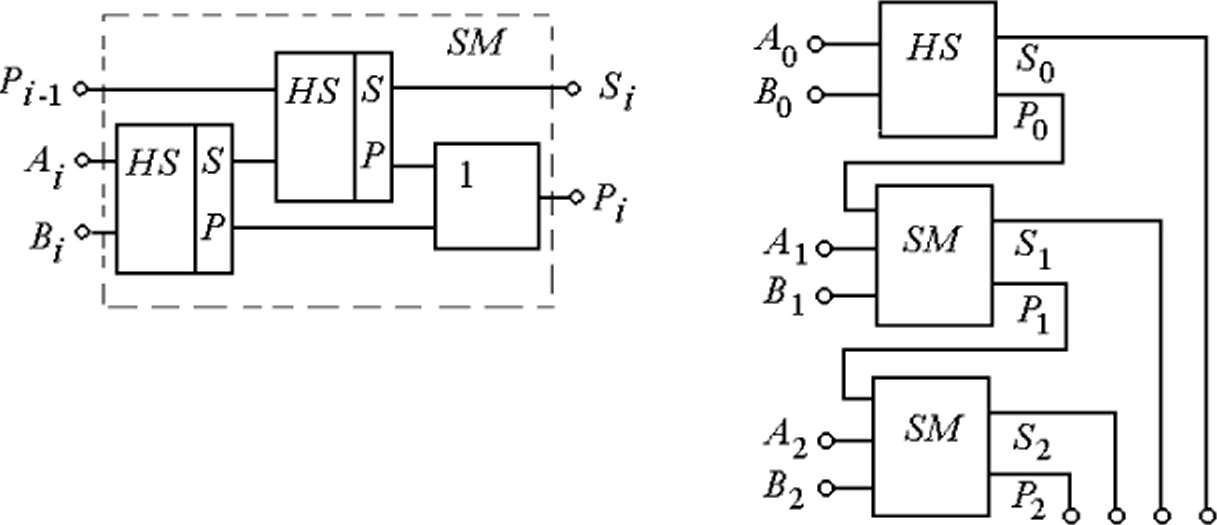

Первые три операции может выполнить один элемент ИЛИ. Что же касается четвертого сочетания слагаемых (1 + 1), то здесь необходим перенос «единицы» в следующий разряд. Это реализуется с помощью нескольких логических элементов. Работу одноразрядного сумматора иллюстрирует рис. 140. Оба слагаемых подаются не только на элемент ИЛИ, но одновременно еще и на элемент И2, а с него на элемент НЕ. На рис. 140 показаны в столбик все возможные варианты суммирования двух одноразрядных чисел. В первых трех случаях (0+0, 0+1, 1+0) элемент И2 не переключается, так как на его входе нет двух единичных импульсов. А значит, в этих случаях на выходе инвертора будут логические единицы. Если на вход сумматора одновременно поступают два единичных импульса (1 + 1), то на выходе сумма (5) будет ноль, а перенос Р примет значение логической единицы. Р  ассмотренная схема может использоваться только для суммирования в младшем разряде и называется поэтому полусумматором. Полусумматор обозначается на схемах буквами HS. ассмотренная схема может использоваться только для суммирования в младшем разряде и называется поэтому полусумматором. Полусумматор обозначается на схемах буквами HS.При суммировании двух многоразрядных чисел для каждого разряда (кроме младшего) необходимо использовать устройство, имеющее дополнительный вход переноса. Такое устройство называется полным сумматором (рис. 141). Соединяя полусумматоры и полные сумматоры определенным образом, получают устройства для сложения нескольких разрядов двоичных чисел. Например, трехразрядный сумматор показан на рис. 142. На выходах Sq — S2 формируется двоичный код суммы двух трехразрядных чисел А2А1А0 и В2В1В0, а на выходе Р2 формируется сигнал переноса, так как при сложении двух трехразрядных двоичных чисел может получиться четырехразрядное число. Одноразрядные, двухразрядные и четырехразрядные сумматоры выпускают в виде интегральных микросхем. С целью наращивания разрядности суммируемых чисел микросхемы соединяют последовательно, для чего выход переноса соединяют с входом переноса микросхем, принадлежащим более высоким разрядам. У микросхемы, суммирующей младшие разряды чисел, вход переноса следует соединить с общим проводом.  Рис. 141. Полный сумматор Рис. 142. Трехразрядный сумматор Приведенный на рис. 142 сумматор называется параллельным, поскольку информационные сигналы поступают па все входы одновременно. В параллельном сумматоре для каждого двоичного разряда нужен отдельный сумматор. |