Микропроцессорная система управления пуском и_________ _______________торможением асинхронного двигателя с фазным ротором_______. Курсовая работа.Кабальновdocx. 1Назначение выводов atmega128 3

Скачать 0.66 Mb. Скачать 0.66 Mb.

|

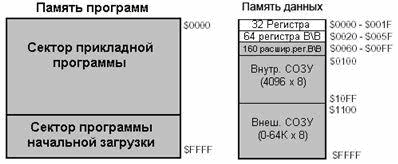

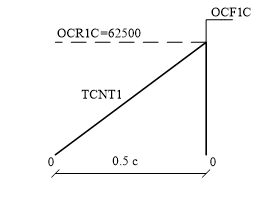

1 2 2 Организация памяти и портов ввода/вывода микроконтроллераМикроконтроллеры AVR имеют раздельные пространства адресов памяти программ и данных (гарвардская архитектура). Организация памяти МК ATMega128 показана на рисунке 2.1  Рисунок 2.1 - Организация памяти микроконтроллера ATmega128 Высокие характеристики семейства AVR обеспечиваются следующими особенностями архитектуры: 1) в качестве памяти программ используется внутренняя флэш-память. Она организована в виде массива 16-разрядных ячеек и может загружаться программатором, либо через порт SPI; 2) 16-разрядные память программ и шина команд вместе с одноуровневым конвейером позволяют выполнить большинство инструкций за один такт синхрогенератора (50 нс при частоте FOSC=20 МГц); 3) память данных имеет 8-разрядную организацию. Младшие 32 адреса пространства занимают регистры общего назначения, далее следуют 64 адреса регистров ввода-вывода, затем внутреннее ОЗУ данных объемом до 4096 ячеек. Возможно применение внешнего ОЗУ данных объемом до 60 Кбайт; 4) внутренняя энергонезависимая память типа EEPROM объемом до 4 Кбайт представляет собой самостоятельную матрицу, обращение к которой осуществляется через специальные регистры ввода-вывода.  Рисунок 2.2 - Регистры общего назначения микроконтроллера ATmega128 Как видно 32 регистра общего назначения (РОН) включены в сквозное адресное пространство ОЗУ данных и занимают младшие адреса. Хотя физически регистры выделены из памяти данных, такая организация обеспечивает гибкость в работе. Регистры общего назначения прямо связаны с АЛУ. Каждый из регистров способен работать как аккумулятор. Большинство команд выполняются за один такт, при этом из регистров файла могут быть выбраны два операнда, выполнена операция и результат возвращен в регистровый файл. Старшие шесть регистров могут использоваться как три 16-разрядных регистра, и выполнять роль, например, указателей при косвенной адресации. Следующие 64 адреса за регистрами общего назначения занимают регистры ввода-вывода (регистры управления/состояния и данных). В этой области сгруппированы все регистры данных, управления и статуса внутренних программируемых блоков ввода-вывода. При использовании команд IN и OUT используются адреса ввода-вывода с $00 по $3F. Но к регистрам ввода-вывода можно обращаться и как к ячейкам внутреннего ОЗУ. При этом к непосредственному адресу ввода-вывода прибавляется $20. Адрес регистра как ячейки ОЗУ приводится далее в круглых скобках. Регистры ввода-вывода с $00 ($20) по $1F ($3F) имеют программно доступные биты. Обращение к ним осуществляется командами SBI и CBI, а проверка состояния – командами SBIS и SBIC. 3 Разработка принципиальной схемы и программного обеспеченияК порту D подключены кнопки и блок-контакты контакторов. Кнопка «пуск» SB1 подключена к выводам внешнего прерывания PD6 (INT6), кнопка «стоп» SB2 к выводу по опросу PD3. К выводам PD4, PD5, PD7 подключены блок-контакты контакторов КМ1, КМ2, КМ3 соответственно. Силовые контакты контактора КМ1 подключают статор асинхронного двигателя с фазным ротором к сети переменного тока. Силовые контакты контактора КМ2 шунтируют пусковую ступень в роторной цепи. Силовые контакты контактора КМ3 отключают статор двигателя от сети переменного тока и подают в две фазы статора постоянный ток. К порту В подключены катушки промежуточных реле (к PB0-KL1, к PB1-KL2, к PB2-KL3. Соответствующие блок-контакты промежуточных реле KL1-KL3 управляют включением катушек контакторов КМ1-КМ3. Сигнал с датчика скорости подается на вывод PF5 встроенного пятого канала АЦП. Внешние прерывание INT6 срабатывают по спадающему фронту сигнала. 8-разрядный таймер Т1 работает в режиме СТС по каналу С. Прерывание от таймера возникает через время, определяемое по формуле:  где СLK – коэффициент делителя частоты, х – число, записанное в регистр сравнения канала ОСR1С,  тактовая частота кварцевого генератора, тактовая частота кварцевого генератора, . .Для заданной аппаратной выдержки в 0,5 секунд число х рассчитывается по формуле:  Выбираем коэффициент делителя частоты таким образом, чтобы число х было меньше и по возможности ближе к 65535. Для такого условия подходит СLK=64.  Диаграмма работы таймера 1 в режиме СТС по каналу С приведена на рисунке 3.1  Рисунок 3.1 – Диаграмма работы таймера 1 в режиме СТС С В данной задаче содержимое счетного регистра TCNT1 увеличивается каждый 64 период тактовой частоты. Когда содержимое счетного регистра TCNT1 совпадет с содержимым регистра сравнения OCR1С (62500), установится флаг совпадения С от таймера Т1 OCF1С. После чего содержимое счетного регистра обнуляется. Определим значения битов регистров управления. Формат регистра разрешения внешних прерываний EIMSK представлен на рисунке 3.2 EIMSK

Рисунок 3.2 – Формат регистра EIMSK

В соответствии с представленным в таблице 3.1 описанием, устанавливаем следующие биты EIMSK.

Рисунок 3.3 - Формат регистра EICRA

Рисунок 3.4 - Формат регистра EICRB Условия генерации внешних прерываний INT7..INT1 определяются значениями бит регистров EICRA и EICRB, согласно таблице 3.2 . Таблица 3.2- Определение условий генерации внешних прерываний INTn

В соответствии с представленным в таблице 3.1 описанием, устанавливаем следующие биты регистров EICRA, EICRB. Формат регистра EICRA

Формат регистра EICRB

Что соответствует условию генерации внешнего прерывания INT6 по спадающему фронту. В регистре ETIMSK необходимо разрешить прерывание от таймера Т1 по совпадению C, то есть установить в единицу бит OCIE1C.

Бит 5 TICIE3. Разрешение прерывания по событию «Захват» таймера Т3. Бит 4 OCIE3А. Разрешение прерывания по событию «Совпадение А» таймера Т3. Бит 3 OCIE3B. Разрешение прерывания по событию «Совпадение В» таймера Т3. Бит 2 TOIE3. Разрешение прерывания по переполнению таймера Т3. Бит 1 OCIE3С. Разрешение прерывания по событию «Совпадение С» таймера Т3. Бит 0 OCIE1C. Разрешение прерывания по событию «Совпадение С» таймера Т1. Для выбора режима работы таймера 1 СТС C при CLK=64 в регистры управления TCCR1A, TCCR1B запишем следующие значения. TCCR1A

TCCR1B

Управление внутренним АЦП осуществляется с помощью регистра управления и состояния АЦП ADCSRA (ADCSR для AVR STUDIO 4) и регистр управления мультиплексором АЦП ADMUX. Форматы этих регистров представлены в таблицах 3.3 и 3.4 соответственно. Таблица 3.3 – Формат регистра ADCSRA

ADEN – включение АЦП. (1 – включено, 0 – выключено); ADSC – запуск преобразования (1 – начать преобразование); ADFR – выбор режима работы АЦП (0 – одиночное, 1 – непрерывное преобразование); ADIF – флаг прерывания от компаратора (устанавливается в 1 по завершению преобразования); ADIE – разрешает прерывания от компаратора; ADPS2 – ADPS0 – выбор коэффициента деления тактовой частоты, согласно таблице 3.4 Таблица 3.4 – Выбор коэффициента деления тактовой частоты

Таблица 3.5 – Формат регистра ADMUX для ADC5

REFS1 и REFS0 – определяют источник опорного напряжения согласно таблице 3.6 ADLAR – выравнивание результата преобразования (1 – влево, 0 – вправо); MUX4 – MUX0 – определяют входной канал согласно таблице 3.7. Таблица 3.6 – Выбор источника опорного напряжения

Таблица 3.7 – Выбор канала АЦП

Программа представлена в таблице 3.8. Таблица 3.8 – Программа для ATmega128

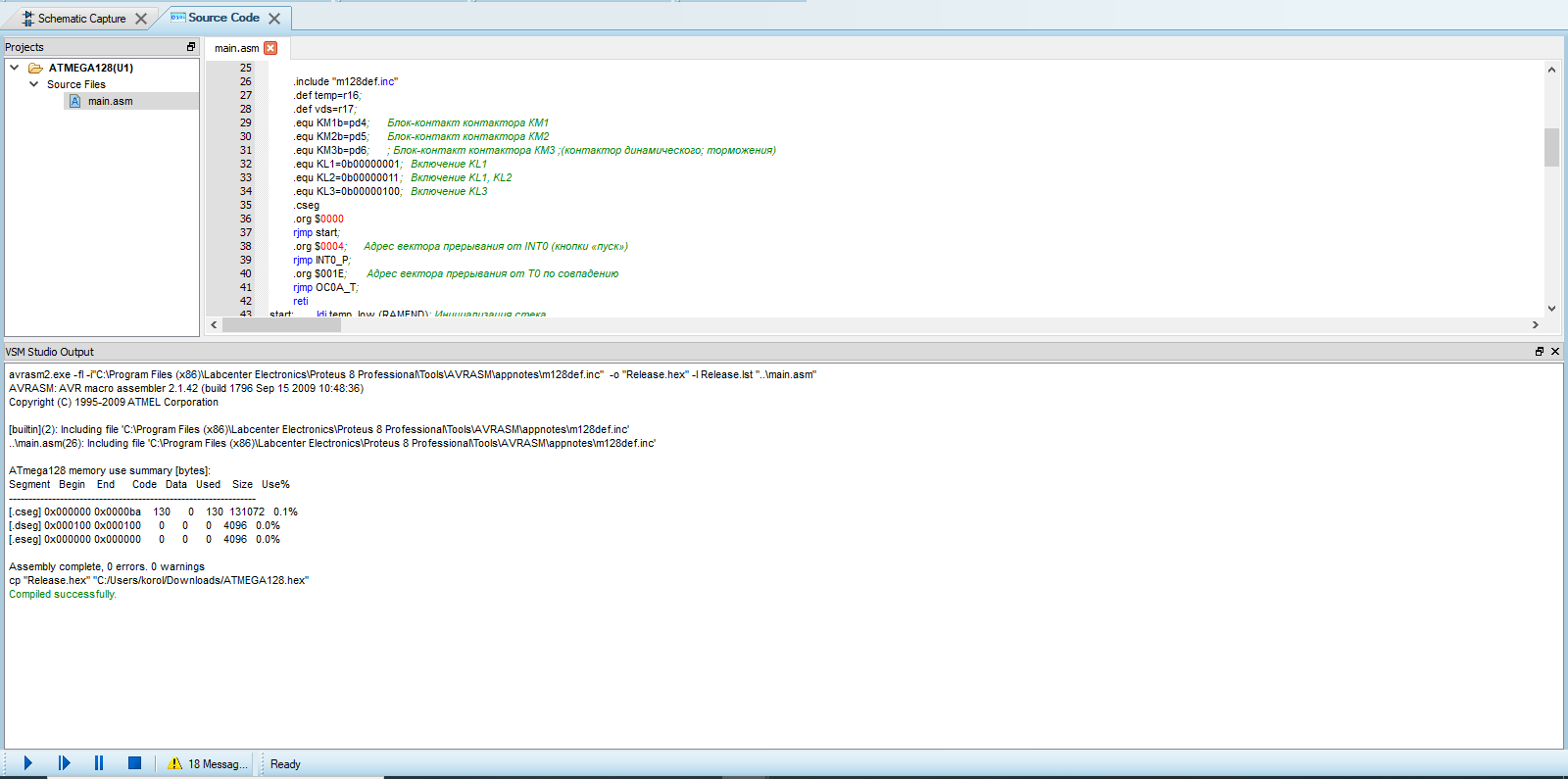

Таблица 3.9 – Программа для ATmega128 в Proteus V8.30 .include "m128def.inc" .def temp=r16; .def vds=r17; .equ KM1b=pd4; Блок-контакт контактора КМ1 .equ KM2b=pd5; Блок-контакт контактора КМ2 .equ KM3b=pd6; ; Блок-контакт контактора КМ3 .equ KL1=0b00000001; Включение KL1 .equ KL2=0b00000011; Включение KL1, KL2 .equ KL3=0b00000100; Включение KL3 .cseg .org $0000 rjmp start; .org $0004; Адрес вектора прерывания от INT0 (кнопки «пуск») rjmp INT0_P; .org $001E; Адрес вектора прерывания от Т0 по совпадению rjmp OC0A_T; reti start: ldi temp, low (RAMEND); Инициализация стека out spl, temp; ldi temp, high (RAMEND); out sph, temp; ldi temp, $FF; Настройка портов B на вывод out DDRB, temp; out PORTD, temp; sts PORTF, temp; ldi temp, $00; Настройка портов D и F на ввод out DDRD, temp; sts DDRF, temp; ldi temp, 0b00001010; Настройка прерываний от внешних источников sts EICRA, temp; INT0 по спадающему фронту ldi temp, 0b00000011; Разрешить прерывание от внешних out EIMSK, temp; источников INT0 ldi temp, high(234); загрузка в регистр сравнения out OCR0, temp; Т0 числа, ldi temp, 0b0000010; Разрешить прерывание от Т0 по совпадению out TIMSK, temp; sei; Разрешить все прерывания M1: sbic PIND, KM1b; Проверка включения контактора КМ1 rjmp M1; ldi r19, KL2; ldi r20,30; Ввод количества циклов 30 M20: ldi temp, 0b0001111; Т0 в режиме СТС канал А CLK/1024 out TCCR0, temp; brne M20; Перейти на М20 если r20 ? 0 M2: sbic PIND, KM2b; Проверка включения контактора КМ2 rjmp M2; ldi temp,0; out TCCR0, temp; остановить таймер M3: sbic PIND, 1 ;Ожидание кнопки стоп rjmp M3 ldi temp, KL3 ;Включение KL3 out PORTB, temp; M4: sbic PIND, KM3b; Проверка включения контактора КМ3 rjmp M4 M7: ldi temp, 0b01100001; Настройка АЦП (выравнивание влево, out ADMUX, temp; вход PF1, Uоп=Uпит) ldi temp, 0b11000101; Запуск АЦП (kдел=32) out ADCSR, temp; M6: sbis ADCSR, ADIF; Проверка окончания работы АЦП rjmp M6; in vds, ADCH; Запись результата преобразования; АЦП с ДС в регистр данных cpi vds, $00; Сравнение с 0 brne M7; Если результат ? 0, то переход на М7 ldi temp, $00; Отключение всех промежуточных реле out PORTB, temp; M8: sbis PIND, KM3b; Проверка отключения КМ3 rjmp M8 rjmp M1 INT0_P: ldi temp, KL1; Включение КL1 out PORTB, temp; reti OC0A_T: cpi r20,0 brne M out portb, r19; Включение КL1, KL2 M: reti Рисунок 2.3 – Компиляция в программе Proteus V8.30  ЗаключениеВ проделанной работе мы согласно заданию, спроектировали микропроцессорную систему управления пуском в одну ступень в функции времени и динамического торможения в функции скорости асинхронного двигателя с фазным ротором на ATMega128L. Выдержка времени аппаратная реализуется с помощью встроенного таймера T0. Провели эмуляцию спроектированной микропроцессорной системы в программе Proteus V8.30 Разработана принципиальная схема микропроцессорной системы управления асинхронным двигателем с фазным ротором и написана программа, машинный код, который составляет 205 байт. 1 2 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||