Отчет к ЛБ 2. Панасюк, 955-об. Амурский государственный университет

Скачать 245.57 Kb. Скачать 245.57 Kb.

|

|

Министерство науки и высшего образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования АМУРСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ (ФГБОУ ВО «АмГУ») Факультет информатики и информатики Кафедра информационных и управляющих систем Направление подготовки 09.03.02 – Информационные системы и технологии Электротехника, электроника и схемотехника ЛАБОРАТОРНАЯ РАБОТА № 2«Изучение работы шифраторов, дешифраторов и мультиплексоров» Вариант 5 (Подгруппа 1) Исполнитель студент группы 955-об Д. В. Панасюк (подпись, дата) Проверил Д. А. Теличенко (подпись, дата) Благовещенск 2022 Цель работы: 1. Изучение принципов работы шифраторов, дешифраторов и мультиплексоров. 2. Реализация логических функций с помощью мультиплексоров. 3. Изучение способов применения дешифраторов. Приборы и элементы: Генератор слов (панель «Instruments/Word Generator»). Логический анализатор (панель «Instruments/Logic Analyzer»). Логические пробники (панель «Indicators/Red probe»). Источник напряжения + 5 В (панель «Basic/Pull-Up Resistor»). З емля (панель «Sources/Ground»). Двухвходовые элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ (панель «Logic Gates/ 2-Input AND, NAND, OR, NOR Gates»). Двухпозиционные переключатели (панель «Basic/Switch»). Дешифратор (панель «Digital/DEC/Generic 8-to-1 DEMUX»). Мультиплексор (панель «Digital/MUX/ Generic 1-of 8 MUX»). Задание 1. Исследование работы шифратора  Таблица истинности шифратора

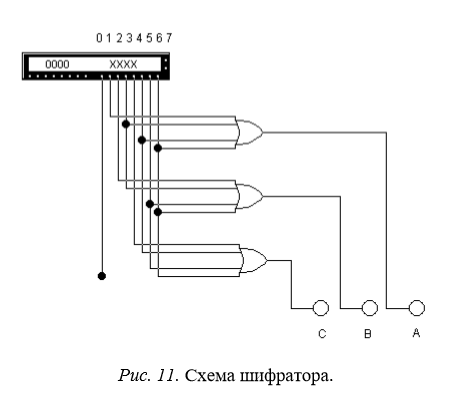

Вывод: Работа шифратора заключается в том, что, получая на входе число в десятичной системе счисления он преобразует его на выходе в двоичную систему счисления. Задание 2. Исследование работы дешифраторов 2.1. Исследование развернутой схемы дешифратора.  Таблица истинности развернутой схемы дешифратора

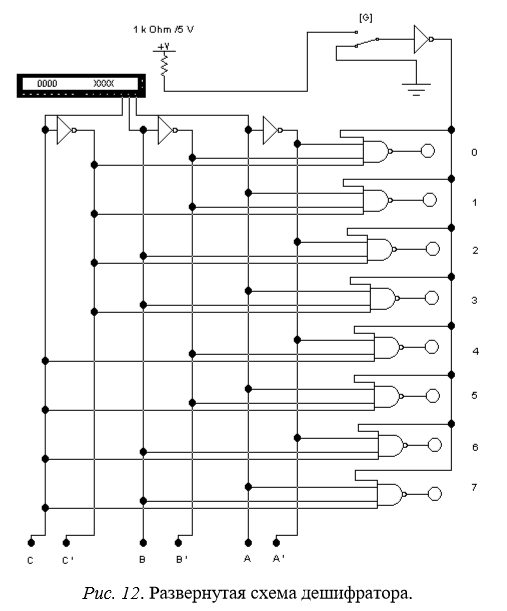

Вывод: Активный уровень сигнала представленной схемы — это уровень логического нуля, т.к разрешающий вход дешифратора – инверсный. 2.2. Исследование работы схемы дешифратора 3*8 в основном режиме.  Таблица истинности развернутой схемы дешифратора в основном режиме

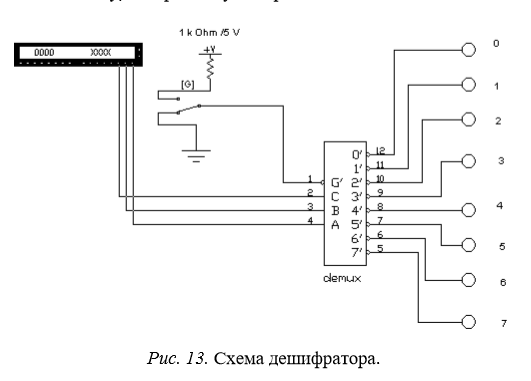

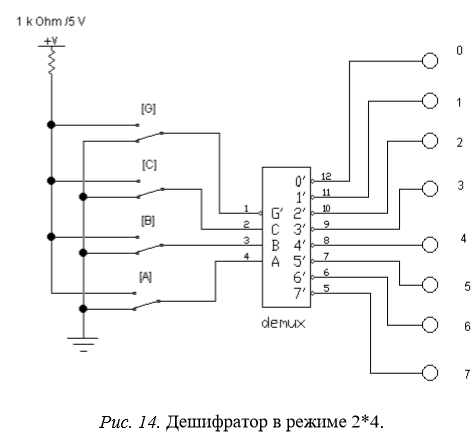

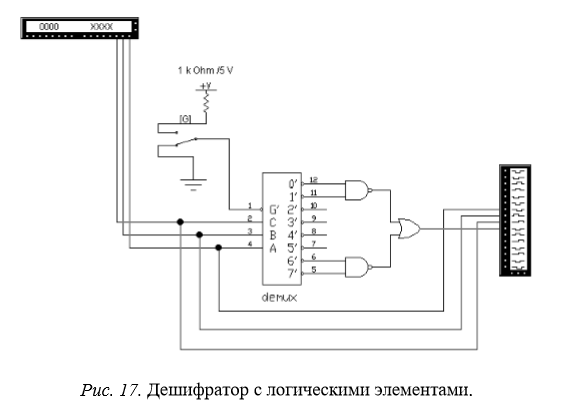

Вывод: разницы в таблицах и работе дешифратора не наблюдается 2.3. Исследование работы схемы дешифратора 3*8 в режиме2*4.  При С=0: На выходах 4, 5, 6, 7 уровень сигнала не менялся При С=1: На выходах 0, 1, 2, 3 уровень сигнала не менялся При B=1: На выходах 2, 3, 6, 7 уровень сигнала не менялся. Это можно объяснить тем, что входы A и С вместе с B образовывали на выходе числа 000,001,100,101, что в десятичной системе равно, соответственно, числам 0, 1, 4, 5. Вывод: Дешифратор можно использовать на меньшую разрешающую способность, если ставить старший разряд как 1 или как 0, исходя из активного уровня. Задание 3. Применение дешифраторов  Таблица истинности дешифратора с логическими эл-ми

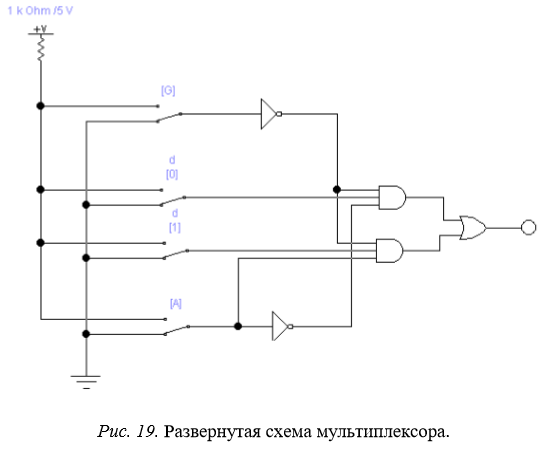

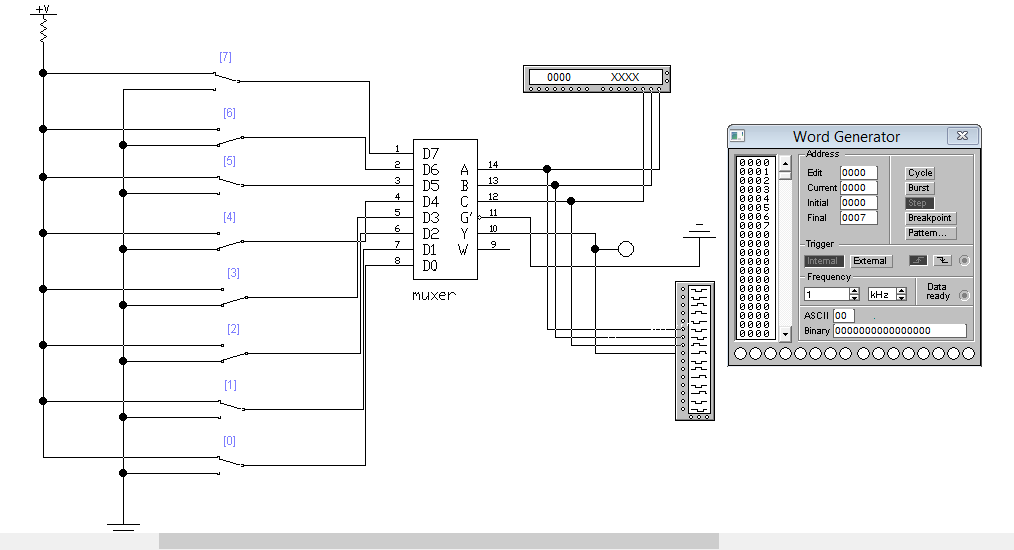

Функция в форме СДНФ:  BC+ABC BC+ABCЗадание 4. Исследование работы мультиплексора 4.1. Исследование развернутой схемы мультиплексора.  Развернутая схема мультиплексора

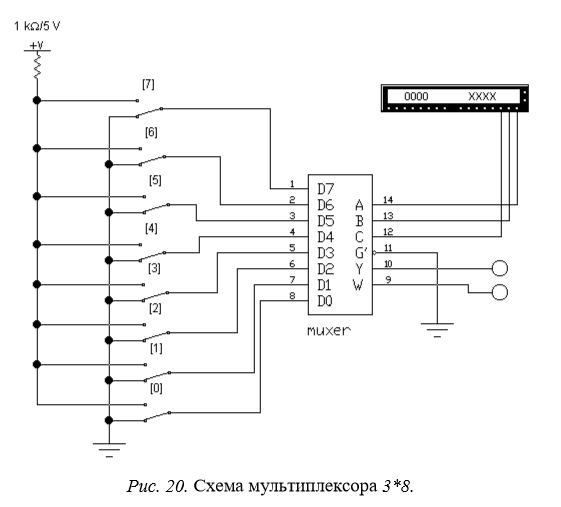

4.2. Исследование работы схемы мультиплексора 3*8 в основном режиме.  Таблица истинности мультиплексора

Задание 5. Реализация логической функции с помощью мультиплексора Таблица истинности для логической функции

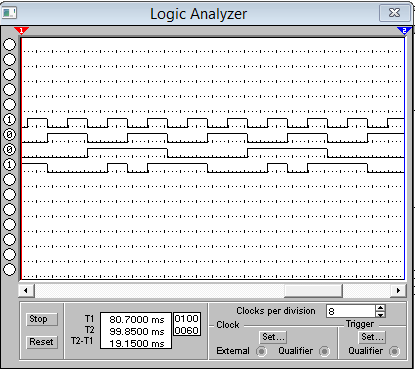

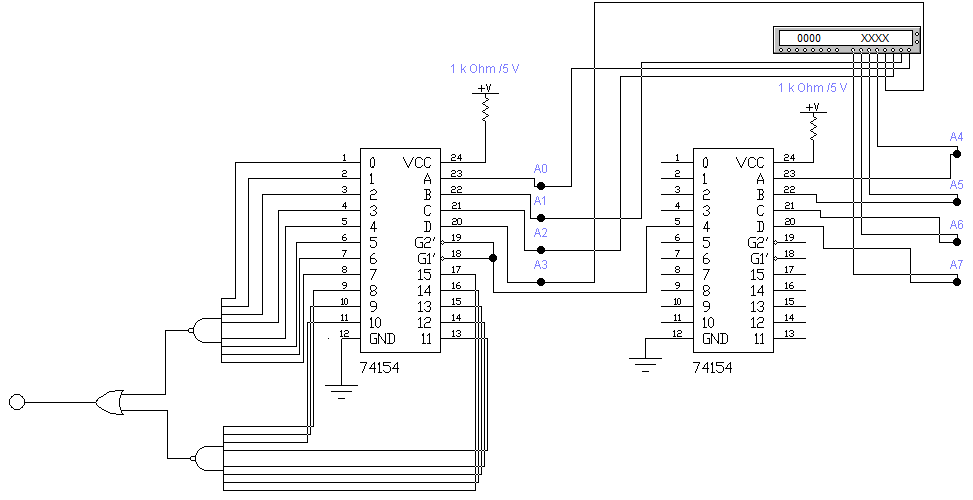

Полученные функции: Неупрощенная:  Упрощенная:  Построенная схема:  Временная диаграмма:  Вывод: Результаты совпадают. Упражнения 1. Применение дешифраторов Сформируйте сигнал выбора определенной микросхемы памяти в микроконтроллере с использованием стандартных дешифраторов. Адреса карты памяти для блока ОЗУ

Адреса в ячейках A7-A4 не меняются, а в ячейках A4-A0 происходит смена значений c 0000 до 1111. Адреса карты памяти

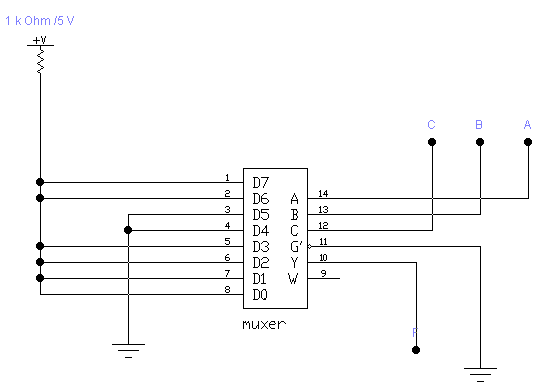

Полученная схема:  2. Применение мультиплексоров По заданной логической функции постройте схему с использованием мультиплексора. Функция: Таблица истинности для функции

Для реализации функции на мультиплексоре на входы с номерами 4, 5 подаем уровень логического нуля, а на остальные – уровень логической единицы. Полученная схема:  | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||