Архитектура информационных систем. Литература по теме Практические задания Тема Устройство персонального компьютера системный блок и периферия Вопросы для самопроверки Литература по теме

Скачать 5.96 Mb. Скачать 5.96 Mb.

|

|

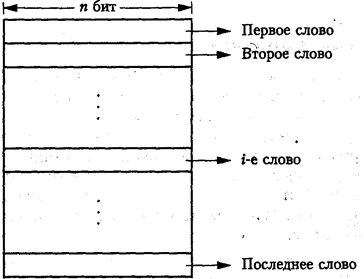

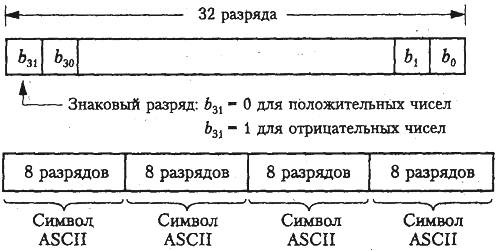

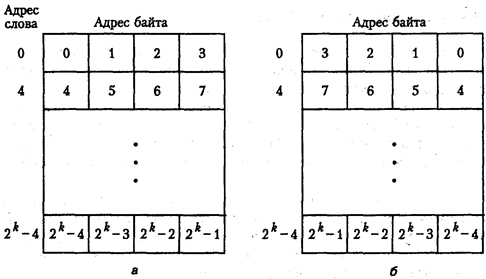

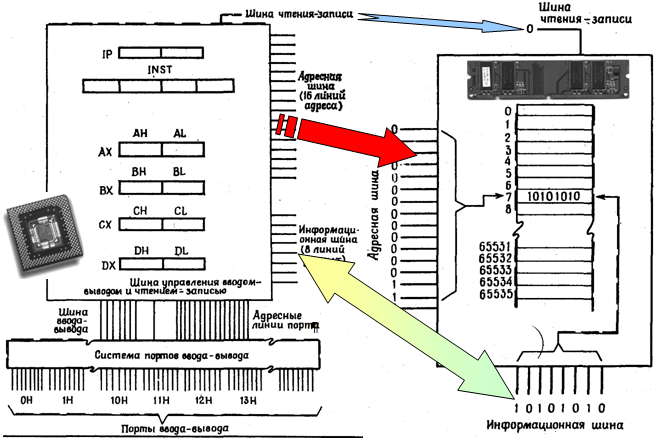

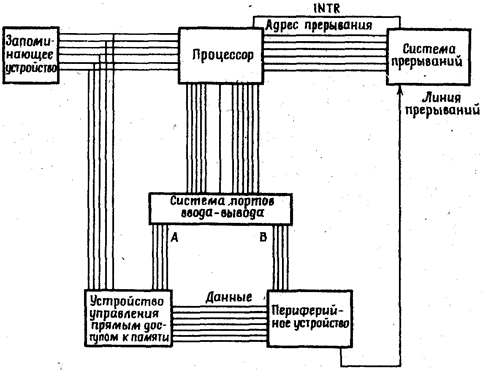

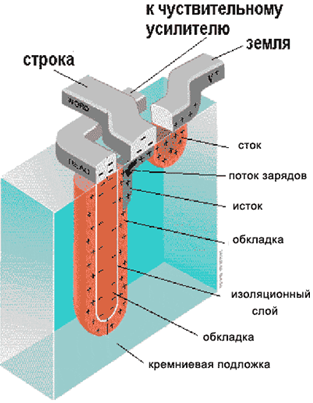

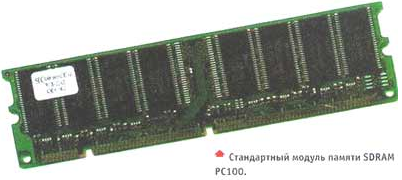

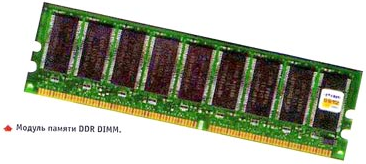

Тема 5. Типы и логическое устройство оперативной памяти. Цели и задачи: Цели и задачи изученияданной темы – получение сведений о назначении и устройстве оперативной памяти ПК, интерфейсах работы оперативной памяти (ОП) и технических параметров модулей ОП. В результате успешного изучения темы Вы: Узнаете: · логическое и техническое устройство ОП; · понятия синхронный и асинхронный интерфейсы доступа к ОП; · основные технические характеристики модулей ОП; · порядок адресации данных в ОП; · порядок доступа и операции с данными ОП; · понятие прямого доступа к ОП (DMA); · режимы работы микропроцессора при обращении к ОП. Приобретете следующие профессиональные компетенции: · умение определять технические параметры модуля ОП по его описанию из прайс-листа; · умение выбирать модули ОП исходя из решаемых задач; · умение выбирать наиболее подходящий тип ОП исходя из решаемых задач. В процессе освоения темы акцентируйте внимание на следующих ключевых понятиях: Время доступа к ОП - время обращения к ячейкам ОП (скорость чтения/записи данных непосредственно в ячейки ОП), измеряется в наносекундах. Регенерация – процесс постоянной перезаписи содержимого ячеек динамической ОП, вызванный саморазрядом конденсаторов. Синхронный и асинхронный интерфейс определяют синхронизирована (синхронный интерфейс) или нет (асинхронный интерфейс) работа оперативной памяти с работой процессора. В случае асинхронного интерфейса момент обращения процессора к станице ОП может не совпадать с моментом ее регенерации. Латентность - интегральный показатель, который характеризует продолжительность интервалов (таймингов) задержек в процессе выполнения операций чтения/записи (время на вычисление адреса страницы и собственно выполнение операции). Как правило, производители указывают данные первого тайминга«CAS Latency (CL)». Это приводит к тому, что в технической литературе часто возникает путаница между понятием «латентность» и «тайминги», т.к. ориентируясь на данные, указанные производителем, летентностью иногда называют только значение первого тайминга. Тайминги - временные задержки сигнала при обработке данных в ОП. Значения таймингов обычно имеют вид комбинации четырех чисел, например, 3-3-3-9 или 4-4-4-12. По порядку это: · CAS Latency (CL) - задержка между отправкой в память адреса столбца и началом передачи данных. Время, требуемое на чтение первого бита из памяти, когда нужная строка уже открыта. · RAS to CAS Delay (tRCD) - число тактов между открытием строки и доступом к столбцам в ней. Время, требуемое на чтение первого бита из памяти без активной строки. · RAS Precharge Time (tRP) - Число тактов между командой на предварительный заряд банка (закрытие строки) и открытием следующей строки. Время, требуемое на чтение первого бита из памяти, когда активна другая строка либо время между командой закрытия и повторной активацией то же строки. · Active to Precharge (tRas) - число тактов между командой на открытие банка и командой на предварительный заряд. Время на обновление строки. Теоретический материал по теме Оперативная память (ОП) или оперативное запоминающее устройство (ОЗУ) - специальная внутренняя память ЭВМ, позволяющая быстро записывать в нее и считывать из нее необходимую информацию. Однако информация в этой памяти хранится лишь до отключения питания компьютера, поэтому ее иногда называют энергозависимой, временной памятью или по-английски «RAM» (Random Access Memory - память произвольного доступа). Обычно в ПК используется DRAM (Dynamic Random Access Memory) - динамическая память. При этом во время работы компьютера информация может постоянно обновляться. В оперативной памяти находятся элементы текстов, числовые данные, программные код и другая информация, необходимая для выполняющихся в данный момент программ. В настоящее время достаточно широко используется кэш-память (Caсhe Memory). Она бывает внутренняя (встроенная, например, в процессор, размером от 128 Кб) и внешняя. Внешняя кэш-память - это сверхоперативная память, расположенная как буфер между процессором и ОЗУ и повышающая производительность ПК. Она служит для уменьшения количества тактов ожидания процессора при обращения к более медленной RAM и имеет размер от 64 Кб до 1 Мб. Оперативная память состоит из многих миллионов ячеек, в каждой из которых содержится один бит информации, имеющий значение 0 или 1. Биты обрабатывают группами фиксированного размера. Для этого память организуется таким образом, что группы по п бит могут записываться и считываться за одну базовую операцию. Группа из п бит называется словом информации, а значение п - длиной слова. Схематически память компьютера можно представить в виде набора слов (рис. 23).  Рис. 23. Схема оперативной памяти ПК Для доступа к памяти с целью записи или чтения отдельных элементов информации, будь то слова или байты, необходимы имена или адреса, определяющие их расположение в памяти. В качестве адресов традиционно используются числа из диапазона от 0 до 2k-1 со значением k, достаточным для адресации всей памяти компьютера. Все 2k адресов составляют адресное пространство компьютера. Следовательно, память состоит из 2k адресуемых элементов. Например, использование 24-разрядных (как в процессоре 80286) адресов позволяет адресовать 224 (16777216) элементов памяти. Обычно это количество адресуемых элементов обозначается как 16 М (16 мега), где 1М - 220 (1048576) (адресное пространство МП 8086 и 80186). 32-разрядным адресам (у процессоров 80386, 80486, Pentium и их аналогов) соответствует адресное пространство из 232, или 4 Гб, элементов, где 1 Г - 230 байт. Существует три основные единицы информации: бит, байт и слово. Байт всегда равен 8 битам, а длина слова обычно колеблется от 16 до 64 бит. Отдельные биты, как правило, не адресуются. В большинстве современных компьютеров адреса назначаются байтам памяти (памятью с байтовой адресацией). Последовательные байты имеют адреса 0, 1, 2 и т. д. Таким образом, при использовании слов длиной 32 бита последовательные слова имеют адреса 1,4,8,..., и каждое слово состоит из 4 байт. В одном 32-х битовом слове может храниться 32-разрядное число в дополнительном коде или четыре символа ASCII, занимающих по 8 бит (рис. 24).  Рис. 24. Схема хранения слов и кодов ASCII в ОП ASCII (American Standard Code for Information Interchange) - таблица для основных печатных символов и некоторых специальных кодов, используемых в ПК. Существует два способа адресации байтов в словах (рис. 25): a. в прямом порядке (little-endian) - байты адресуются справа налево, так что наименьший адрес имеет самый младший байт слова (расположенный с правого края); b. в обратном порядке (big-endian) - байты адресуются слева направо, так что самый старший байт слова (расположенный с левого края) имеет наименьший адрес.  Рис. 25. Прямая (а) и обратная (б) адресации байтов в словах Слова «старший» и «младший» определяют вес бита, то есть степень двойки, соответствующей данному биту, когда слово представляет число. В ПЭВМ на основе МП 80x86 используется прямой порядок, а в ПЭВМ на основе МП Motorola 68000 - обратный. В обеих этих системах адреса байтов 0,4, 8 и т. д. применяются в качестве адресов последовательных слов памяти в операциях чтения и записи слов. Наряду с порядком байтов в слове важно также определить порядок битов в байте. Наиболее естественный порядок битов для кодирования числовых данных (непосредственно соответствующий их разрядам) - «слева направо»: b32, ... ,b1,b0. Однако существуют компьютеры, для которых характерен обратный порядок битов. В случае 32-разрядных слов их естественные границы располагаются по адресам 0,4,8 и т. д. При этом мы говорим, что слова выровнены по адресам в памяти. Если говорить в общем, слова считаются выровненными в памяти в том случае, если адрес начала каждого слова кратен количеству байтов в нем. По практическим причинам, связанным с манипулированием двоично-кодированными адресами, количество байтов в слове обычно является степенью двойки. Поэтому, если длина слова равна 16 бит (2 байтам), выровненные слова начинаются по байтовым адресам 0, 2, 4, ... , а если она равна 64 бит (23 т.е. 8 байтам), то выровненные слова начинаются по байтовым адресам 0, 8, 16, ... . Не существует причины, по которой слова не могли бы начинаться с произвольных адресов. Такие слова называются невыровненными. Как правило, слова выравниваются по адресам памяти, но иногда этот принцип нарушатся. Доступ к числам, символам и символьным строкам. Обычно число занимает целое слово. Поэтому, для того чтобы обратиться к нему в памяти, нужно указать адрес слова, по которому оно, это число, хранится. Точно так же доступ к отдельно хранящемуся в памяти символу осуществляется по адресу его байта. Во многих приложениях необходимо обрабатывать строки символов переменной длины. Для доступа к такой строке нужно указать адрес байта, в котором хранится ее первый символ. Последовательные символы строки содержатся в последовательных байтах. Существует два способа определения длины строки. Первый из них заключается в использовании специального управляющего символа, обозначающего конец строки и являющегося ее последним символом. Второй способ состоит в использовании отдельного слова памяти или регистра процессора, содержащего число, которое определяет длину строки в байтах. Операции с памятью. И команды программ, и данные, являющиеся операндами этих команд, хранятся в памяти. Для выполнения команды управляющие схемы процессора должны инициировать пересылку содержащего ее слова или слов из памяти в процессор. Операнды и результаты также должны пересылаться между памятью и процессором. Таким образом, для выполнения команды программы необходимо произвести две операции с памятью: · Load (или Read, или Fetch), то есть загрузка (или чтение, или выборка соответственно). · Store (или Write), то есть сохранение (или запись). Операция загрузки пересылает в процессор копию содержимого памяти но заданному адресу. При этом содержимое памяти остается неизменным. Для того чтобы начать операцию загрузки, процессор отсылает в память адрес и запрашивает содержимое памяти по этому адресу. Из памяти считываются соответствующие данные и пересылаются в процессор. Операция сохранения пересылает элемент информации из процессора в память по заданному адресу, уничтожая предыдущие данные, хранившиеся по этому адресу. Для выполнения такой операции процессор отсылает в память данные и адрес, по которому они должны быть записаны. Информацию из одного слова или одного байта можно переслать между процессором и памятью за одну операцию. Процессор содержит небольшое количество регистров, вмещающих по одному слову. Эти регистры служат либо источниками, либо приемниками данных, пересылаемых в память и из памяти. Пересылаемый байт обычно располагается в младшей (крайней справа) позиции в регистре. Взаимодействие с памятью (рис. 26) происходит через: · шину чтения-записи; · адресную шину; · информационную шину.  Рис. 26. Взаимодействие процессора с ОП По шине чтения-записи сообщается тип производимой операции (считывание из памяти или запись в нее). Сигналы, подаваемые на адресную шину, определяют область памяти, из которой (в которую) ведется считывание (запись), а по информационной шине передается считанная (записанная) информация. Пример – считывание из памяти и запись в память байта с адресом 7. При считывании данных из памяти некоторая внешняя (по отношению к запоминающему устройству) система (например, микропроцессор) устанавливает на шине чтения-записи сигнал 1, сообщая таким образом, что должна производиться операция считывания. Кроме того, эта внешняя система помещает на адресную шину значение 0000000000000111 в двоичной системе счисления (или, что то же самое, 7 — в десятичной системе счисления). Тем самым запоминающему устройству сообщается, что требуется считать байт информации из ячейки 7. Очевидно, что в результате операции считывания содержимое указанного байта, равное 10101010, появится на информационной шине (см. рисунок). При записи на шине чтения-записи устанавливается сигнал 0 и на адресную и информационную шины помещаются адреса и записываемые данных. В качестве адреса запоминающее устройство получает число 0000000000000111, или, что то же самое, 7, а в качестве записываемых данных - число 10101010. Поскольку на шине чтения-записи установлен сигнал 0, данные с информационной шины заносятся в ячейку 7. Система прямого доступа к памяти. Как уже отмечалось, процессор способен считывать данные из некоторого устройства и записывать их в память. Подобные действия может выполнять и система прямого доступа к памяти DMA (Direct Memory Аccess) и таким образом освобождать процессор от этой работы. На рисунке 27 показано, каким образом процессор и система прямого доступа к памяти связаны с запоминающим устройством. Здесь же показано, что обе системы могут посылать и принимать данные из некоторого периферийного устройства. Для доступа к этому устройству процессор использует порт В, а система прямого доступа — шину, обозначенную словом «Данные». Наконец, процессор может вести обмен данными с системой прямого доступа к памяти через порт А.  Рис. 27. Схема прямого доступа к ОП Рассмотрим в качестве примера процесс считывания нескольких байтов данных из периферийного устройства и занесения их в память. Процесс начинается, когда процессор посылает одну команду в систему прямого доступа к памяти через порт А, а другую — в устройство через порт В. По команде, направленной в устройство, последнее должно переслать несколько байтов данных в систему прямого доступа к памяти. Согласно команде, посланной в систему прямого доступа, эта система должна принять байты данных из устройства и записать их в память. Во время выполнения описанных пересылок процессор может продолжать считывание и выполнение команд. Может возникнуть вопрос, каким образом система прямого доступа и процессор могут одновременно осуществлять доступ к памяти? На самом деле такой возможности нет. Запоминающее устройство в каждый момент времени обрабатывает только один запрос. Однако система прямого доступа к памяти достаточно «интеллектуальна» и в состоянии задержать запрос процессора, пока сама реализует обращение. Таким образом, процессор и система прямого доступа к памяти поочередно работают с запоминающим устройством, причем процессор время от времени находится в состоянии ожидания, пока освободится память. С запросами периферийного устройства на передачу данных затруднений обычно не возникает, так как они поступают существенно реже, чем запросы процессора. Система прямого доступа лишь иногда обращается к памяти, в то время как процессор постоянно требует доступа к запоминающему устройству. Поэтому создается впечатление, что и процессор, и система прямого доступа работают с памятью одновременно. Режимы процессора. Все 32-разрядные процессоры Intel и совместимые, начиная с 80386-го, могут выполнять программы в нескольких режимах. Режимы процессора предназначены для выполнения программ в различных средах; в разных режимах возможности микропроцессора неодинаковы, потому что команды выполняются по-разному. В зависимости от режима процессора изменяется схема управления памятью системы и задачами. Процессоры могут работать в трех режимах: · реальном; · защищенном; · виртуальном реальном режиме (реальном внутри защищенного). Реальный режим. В первоначальном IBM PC использовался процессор i8086, который мог выполнять 16-разрядные команды, применяя 16-разрядные внутренние регистры, и адресовать только 1 Мбайт (220 байт) памяти, используя 20 разрядов для адреса. Все программное обеспечение PC первоначально было предназначено для этого процессора; оно было разработано на основе 16-разрядной системы команд и модели памяти объемом 1 Мбайт. Например, DOS, все программное обеспечение DOS, Windows от 1.x до 3.x и все приложения для Windows от 1.x до 3.x написаны в расчете на 16-разрядные команды. Эти 16-разрядные операционные системы и приложения были разработаны для выполнения на процессоре i8086. Более поздние процессоры, например i80286, могли также выполнять те же самые 16-разрядные команды, что и первоначальный i8086, но намного быстрее. Другими словами, процессор i80286 был полностью совместим с первоначальным i8086 и мог выполнять все 16-разрядные программы точно так же, как i8086, но, конечно же, значительно быстрее. Шестнадцатиразрядный режим, в котором выполнялись команды процессоров i8086 и i80286, был назван реальным режимом. Все программы, выполняющиеся в реальном режиме, должны использовать только 16-разрядные команды, 20-разрядные адреса и поддерживаться архитектурой памяти, рассчитанной на емкость до 1 Мбайт. Для программного обеспечения этого типа обычно используется однозадачный режим, т.е. одновременно может выполняться только одна программа. Нет никакой встроенной защиты для предотвращения перезаписи ячеек памяти одной программы или даже операционной системы другой программой; это означает, что при выполнении нескольких программ вполне могут быть испорчены данные или код одной из них, а это может привести всю систему к краху (или останову). Защищенный режим. Несмотря на то что процессор i80286 как и i8086 является 16-разрядным, он (в отличие от последнего) может работать в новом – защищённом - режиме и имеет встроенную поддержку мультизадачных операционных систем, значительно ускоряющую и упрощающую процесс переключения задач. Эта поддержка активно используется всеми мультизадачными операционными системами и оболочками, разработанными для компьютера IBM PC. Адресная шина i80286 была увеличена с 20 до 24 разрядов, что привело к расширению адресного пространства с 1 до 16 Мб (224 байт). Новый метод адресации памяти позволил изолировать адресные пространства отдельных задач друг от друга. При этом прикладная программа, работающая в среде операционной системы, использующей защищённый режим, не может случайно или намеренно разрушить целостность самой операционной системы, она может записывать данные только в те области памяти, которые выделены ей операционной системой. Следующие модели процессоров фирмы Intel - i80386, i80486 и i80586 (Pentium) были 32-разрядными. Помимо расширения адресного пространства до величины в 4 Гбайта (232 байт) в них реализована концепция страничной виртуальной памяти, возможной только в защищённом режиме. Механизм страничной виртуальной памяти позволяет разместить часть оперативной памяти на диске. При этом размер оперативной памяти (виртуальной), предоставляемой программам, ограничен разве что лишь размером свободного пространства на диске. Виртуальный реальный режим. Помимо страничной виртуальной памяти в процессорах i80386 и более поздних реализован так называемый режим виртуального процессора i8086 или просто виртуальный режим. Этот режим реализуется в рамках защищённого режима (процессор может переключиться в виртуальный режим только из защищённого режима). В виртуальном режиме процессор способен выполнять программы, составленные для процессора i8086, находясь в защищённом режиме и используя аппаратные средства защищённого режима: мультизадачность, изолирование адресных пространств отдельных задач друг от друга, страничная виртуальная память. Устройство и принципы функционирования оперативной памяти. Ядро микросхемы динамической памяти (рис. 28) состоит из множества ячеек, каждая из которых хранит всего один бит информации. На физическом уровне ячейки объединяются в прямоугольную матрицу, горизонтальные линейки которой называются строками (ROW), а вертикальные - столбцами (Column) или страницами (Page).  Рис. 28. Физическое устройство ячейки динамической ОП Линейки представляют собой обыкновенные проводники, на пересечении которых находится «сердце» ячейки - несложное устройство, состоящее из одного транзистора и одного конденсатора. Конденсатору отводится роль непосредственного хранителя информации. Правда, хранит он очень немного - всего один бит. Отсутствие заряда на обкладках соответствует логическому нулю, а его наличие - логической единице. Транзистор же играет роль «ключа», удерживающего конденсатор от разряда. В спокойном состоянии транзистор закрыт, но, стоит подать на соответствующую строку матрицы электрический сигнал, как он откроется, соединяя обкладку конденсатора с соответствующим ей столбцом. Чувствительный усилитель (sense amp), подключенный к каждому из столбцов матрицы, реагируя на слабый поток электронов, устремившихся через открытые транзисторы с обкладок конденсаторов, считывает всю страницу целиком. Чтение/запись отдельно взятой ячейки невозможно, поскольку открытие одной строки приводит к открытию всех, подключенных к ней транзисторов, а, следовательно, - разряду закрепленных за этими транзисторами конденсаторов. Чтение ячейки деструктивно по своей природе, поскольку sense amp (чувствительный усилитель) разряжает конденсатор в процессе считывания его заряда. «Благодаря» этому динамическая память представляет собой память разового действия, поэтому во избежание потери информации считанную строку приходится тут же перезаписывать вновь. Кроме того, ввиду микроскопических размеров, а, следовательно, емкости конденсатора записанная на нем информация хранится крайне недолго, - буквально сотые, а то тысячные доли секунды. Причина тому - саморазряд конденсатора. Несмотря на использование высококачественных диэлектриков с огромным удельным сопротивлением, заряд стекает очень быстро, ведь количество электронов, накопленных конденсатором на обкладках, относительно невелико. Для борьбы с «забывчивостью» памяти прибегают к ее регенерации - периодическому считыванию ячеек с последующей перезаписью. В зависимости от конструктивных особенностей «регенератор» может находиться как в контроллере, так и в самой микросхеме памяти. Необходимость данной процедуры отпадает при использовании статической оперативной памяти – SRAM (Static Random Access Memory). Ее основное отличие состоит в том, что в качестве ячейки здесь выступает статический триггер, что исключает «стекание» заряда, и соответственно, необходимость регенерации такой памяти отпадает. Данный вид модулей оперативной памяти существенно дороже DRAM, при этом более высокая производительность SRAM по сравнению с DRAM не оказывает ощутимого эффекта на работу системы в целом по причине ограниченной пропускной способности системной шины. Использование SRAM в ПК целесообразно в случае критичности обеспечения низкого энергопотребления и небольшого объема хранимых данных. В связи с этим SRAM используется, как правило, в микроконтроллерах и в качестве кэш памяти. Физически микросхема памяти (не путать с модулями памяти) представляет собой прямоугольный кусок керамики, имеющий контактные ножки: линии адреса (служат для выбора адреса ячеек памяти) и линии данных (служат для чтения и для записи данных). Необходимый режим работы определяется состоянием специального вывода Write Enable (Разрешение Записи). Низкий уровень сигнала WE готовит микросхему к считыванию состояния линий данных и записи полученной информации в соответствующую ячейку, а высокий, наоборот, заставляет считать содержимое ячеек и «выплюнуть» их значения в линии данных. DIMM. Аббревиатура DIMM расшифровывается как Dual Inline Memory Module (Модуль памяти с двойным расположением выводов). В модуле DIMM имеется 168 контактов, которые расположены с двух сторон платы и разделены изолятором. Следует отметить, что разъем DIMM имеют много разновидностей DRAM. Поэтому для облегчения выбора нужного модуля пользователям на материнских платах разные типы DIMM имеют от одного до трех вырезов на модуле памяти. Они предотвращают от неправильного выбора и неправильной установки модулей памяти. SDRAM. Оперативная память персональных компьютеров сегодня, как и десять лет тому назад, строится на базе относительно недорогой динамической памяти - DRAM (Dynamic Random Access Memory). Аббревиатура SDRAM расшифровывается как Synchronic DRAM (динамическое ОЗУ с синхронным интерфейсом), это означает, что микросхемы памяти SDRAM (рис. 29) работают синхронно с контроллером, что гарантирует завершение цикла в строго заданный срок. Кроме того, номера строк и столбцов подаются одновременно, с таким расчетом, чтобы к приходу следующего тактового импульса сигналы уже успели стабилизироваться и были готовы к считыванию. Этим SDRAM отличается от FPM и EDO DRAM, работающих по асинхронному интерфейсу.  Рис. 29. Микросхема (модуль памяти) SDRAM С асинхронным интерфейсом процессор должен ожидать, пока DRAM закончит выполнение своих внутренних операций. Они обычно занимают 60 нс. В DRAM с синхронным управле нием происходит защелкивание информации от процессора под управлением системных часов. Триггеры запоминают адреса, сигналы управления и данных. Это позволяет процессору выполнять другие задачи. После определенного количества циклов данные становятся доступными, и процессор может их считывать. Таким образом, уменьшается время простоя процессора во время регенерации памяти. Другое преимущество синхронного интерфейса - это то, что системные часы задают временные границы, необходимые DRAM. Это, во-первых, уменьшает трафик по локальной шине (нет «лишних» сигналов), а во-вторых, позволяет упростить операции ввода-вывода (в операциях пересылки центральный процессор либо контроллер DMA уже не должен выделять полезную информацию среди служебных импульсов и битов четности). В-третьих, все операции ввода/вывода на локальной шине стали управляться одними и теми же синхроимпульсами, что само по себе хорошо. Так же, в SDRAM реализован усовершенствованный пакетный режим обмена. Контроллер может запросить как одну, так и несколько последовательных ячеек памяти, а при желании - всю строку целиком. Это стало возможным благодаря использованию полноразрядного адресного счетчика. Количество матриц (банков) памяти в SDRAM увеличено с одного до двух (а, в некоторых моделях, и четырех). Это позволяет обращаться к ячейкам одного банка параллельно с перезарядкой внутренних цепей другого, что вдвое увеличивает предельно допустимую тактовую частоту. Наконец, разрядность шины данных увеличилась с 32 до 64 бит, что еще вдвое увеличило ее производительность. SDRAM II или DDR SDRAM. Спецификация SDRAM II (рис. 30), иначе называемая DDR SDRAM, не имеет полной совместимости с SDRAM. Эта спецификация позволяет увеличить частоту SDRAM за счет работы на обеих границах тактового сигнала, то есть на подъеме и спаде. Однако SDRAM II использует тот же 168-ми контактный разъем DIMM.  Рис. 30. Микросхема (модуль памяти) SDRAM II В настоящее время используются различные модификации SDRAM II – DDR, DDR2 и DDR3 не совместимые между собой. Память от Rambus (RDRAM, RIMM). RDRAM представляет собой спецификацию, созданную и запатентованную фирмой Rambus, Inc. За счет использования обоих границ сигнала достигается частота работы памяти в 800 МГц. Модули RIMM (рис. 31) имеют размеры, сходные с геометрическими размерами SDRAM DIMM. В отличие от SDRAM DIMM, Direct Rambus может содержать любое целое число чипов Direct RDRAM (до максимально возможного).  Рис. 31. Модули памяти RIMM Один канал Direct Rambus максимум может поддерживать 32 чипа DRDRAM. На материнской плате может использоваться до трех RIMM модулей. Используются 64 Мбит, 128 Мбит и 256 Мбит устройства. Основных отличий от памяти предыдущих поколений всего три: · увеличение тактовой частоты за счет сокращения разрядности шины; · одновременная передача номеров строки и столба ячейки; · увеличение количества банков для усиления параллелизма. Чтобы расширить память сверх 32-х устройств, могут использоваться два чипа повторителя. С одним повторителем канал может поддерживать 64 устройства с 6-ю RIMM модулями, а с двумя - 128 устройств на 12 модулях. Несмотря на усилия компании Rambus Inc использование модулей RIMM не нашло поддержки у производителей материнских плат, поэтому активно обсуждается вопрос о закрытии проекта. Сравнительная характеристика основных типов памяти. Основными техническими характеристиками памяти являются: · тип памяти; · рабочая тактовая частота; · разрядность; · время доступа; · объем. В некоторых случаях производители указывают еще такой параметр как латентность. Это достаточно сложный интегральный показатель, который характеризует продолжительность интервалов задержек в процессе выполнения операций чтения/записи (время на вычисление адреса страницы и собственно выполнение операции). Такие задержки называются таймингами (от англ. time - время). В иделае – чем меньше тайминги, тем лучше, однако на практике вследствие конструктивных особенностей модулей оперативной памяти приходится искать компромисс между латентностью и тактовой частотой. В технической литературе и описаниях модулей оперативной памяти латентность указывается сокращением «CL» или «CAS Latency» от англ. column address strobe latency (дословно задержка импульса адресации столбца). Соответствующее число указывает комбинацию задержек, которая устанавливается по умолчанию (в общем случае, чем меньше – тем лучше), но может быть изменена пользователем, например через некоторые версии CMOS. Такую операции нужно проводить очень осторожно, поскольку, не зная правил формирования комбинаций можно вывести оперативную память из строя. Соответствующие параметры ОП приводятся в таблице 3. Таблица 3. Основные параметры модулей оперативной памяти  Итак, тип памяти определяется в соответствии с эволюцией ее развития и содержит информацию не только о быстродействии памяти, но и о типе разъема для ее установки (EDO просто не установится в разъем для DDR, что видно по рисункам). Рабочая тактовая частота характеризуют скорость обмена информацией с микропроцессором, а разрядность – количество бит информации, передаваемых за один такт. Время доступа (измеряемое в наносекундах) определяет время обращения к ячейкам памяти. И, наконец, объем памяти определяет ее ресурс по хранению информации. В настоящее время на компьютерном рынке представлены модули памяти от 256 до 4096 Мб. В качестве примера рассмотрим следующее описание по прайс-листу: Модуль памяти 1ГБ DDR3 SDRAM Kingston «ValueRAM» KVR1333D3N9/1G (PC10600, 1333МГц, CL9). Специфкация: 1. тип оперативной памяти: DDR3 SDRAM; 2. объем модуля оперативной памяти: 1ГБ; 3. эффективная тактовая частота оперативной памяти: 1333МГц; 4. максимальная скорость передачи данных (пропускная способность) 10600Мбит/c; 5. производитель: Kingston; 6. маркировка: «ValueRAM» KVR1333D3N9/1G; 7. латентность: CL9. Вопросы для самопроверки: 1. Для чего предназначена ОП? 2. Что значат сокращение DRAM, SRAM? 3. Как на физическом уровне устроена динамическая ОП? 4. В чем различие между синхронным и асинхронным интерфейсом ОП? 5. Каким образом происходит обращение к ячейкам ОП? 6. Что обозначают сокращения DIPP, SIPP, SIMM, EDO RAM, DIMM, SD RAM, DDR SD RAM, RIMM? 7. Какие технические характеристики ОП вы знаете? 8. Перечислите режимы, в которых могут работать процессоры класса 80x86. Напишите небольшое эссе (объемом в 2-3 страницы) по одному из перечисленных ниже вопросов: 1. Перспективы развития ОП. 2. Основные направления увеличения производительности ОП. 3. Сравнительный анализ статической и динамической ОП. 4. Сравнительный анализ методик определения латентности ОП. 5. Конструктивные особенности ОП Rambus. 6. Сравнительный анализ модулей памяти DDR2 и DDR3. 7. Память для видеокарт (видеопамять, графическая память). 8. Требования различных операционных систем к объему ОП. 9. Таблица кодов ASCII (назначение, управляющие символы, представление в ЭВМ). Литература по теме: Основная литература: 1. Аппаратное обеспечение вычислительных систем / Д.В. Денисов, В.А. Артюхин, М. Ф. Седненков; под ред. Д.В. Денисова. – М.: Маркет ДС, 2010 – 184 с. (Университетская серия.). Дополнительная литература: 1. Вычислительная техника: учеб. пособие. – М.: ФОРУМ: ИНФРА-М, 2007. – 608 с.: ил. – (Профессиональное образование). Глава 3, п. 3.7 (стр. 272-277). 2. Архитектура ЭВМ и вычислительных систем: учебник. – М.: ФОРУМ, 2008. – 512 с.: ил. – (Профессиональное образование). Глава 4, п. 4.5 (стр. 447-456). 3. Как выбрать оперативную память? // http://compmasterspb.ru/articles_text.php?id=23. Видеоролики: 1. Оперативная память // http://video.mail.ru/mail/bor-volodya/293/47.html. 2. Оперативная память // http://www.youtube.com/watch?v=rX1bHT6o4UU. Практические задания: Задание 1. Выберете модуль ОП для следующей материнской платы: Материнская плата Intel, Socket 478, D865GLCL «La Crosse» (Intel 865G/ICH5) Hyper-Threading, FSB/800МГц, 4xDDR/400МГц, AGP8x(1.5v), 3xPCI, Видео (Intel Extreme Graphics 2), Звук 5.1, Сеть 10/100Мбит/с (Intel), 8xUSBv2.0, 2xSATA/150, 2xATA/100, mATX. a) Модуль памяти DDR 256Мб, PC2100/266МГц Kingmax. b) Модуль памяти RIMM 256Мб, PC3200/800МГц Samsung (SEC-1). c) Модуль памяти DDR 256Мб, PC3200/400МГц Kingston. d) Модуль памяти DIMM 256Мб, PC133/133МГц JetRAM. Задание 2. Выберете модуль ОП для следующей материнской платы: Socket 1156 GIGABYTE «GA-H55M-D2H» (iH55, 2xDDR3, SATA II, U133, 2xPCI-E, D-Sub, DVI, HDMI, SB, 1Гбит LAN, USB2.0, mATX). a) Модуль памяти 512МБ DDR SDRAM Patriot (PC3200, 400МГц). b) Модуль памяти 2ГБ DDR3 SDRAM Kingston «Hyper X» KHX1600C9AD3B1/2G (PC12800, 1600МГц, CL9). c) Модуль памяти 2ГБ DDR2 SDRAM Kingston «ValueRAM» KVR800D2N6/2G (PC6400, 800МГц, CL6). d) Модуль памяти 1ГБ DDR3 SDRAM Silicon Power «SP001GBLTU133S02» (PC10600, 1333МГц, CL9). Задание 3. Дано описание ОП по прайс-листу: Модуль памяти 1ГБ DDR2 SDRAM Silicon Power «SP001GBLRU800S02» (PC6400, 800МГц, CL5). Проведите описание технических параметров (спецификации) данной ОП аналогично примеру в конце темы. Задание 4. Дано описание модуля ОП по прайс-листу: Модуль памяти DDR2 512Мб PC5300/667МГц Kingmax. Проведите описание технических параметров (спецификации) данного модуля ЛП аналогично примеру в конце темы. |