КСлаб1э. Методичні вказівки до виконання лабораторних робіт з дисциплін "схемотехніка еом" "компютерна схемотехніка"

Скачать 3.98 Mb. Скачать 3.98 Mb.

|

|

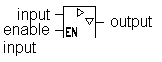

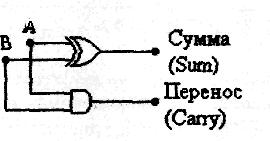

Установку типа буфера можно произвести с помощью команды Model в меню Circuit (CTRL+M). При использовании ТТЛ элемента в качестве буфера необходимо выбрать модель буфера LS-BUF или LS-OC-BUF (OpenCollector – открытый коллектор). Если в качестве буфера применяется КМОП элемент, следует выбрать модель Н- BUF, либо HC-OD-BUF (OpenDrain -открытый сток). Если тип буфера не выбран, то буфер ведет себя как обычный цифровой элемент с малой нагрузочной способностью.  Буфер с тремя состояниями Буфер с тремя состояниямиБуфер с тремя состояниями имеет дополнительный разрешающий вход (enable input). Если на разрешающем входе высокий потенциал, то элемент функционирует по таблице истинности обыкновенного буфера, если низкий, то независимо от сигнала на входе выход перейдет в состояние с высоким импедансом. В этом состоянии буфер не пропускает сигналы, поступающие на вход. Установка режима работы, производится так же, как и для обычного буфера. Узлы комбинационного типа Полусумматор ПолусумматорПолусумматор производит сложение двух одноразрядных двоичных чисел. Он имеет два входа слагаемых: А, В и два выхода: суммы (Sum) и переноса (Carry). Суммирование производится элементом Исключающее ИЛИ, а перенос – элементом И. Эквивалентная схема:  Таблица функционирования

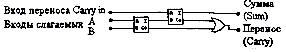

Выражения Булевой алгебры: Сумма = А В Перенос = А • В. П  олный двоичный сумматор олный двоичный сумматорПолный двоичный сумматор производит сложение трех одноразрядных двоичных чисел. Результатом является двухразрядное двоичное число, младший разряд которого назван суммой, старший разряд – переносом. Устройство имеет три входа и два выхода. Входы: слагаемых – А, В и переноса - CarryIN. Выходы: суммы – Sum и переноса – СаггуOUT.. Полный двоичный сумматор можно реализовать на двух полусумматорах и одном элементе ИЛИ.

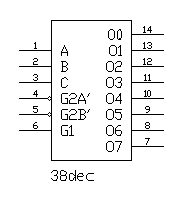

Д  ешифратор из 3 в 8 ешифратор из 3 в 8Дешифратор — логическое устройство, имеющее n входов и 2n выходов. Каждой комбинации входного кода соответствует активный уровень на одном из 2n выходов. Данный дешифратор имеет три входа адреса (А, В, С), два разрешающих входа (Gl, G2) и 8 выходов (YO...Y7). Номер выхода, имеющего активное состояние, равен числу N, определяемому состоянием адресных входов: N = 22С + 21В + 20А. Активным уровнем является уровень логического нуля. Дешифратор работает, если на входе G1 высокий потенциал, а на G2 – низкий. В других случаях все выходы пассивны, то есть имеют уровень логической 1. Таблица функционирования

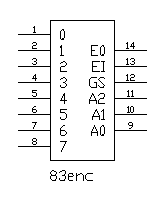

П  риоритетный шифратор риоритетный шифраторШифратор выполняет операцию, обратную дешифратору. Строго говоря, только один из входов шифратора должен иметь активный уровень. Данный шифратор при наличии на нескольких входах активного состояния активным считает вход со старшим номером. Кроме того, выход дешифратора инверсный, то есть значения разрядов двоичного числа на выходе инвертированы. Если хотя бы один из входов шифратора в активном состоянии, выход GS также будет в активном состоянии, а выход ЕО – в пассивном и наоборот. При пассивном состоянии разрешающего входа Е1 выходы GS также будут пассивными. Активным уровнем, так же, как и у дешифратора, является уровень логического нуля. Таблица функционирования

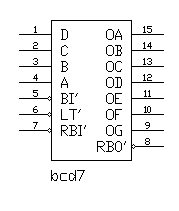

С  емисегментный дешифратор емисегментный дешифраторДанное устройство предназначено для управления семисегментным индикатором. Четырехразрядное двоичное число на входе определяет комбинацию логических уровней на выходе дешифратора таким образом, что при подключении к нему семисегментного индикатора на его дисплее отображается символ, соответствующий числу на входе. Для тестирования выходов дешифратора используется вывод LT (lamp testing). Когда на этот вход подан уровень логического 0, на всех выходах — логическая 1. Все выходы дешифратора устанавливаются в 0 при подаче на вход BI логического 0. Декодирующий семисегментный индикатор имеет встроенное декодирующее устройство, поэтому при работе с ним не надо использовать данный дешифратор. Таблица функционирования

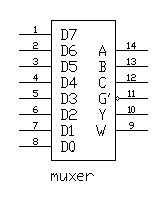

М  ультиплексор из 8 в 1 ультиплексор из 8 в 1Мультиплексор (селектор данных) осуществляет операцию передачи сигнала с выбранного входа на выход. Номер входа равен адресу — двоичному числу, определяемому состоянием адресных входов. Данный мультиплексор имеет 12 входов: восемь из которых – входы данных (DO – D7), три – входы адреса (А, В, С) и один – разрешающий вход (EN). Мультиплексор работает при подаче на вход разрешения логического 0. Выход W является дополнением выхода Y. (W=Y') Таблица функционирования

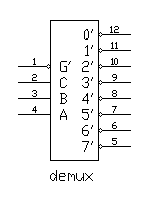

Д  емультиплексор емультиплексорДемультиплексор выполняет операцию, обратную мультиплексору. Он передает данные со входа на тот вывод, номер которого равен адресу. Данное устройство имеет 4 входа и 8 выходов. Входы адреса: А, В, С. Вход данных – G. Если на входе G логическая 1, то на всех выходах – также логическая 1. Таблица функционирования

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||