Контрольная по ТОЭ. Заказ_202275. 1. Общая характеристика и описание компонентов 4 Микропроцессорный модуль 4

Скачать 0.67 Mb. Скачать 0.67 Mb.

|

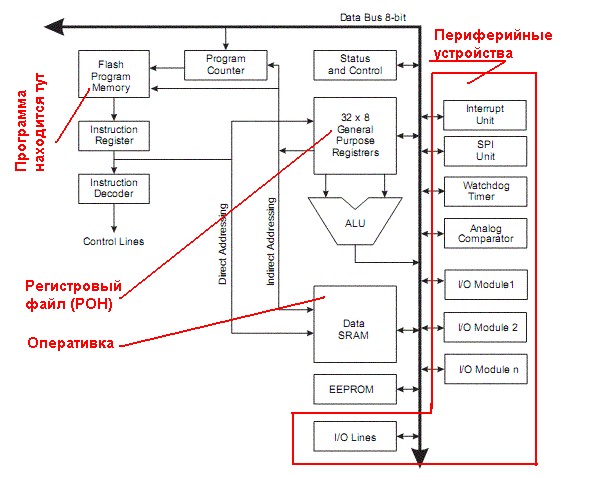

Технические характеристики FLASH-память программ объемом 16 Кбайт (число циклов стирания/записи не менее 10 000); оперативная память (статическое ОЗУ) объемом 1 Кбайт; память данных на основе ЭСППЗУ (EEPROM) объемом 256 байт (число циклов стирания/записи не менее 100 000); возможность защиты от чтения и модификации памяти программ и данных; возможность программирования непосредственно в системе через последовательные интерфейсы SPI и JTAG; возможность самопрограммирования; разнообразные способы синхронизации: встроенный RCгенератор с внутренней или внешней времязадающей RС-цепочкой, встроенный генератор с внешним кварцевым или пьезокерамическим резонатором, внешний сигнал синхронизации; наличие нескольких режимов пониженного энергопотребления; наличие детектора пониженного напряжения питания (Brown-Out Detector—BOD); полностью статическая архитектура, минимальная тактовая частота равна нулю; арифметико-логическое устройство (АЛУ) подключено непосредственно к регистрам общего назначения (32 регистра); большинство команд выполняются за один период тактового сигнала; векторная система прерываний, поддержка очереди прерываний; наличие аппаратного умножителя. программное конфигурирование и выбор портов ввода/вывода; выводы могут быть запрограммированы как входные или как выходные независимо друг от друга; входные буферы с триггером Шмитта на всех выводах; на всех входах имеются индивидуально отключаемые внутренние подтягивающие резисторы сопротивлением 20-50 кОм. Периферийные устройства два 8-битных таймера/счетчика. Один из них может работать в качестве часов реального времени (в асинхронном режиме); один 16-битный таймер/счетчик; сторожевой таймер; четыре канала ШИМ - сигнала. Разрешение формируемого сигнала может составлять от 1 до 16 бит; аналоговый компаратор; 8 - канальный 10-битный АЦП последовательного приближения, имеющий как несимметричные, так и дифференциальные входы; последовательный синхронный интерфейс SPI; последовательный двухпроводный интерфейс TWI (полный аналог интерфейса I2С); полнодуплексный универсальный синхронный/асинхронный приемо-передатчик (USART). Архитектура микроконтроллера ATmega16 На рисунке 1.1 приведена упрощенная схема архитектуры микроконтроллера ATmega16. Включающая, все основные модули, а также меж модульные связи.  Рисунок 1.1. Архитектура микроконтроллера ATmega16 1.2. Flash память Таблица 1.2 – Основные характеристики Microchip AT25F2048

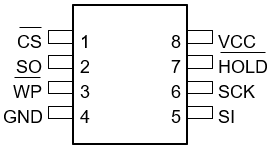

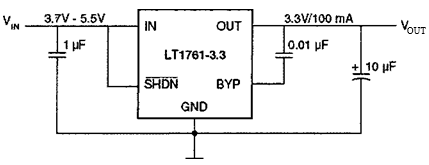

Рисунок 1.2. УГО микросхемы ATF25F2048 Описание микросхемы ATF25F2048 [2] Схема питания микросхемы Flash-памяти AT25F2048 представлена на рис. 1.2.  Рисунок 1.2. Схема питания микросхемы AT25F2048 Таблица 1.3. Инструкции управления Flash-памятью

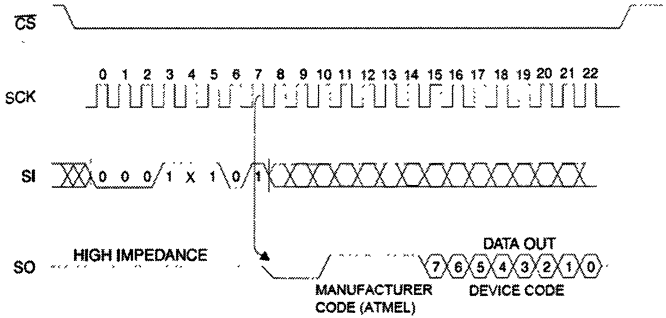

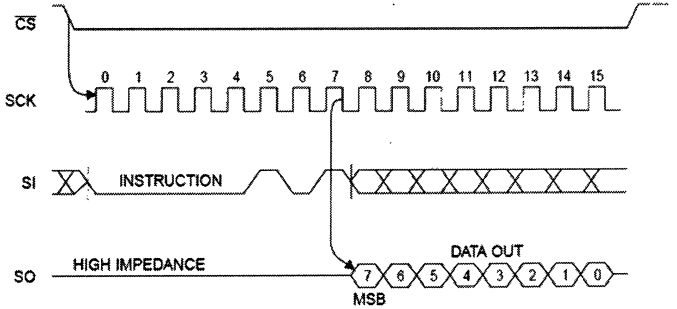

Инструкция rdid – “Получение кода изготовителя и идентификационного номера устройства” Последовательность выполнения инструкции RDID иллюстрирует рис.1.3. 1. На вывод /CS памяти подать 0 В. 2. Передать инструкцию 0001 Х101. 3. Принять байт данных (код изготовителя). 4. Принять байт данных (номер устройства). 5. На вывод /CS памяти подать +5 В.  Рисунок 1.3. Последовательность выполнения инструкции RFID Инструкция rdsr – “Чтение регистра состояния памяти” Последовательность выполнения инструкции RDSR иллюстрирует рис.1.4.  Рис.1.4. Последовательность выполнения инструкции rdsr 1. На вывод /CS памяти подать 0 В. 2. Передать инструкцию 0000 Х101. 3. Принять байт данных (регистр состояния). 4. На вывод /CS памяти подать +5 В. Регистр состояния Flash-памяти AT25F2048 показан в табл.1.4. Таблица 1.4. Регистр состояния Flash-памяти AT25F2048

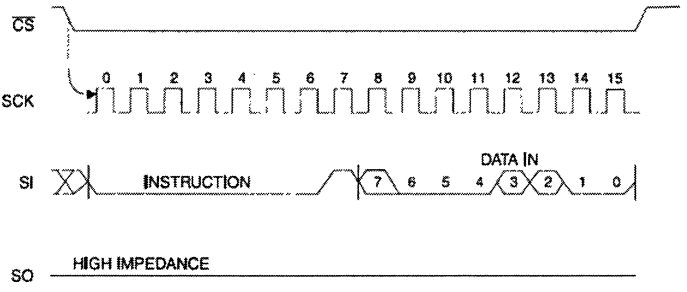

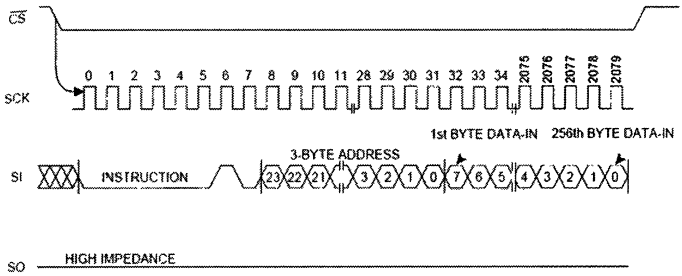

Назначение разрядов регистра состояния: /RDY: 0 — устройство готово; 1 — происходит цикл записи; WEN: 0 — включено разрешение записи; 1 — разрешение записи отключено; ВР0:ВР1 — определяют, какие сектора памяти будут защищены от записи; WPEN — разрешает/запрещает запись независимо от состояния вывода AVP. Аппаратная зашита от записи включена, когда вывод /WP находится в состоянии лог. 0 и WPEN = 1. Аппаратная зашита от записи отключена, когда вывод AVP находится в состоянии лог. 1 или WPEN = 0. Функция вывода ЛУР блокирована, когда WPEN = 0, и активна, когда WPEN = 1. Инструкция wrsr — “Программирование регистра состояния памяти” Последовательность выполнения инструкции WRSR иллюстрирует рис. 1.5.  Рисунок 1.5. Последовательность выполнения инструкции wrsr 1. На вывод /CS памяти подать 0 В. 2. Передать инструкцию 0000 Х001. 3. Передать байт данных (регистр состояния). 4. На вывод /CS памяти подать +5 В. Инструкция program— “Запись данных в массив памяти” Последовательность выполнения инструкции WRSR иллюстрирует рис.1.6.  Рис. 1.6. Последовательность выполнения инструкции program Перед программированием памяти необходимо выполнить инст- рукцию WREN (разрешить запись). После программирования разрешение записи автоматически сбросится. 1. На вывод /CS памяти подать 0 В. 2. Передать инструкцию 0000 Х010. 3. Принять три байта, указывающие с какого адреса начинать запись. 4. Передать 256 байт данных. 5. На вывод /CS памяти подать +5 В. Одна инструкция записи не может записать больше 256 байт за раз. Если размер записываемых данных меньше 256 байт, то все остальные данные останутся неизмененными. Если в процессе записи достигнут конец страницы (256 байт), то программирование продолжится с перво- го байта текущей страницы. Один и тот же байт не может быть перезаписан без стирания всего сектора. В микросхеме AT25F2048 всего четыре сектора: 1 — адреса 000000..00FFFF (от 0 до 65 535 байт); 2 — адреса 010000..01FFFF (от 65 536 до 131 071 байт); 3 — адреса 020000..02FFFF (от 131 072 до 196 607 байт); 4 — адреса 030000..03FFFF (от 196 608 до 262 143 байт). |