1. Поколения вычислительных машин. 5

Скачать 2.93 Mb. Скачать 2.93 Mb.

|

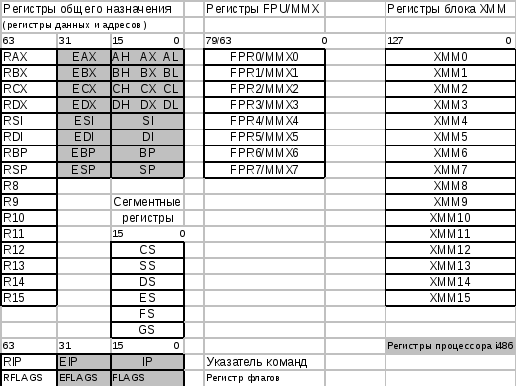

9.Регистры процессора и его программная модель.Общие понятия Разрядность адреса определяет, сколько бит (16, 32 или 64) используется в регистрах формирующих адрес данных или команд (инструкций), расположенных в памяти. Разрядность данныхопределяет, сколько бит содержится в командах, оперирующих словами. Каждому режиму работы процессора соответствует своя разрядность, применяемая по умолчанию. При необходимости для каждой исполняемой команды разрядность адреса или/и операнда может изменяться с помощью специальныхпрефиксов(байтов перед кодом операции КОП). 32-битные регистры позволяют непосредственно адресовать до 4 Гбайт памяти, что в свое время было более чем достаточно. Сейчас существует несколько механизмов расширения (х86-64 или ЕМ64Т), которые позволяют радикально увеличить объем адресуемой памяти: 64-битные регистры позволяют адресовать до 264 = 18,4 х 1018байт, но пока используют только младшие 48 бит адреса. Процессоры могут работать в различных режимах, определяющих возможности адресации памяти и защиты. Режим работы задается операционной системой с учетом работы приложений. Режимы работы процессоров: Режим реальной адресации, или простореальный режим полностью совместим с 8086. В этом режиме возможна адресация до 1 Мбайт физической памяти. Защищенный режим. Это основной режим работы, в этом режиме процессор включает механизмы сегментации и страничной трансляции. Это позволяет поддерживать виртуальную память объемом до 64 Тбайт. В защищенном режиме процессор может выполнять дополнительные команды, недоступные в реальном режиме. Мультипрограммный режим (многозадачность) это такой способ организации работы процессора, при котором в его памяти одновременно содержатся программы и данные для выполнения нескольких процессов обработки данных. При этом обеспечивается взаимная защита программ и данных. 64 – битный режим – это режим полной поддержки 64-битной виртуальной адресации и 64-битных расширений регистров. Режим совместимости позволяет 64-битным ОС работать с 32 и 16-битными приложениями. Операнды команд могут находиться в регистрах процессора,ячейках памяти(или в портах ввода/вывода), а такжев самой команде(непосредственный операнд). Наиболее эффективно процессор работает с операндами, расположенными в его регистрах. Регистры процессора Программная модельвключает восемь регистров общего назначения, шесть регистров сегментов, указатель команд, регистр системных флагов, регистры системных адресов, четыре регистра управления и шесть регистров отладки.  Рис.9.1 Пользовательские регистры процессоров х86 Для обращений к памяти у процессоров х86 используются 16-битные сегментные регистры, с помощью которых формируется логический адрес: CS(CodeSegment) – для адресации команд; SS(StackSegment) – для работы со стеком; DS,ES,GS– для обращений к данным. Обратите внимание, названия 32-битных регистров начинаются с буквы E, 64-битных – с буквыR. БлокиFPU,MMX,XMMв архитектуре процессора х86 держатся особняком. Они присутствуют не во всех процессорах и являются пристройкой. Эти блоки предназначены для ускорения вычислений с данными различных форматов. Восемь регистров общего назначения (РОН) имеют длину в 32 бит и содержат адреса или данные. Они поддерживают операнды-данные длиной 1, 8, 16, 32 и (при использовании двух регистров) 64 бит; битовые поля от 1 до 32 бит; операнды-адреса длиной 16 и 32 бит. Эти регистры называются EAX, EBX, ECX, EDX, ESI, EDI, EBP, ESP. Доступ к младшим 16 бит этих регистров выполняется независимо при использовании соответствующих имен 16-битных регистров: AX, BX, CX, DX, SI, DI, BP и SP. Также могут использоваться индивидуально младший (биты 0-7) и старший (биты 8-15) байты регистров AX, BX, CX, DX. Им соответствуют обозначения AH, DH, CH, BH и AL, DL, CL, BL. Хотя регистр ESP тоже относится к регистрам общего назначения, он содержит указатель на вершину стека и не используется для других целей. Следует отметить, что регистры могут быть неравнозначны и при использовании определенных инструкций могут иметь и иногда имеют специальное назначение: EAX - аккумулятор, операнд-источник или приемник результата (некоторые инструкции могут быть короче на один байт при использовании EAX); EBX - указатель на данные в сегменте DS; ECX - счетчик для цепочечных (например, MOVS) и циклических (с префиксом REP) инструкций; EDX - адрес порта ввода-вывода для инструкций IN/INS, OUT/OUTS; ESI - указатель на операнд-источник в сегменте DS для цепочечных инструкций; EDI - указатель на операнд-приемник в сегменте ES для цепочечных инструкций; EBP - указатель на данные в сегменте SS. МП включает шесть непосредственно доступных 16-битных регистров сегментов. С каждым сегментным регистром ассоциирован программно-недоступный кэш дескриптора соответствующего сегмента, содержащий базовый адрес сегмента в линейном адресном пространстве, предел сегмента и атрибуты сегмента. Не все сегментные регистры равнозначны. Регистр CS хранит селектор сегмента кода. МП извлекает очередную инструкцию для исполнения, формируя логический адрес из селектора в CS и смещения в регистре EIP. Значение этого регистра нельзя изменить непосредственно, оно меняется в командах межсегментного перехода (FAR JMP), межсегментного вызова (FAR CALL), при вызове обработчика прерывания (INT) и при возврате из далекой процедуры (RETF) или обработчика прерывания (IRET). Регистр SS хранит селектор сегмента стека. Стек используется для передачи параметров подпрограммам и для сохранения адреса возврата при вызове подпрограммы или обработчика прерывания. Вершиной стека считается байт, логический адрес которого образуется из селектора в регистре SS и смещения в регистре ESP. Регистры DS, ES, FS и GS хранят селекторы сегментов данных. Если инструкция обращается к памяти, но содержит только смещение, то считается, что она обращается к данным в сегменте DS. Сегмент ES может использоваться без явного указания в цепочечных командах. Сегменты FS и GS используются при обращении к памяти только при явном использовании в инструкции префиксов этих сегментов. Указатель команд (EIP) является 32-разрядным регистром. Он содержит смещение следующей команды, подлежащей выполнению. Относительный адрес отсчитывается от базового адреса сегмента исполняемой задачи. Указатель команд непосредственно недоступен программисту, но он изменяется явно командами управления потоком, прерываниями и исключениями (JMP, CALL, RET, IRET, команды условного перехода). Получить текущее значение EIP можно, если выполнить команду CALL, а затем прочитать слово на вершине стека. Регистр системных флагов EFLAGS содержит группу флагов состояния, управления и системных флагов. Младшие 16 бит регистра представляют собой 16-разрядный регистр флагов и состояния МП 8086, называемый FLAGS, который наиболее полезен при исполнении программ для МП 8086 и Intel-286. Некоторые из флагов могут быть изменены специально предназначенными для этой цели инструкциями. Для изменения или проверки группы флагов можно воспользоваться следующими командами: LAHF/SAHF - загрузка/сохранение младших 8 битов регистра флагов в регистре AH; PUSHF/POPF - помещение/извлечение из стека младших 16 битов регистра флагов; PUSHFD/POPFD - помещение/извлечение из стека 32-битного регистра EFLAGS. МП имеет четыре 32-разрядных регистра управления CR0-CR4, в которых хранятся флаги состояния МП или глобальные флаги. Вместе с регистрами системных адресов эти регистры хранят информацию о состоянии МП, которая влияет на все задачи в системе. Системным программистам регистры управления доступны только через варианты команды MOV, которые позволяют их загружать или сохранять в регистрах общего назначения. Шесть доступных регистров отладки (DR0-DR3, DR6, DR7, регистры DR4 и DR5 зарезервированы) расширяют возможности отладки. Они устанавливают точки останова по данным и позволяют устанавливать, задавать точки останова по командам без модификации сегментов программ. Регистры DR0-DR3 предназначены для хранения четырех линейных адресов точек останова. Регистр DR6 отражает текущее состояние точек останова. Регистр DR7 задает условие для точек останова. |