пример реферата. 1. Понятие архитектуры эвм. Принципы фон Неймана 4 1 Использование двоичной системы представления данных 4

Скачать 1.24 Mb. Скачать 1.24 Mb.

|

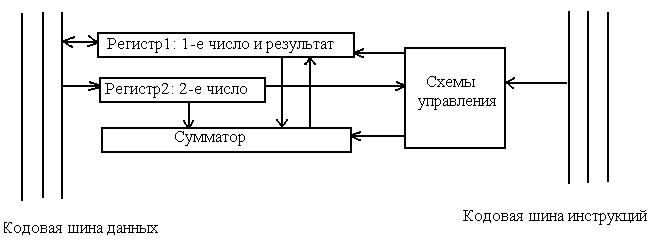

3.1 Структура микропроцессораУстройство управления. Устройство управления является функционально наиболее сложным устройством ПК. Он вырабатывает управляющие сигналы, поступающие по кодовым шинам инструкций во все блоки машины. Упрощенная функциональная схема УУ показана на рис.4.5 Здесь представлены [4, c.98]: Регистр команд - запоминающий регистр, в котором хранится код команды: код выполняемой операции и адреса операндов, участвующих в операции. Регистр команд расположен в интерфейсной части МП, в блоке регистров команд. Дешифратор операций - логический блок, выбирающий в соответствии с поступающим из регистра команд кодом операции (КОП) один из множества имеющихся у него выходов. Постоянное запоминающее устройство микропрограмм - хранит в своих ячейках управляющие сигналы (импульсы), необходимые для выполнения в блоках ПК операций обработки информации. Импульс по выбранному дешифратором операций в соответствии с кодом операции считывает из ПЗУ микропрограмм необходимую последовательность управляющих сигналов. Узел формирования адреса (находится в интерфейсной части МП) - устройство, вычисляющее полный адрес ячейки памяти (регистра) по реквизитам, поступающим из регистра команд и регистров МПП. Кодовые шины данных, адреса и инструкций - часть внутренней шины микропроцессора. В общем случае УУ формирует управляющие сигналы для выполнения следующих основных процедур. Выборки из регистра-счетчика адреса команды МПП адреса ячейки ОЗУ, где хранится очередная команда программы; Выборки ИЗ ячеек ОЗУ кода очередной команды и приема считанной команды в регистр команд. Расшифровки кода операции и признаков выбранной команды. Считывания из соответствующих расшифрованному коду операции ячеек ПЗУ микропрограмм управляющих сигналов (импульсов), определяющих во всех блоках машины процедуры выполнения заданной операции, и пересылки управляющих сигналов в эти блоки. Считывания из регистра команд и регистров МПП отдельных составляющих адресов операндов (чисел), участвующих в вычислениях, и формирования полных адресов операндов. Выборки операндов (по сформированным адресам) и выполнения заданной операции обработки этих операндов. Записи результатов операции в память. Формирования адреса следующей команды программы. Арифметико-логическое устройство. Арифметикo-логическое устройство предназначено для выполнения арифметических и логических операций преобразования информации. Функционально АЛУ (рис.2) состоит обычно из двух регистров, сумматора и схем управления (местного устройства управления).  Рис.2. Функциональная схема АЛУ Сумматор - вычислительная схема, выполняющая процедуру сложения поступающих на ее вход двоичных кодов; сумматор имеет разрядность двойного машинного слова. Регистры быстродействующие ячейки памяти различной длины: регистр 1 (Pr1) имеет разрядность двойного слова, а регистр 2 (Pr2) - разрядность слова. При выполнении операции в Pr1 помещается первое число, участвующее в операции, а по завершении операции - результат; в Pr2 - второе число, участвующее в операции (по завершении операции информация в нем не изменяется). Регистр 1 может принимать информацию с кодовых шин данных, и выдавать информацию с этих шин. Схемы управления принимают по кодовым шинам инструкций управляющие сигналы от устройства управления и преобразуют их в сигналы для управления работой регистров и сумматора АЛУ [5, c.96]. АЛУ выполняет арифметические операции (+,-,*,:) только над двоичной информацией с запятой, фиксированной после последнего разряда, т.е. только над целыми двоичными числами. Выполнение операций над двоичными числами с плавающей запятой и над двоично-кодированными десятичными числами осуществляется или с привлечением математического сопроцессора, или по специально составленным программам. Микропроцессорная память. Микропроцессорная память - память небольшой емкости, но чрезвычайно высокого быстродействия (время обращения к МПП, т.е. время, необходимое на поиск, запись или считывание информации из этой памяти, измеряется наносекундами). Она предназначена для кратковременного хранения, записи и выдачи информации, непосредственно в ближайшие такты работы машины участвующей в вычислениях; МПП используется для обеспечения высокого быстродействия машины, ибо основная не всегда обеспечивает скорость записи, поиска и считывания информации, необходимую для эффективной работы быстродействующего микропроцессора. Микропроцессорная память состоит из быстродействующих регистров с разрядностью не менее машинного слова. Количество и разрядность регистров в разных микропроцессорах различны. Регистры микропроцессора делятся на регистры общего назначения и специальные. Специальные регистры применяются для хранения различных адресов (адреса команды, например), признаков результатов выполнения операций и режимов работы ПК (регистр флагов, например) и др. Регистры общего назначения являются универсальными и могут использоваться для хранения любой информации, но некоторые из них тоже должны быть обязательно задействованы при выполнении ряда процедур. Интерфейсная часть микропроцессора. Интерфейсная часть МП предназначена для связи и согласования МП системной шиной ПК, а также для приема, предварительного анализа команд выполняемой программы и формирования полных адресов операндов и команд [1, c.89]. Интерфейсная часть включает в свой состав адресные регистры МПП, узел формирования адреса, блок регистров команд, являющийся буфером команд в МП, внутреннюю интерфейсную шину МП и схемы управления шиной и портами ввода-вывода. Порты ввода-вывода - это пункты системного интерфейса ПК, через которые МП обменивается информацией с другими устройствами. Всего портов у МП может быть 65536. Каждый порт имеет адрес - номер порта, соответствующий адресу ячейки памяти, являющейся частью устройства ввода-вывода, использующего этот порт, а не частью основной памяти компьютера. Порт устройства содержит аппаратуру сопряжения и два регистра памяти - для обмена данными и обмена управляющей информацией. Некоторые внешние устройства используют и основную память для хранения больших объемов информации, подлежащей обмену. Многие стандартные устройства (НЖМД, НГМД, клавиатура, принтер, сопроцессор и др.) имеют постоянно закрепленные за ними порты ввода-вывода. Схема управления шиной и портами выполняет следующие функции: формирование адреса порта и управляющей информации для него (переключение порта на прием или передачу и др.); прием управляющей информации от порта, информации о готовности порта и его состоянии; организацию сквозного канала в системном интерфейсе для данных между портом устройства ввода-вывода и МП [3, c.75]. |