лаб. Архитектура 8разрядного однокристального микропроцессора серии К580 Общая характеристика однокристального мп серии К580

Скачать 109.5 Kb. Скачать 109.5 Kb.

|

|

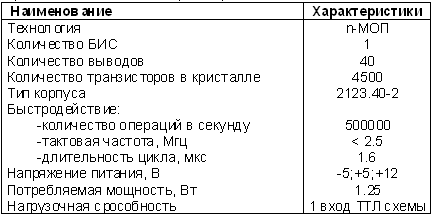

Архитектура 8-разрядного однокристального микропроцессора серии К580 Общая характеристика однокристального МП серии К580 Микропроцессор КР580ИК80А является программируемой универсальной БИС, может считывать информацию из внешних устройств, памяти и производить над ней арифметические и логические операции, анализировать результаты вычислений и записывать данные в память и внешние устройства, функционируя при этом под управлением команд из некоторого фиксированного множества. Микропроцессорная БИС КР580ИК80 представляет собой однокристальный 8-разрядный МП с двумя магистралями: однонаправленной 16-разрядной адресной магистралью (МА), двунаправленной 8-разрядной магистралью данных (МД) и 12 сигналами управления (шесть входных и шесть выходных). Таблица 1 - Технические характеристики БИС КР580ИК80  Условное обозначение МП БИС К580ИК80 приведено на рисунке 2.  Функциональное назначение внешних выводов МП БИС КР580ИК80: Адресная шина (А0-А15), обеспечивающая адресацию к любой из 216 8-разрядной ячейке памяти или внешнего устройства (ВУ); Двунаправленная шина данных (Д0-Д7), используемая для обмена информации с памятью или ВУ; Шина управления (выходная): СИНХР (SYNC) - на этом выходе МП БИС фпрмируется сигнал СИНХР в начале каждого машинного цикла; П (DBIN,прием) - сигнал ПРИЕМ на этом выходе указывает на готовность МП БИС к приему данных; ОЖД (WAIT,ожидание) - сигнал ОЖД на этом выходе указывает что МП находится в состоянии ожидания; ЗП (WR)- на этом выходе МП БИС сигнал ЗП указывает, что данные выданы МП БИС и установлены на МД (магистраль данных) и могут быть записаны в ВУ; П.ЗХ (HLDA, подтверждение захвата) - на этом выходе МП БИС сигнал П.ЗХ появляется в ответ на сигнал З.ЗХ (запрос захвата) и указывает, что МД и МА находятся в состоянии высокого сопротивления; Р.ПР (INTE, разрешение прерывания) - на этом выходе сигнал Р.ПР указывает на состояние внутреннего триггера разрешения прерывания МП БИС. Состояние триггера может быть установлено программно с помощью команд EI,DI. При уровне “0” на выходе Р.ПР прием запросов прерывания МП БИС невозможен. Шина управления (входная): Г (READY, готов) - сигнал ГОТОВ на этом входе информирует о готовности ВУ к обмену информацией с МП БИС . При уровне “0” МП БИС будет находиться в состоянии ОЖИДАНИЕ. З.ЗХ (HOLT, запрос захвата) - вход, используемый для подачи сигнала З.ЗХ на переход МП БИС в состояние ЗАХВАТ, в котором МА и МД переходят в третье состояние (высокое сопротивление). Обычно состояние используется для организации обмена информацией по каналу прямого доступа к памяти; З.ПР (INT, запрос прерывания) - вход, используемый для подачи сигнала З.ПР. Сигнал поступает от внешнего источника на прерывание выполнения основной программы и переход на выполнение подпрограмм обслуживания прерывания. Сигнал запроса прерывания не воспринимается МП БИС при работе его в режимах ЗАХВАТ, ОЖИДАНИЕ или нулевом состоянии внутреннего тригера разрешения прерывания; R (RESET)- вход, по которому поступает сигнал на начальную установку МП БИС, при этом обнуляется его программный счетчик, внутренние триггеры, формирующие сигналы Р.ПР и П.ЗХ; CLK1,2 - входы для подачи тактовых сигналов Ф1(СДК1) и Ф2(СДК2). Эти сигналы являются не пересекающимися во времени сигналами, определяющими тактовую частоту работы МП БИС. Структурная схема МП Микропроцессорная БИС, представленная на рисунке 3, включает в себя следующие функциональные блоки: - блок регистров; - арифметическо-логический блок; - устройство управления (УУ); - буферные схемы шины данных (БФД) и шины адреса (БФА). Секция регистров включает шесть 16-разрядных регистров: W,Z,B,C,D,E,H,L; РС (программный счетчик) и SP (указатель стека). Шесть 8-разрядных регистров общего назначения составлены в пары регистров:B,C; D,E; H,L. Они могут быть использованы в программах как отдельные 8-разрядные регистры или как три 16-разрядных регистра (B,D,H). Программный счетчик РС содержит текущий адрес памяти, к которому обращается программа. Содержание РС автоматически изменяется в течении каждого цикла команды. Указатель стека SР содержит адрес памяти, начиная с которого ее можно применять для хранения и восстановления содержимого программно- доступных регистров МП БИС. Указатель стека SP служит для работы со стековой памятью и определяет адрес последней занятой ячейки стека. Буферные регистры 0W,Z не являются программно доступными регистрами и используются для выполнения команд внутри МП БИС.  Арифметическо-логический блок выполняет арифметические и логические операции под воздействием устройства управления МП БИС. Он включает в себя 8-разрядное АЛУ, схему десятичной коррекции ДК, построенной на базе ПЗУ, 5-ти разрядный регистр признаков, аккумулятор А, буфер аккумуляторя БФА и буферный регистр БФРг. Арифметическо-логический блок позволяет осуществить арифметические операции сложения, вычитания, а также основные логические операции (И, ИЛИ, исключающее ИЛИ) и сдвиг. При проведении операции одно число всегда берется из буфера аккумулятора, а другое - из буферного регистра. По результату выполнения арифметико-логических операций АЛБ устанавливает в регистре признаков пять знаков. Признак переноса (Carry - C) устанавливается в единицу, если при выполнении команд появляется единица переноса из старшего разряда. Дополнительный признак переноса (Auxiliary carry - АС) устанавливается в единицу, если при выполнении команд возникает единица переноса из третьего разряда числа. Состояние разряда может быть проанализировано лишь командой десятичной коррекции числа. Признак знака (Sign - S) в машинном слове можно представить числом от -128 до 127. В этом случае седьмой (старший) разряд числа - его знак. Единица в седьмом разряде при такой записи будет указывать на отрицательное число, а ноль- на положительное. В разряд нулевого признака (Zero -Z) записывается единица, если при выполнении команды результат равен нулю. В разряд признака четности (Parity - P) записывается единица, если при выполнении команды количество единиц в разрядах результата будет четным. Регистр команд РгК и дешифратор команды ДШК используются в МП БИС для получения и дешифрации кода команды. При извлечении команды первый байт, содержащий ее код, помещается в регистр команды и поступает на дешифратор команд. Дешишифратор совместно с устройством управления и синхросигналами Ф1 и Ф2 формируют управляющие сигналы для всех внутренних блоков МП БИС, а также его выходные сигналы управления и состояния. Выполнение каждой команды производится в МП БИС в строго определенной последованности, определяемой кодом команды, и синхронизируется во времени сигналами Ф1 и Ф2 тактового генератора. Период синхросигналов CLK1 и CLK2 называется МАШИННЫМ ТАКТОМ (Т). Длительность машинного такта Т может быть установлена произвольно в диапазоне от 0.5 до 2 микросекунд. При использовании МП БИС необходимо ясно представлять динамику его работы, т.е. на каких магистралях, в зависимости от каких управляющих сигналов и когда МП БИС будет выдавать ту или иную информацию. Это в дальнейшем поможет понимать работу схем, позволяющих согласовывать ее с различными периферийными устройствами микро-ЭВМ. При анализе процессов будем использовать следующие понятия: Машинный цикл (М)-время , требуемое для извлечения из памяти один байт информации или выполнение команды, определяемой одним машинным словом. Машинный цикл может состоять из 3-5 машинных тактов. Время выполнения команды - время получения, декодирования и выполнения команды. В зависимости от вида команды это время может состоять из 1-5 машинных циклов. Для МП БИС КР580ИК80 существует 10 различных типов машинных циклов: 1. Извлечение кода команды (М1). 2. Чтение данных из памяти. 3. Запись данных в память. 4. Извлечение из стека. 5. Запись данных в стек. 6. Ввод данных из внешнего устройства. 7. Запись данных во внешнее устройство. 8. Цикл обслуживания прерывания. 9. Останов. 10. Обслуживание прерываний при работе МП БИС в режиме останова. Тип выполняемого цикла МП указывает на первом такте каждого машинного цикла с помощью 8-разрядного слова состояния, выдаваемого на ШД. Отдельные разряды слова состояния задействуются в микро-ЭВМ для формирования магистрали управления. Слово состояния выдается на ШД лишь на интервале синхросигналов С (такты Т1 и Т2), а используется на протяжении всего машинного цикла, поэтому необходимо записать его в специальный регистр слова состояния РгСС. На рисунке 4 приведена схема записи слова состояния.  Запись осуществляется с использованием сигнала “Синхро” и тактового импульса Ф1. Сигнал “Синхро” появляется в начале каждого цикла и занимает промежуток времени между положительными фронтами тактового импульса Ф2 на тактах Т1 и Т2. Таким образом, запись слова состояния осуществляется сигналом Ф1 на такте Т2. Состояние разрядов в регистре состояний для всех типов машинных циклов приведены в таблице 2. Таблица 2 - Слово состояния процессора  Рассмотрим временные диаграммы работы процессора при различных машинных циклах. Извлечение кода команды или данных из памяти или внешнего устройства. Цикл М1 является основным циклом с которого начинается выполнение любой команды, поэтому временные процессы для него рассмотрим более подробно. Анализ процессов будем проводить по каждому машинному такту Т (рисунок 5). На такте Т1 программный счетчик МП выдает на ША адрес ячейки памяти, из которой будет считываться код команды. При этом схема приращения адреса МП автоматически увеличивает на единицу значение числа, записанного в программном счетчике. Положительным фронтом тактового импульса Ф2 формируется сигнал “Синхро” и выдается слово состояния на ШД. Сигнал “Прием”, управляющий двунаправленным шинным формирователем (ШФ) шины данных (рисунок 6), на этом такте равен нулю, что позволяет слову состояния поступить на ШД процессора.   На такте Т2 слово состояния записывается в регистр. Положительным фронтом Ф2 заканчивается сигнал “Синхро” и формируется единичный сигнал “Прием”, позволяющий данным поступить на вход МП через ШФ. На такте Т2 из сигнала “Прием” и седьмого разряда слова состояния (Д7) формируется сигнал на чтение данных из памяти (Чт. памяти), позволяющий данным поступать из памяти на ШД (см. рисунок 5 ). На этом же такте анализируется состояние сигналов “Готов” и “Захват”. При нулевом сигнале на входе “З.Зх” и единичном сигнале на входе “Готов” МП переходит к выполнению такта Т3. Если к моменту появления отрицательного фронта Ф2 на такте Т2 сигнал на входе “Готов” будет иметь нулевой потенциал, то МП на такте Т3 переходит в режим ожидания. В этом режиме приостанавливается процесс обработки данных и формируется единичный сигнал на выходе “Ожидание”, подтверждающий это состояние. Время ожидания выражается целым числом тактов и может длиться бесконечно долго. На каждом такте в этом режиме при отрицательном фронте Ф2 будет проверяться состояние сигнала на входе “Готов”. Изменения в диаграммах работы МП в режимах “Захват”, “Останов” и “Прерывание” будут рассмотрены отдельно. На такте Т3 в момент отрицательного фронта сигнала Ф1 производится запись данных во внутренний регистр кода команды. Положительным фронтом Ф2 снимается сигнал “Прием” на выходе МП и, следовательно, сигнал “Чт. памяти”. На последующих тактах Т4 и Т5 . дешифратор кода команды расшифровывает код команды, определяет количество байтов в команде, формирует команды на внутренние пересылки данных и подготавливает МП к выполнению следующих машинных циклов. Отличие машинных циклов чтения данных из памяти или внешнего устройства будет заключаться лишь в том, что МП будет воспринимать числа, полученные на такте Т3 по ШД не как код команды, а как данные. При приеме данных из внешнего устройства на ШУ формируется сигнал чтение устройства ввода-вывода (Чт.ВУ) из сигнала “Прием” и разряда Д6 регистра состояния. Этот сигнал позволяет именно ВУ выдать информацию на ШД процессора. Запись данных в память или внешнее устройство Процесс записи данных в память иллюстрируется на схеме, показанной на рисунке 7.  На такте Т1 содержимое регистра адреса МП выдается на ША, а на ШД выдается слово состояния. На такте Т2 на ШД выдаются данные для записи в память. На такте Т3 формируется сигнал “Запись”, по которому будет проходить запись данных в память или ВУ. На протяжении всего машинного цикла записи данных в память сигнал “Прием” находится на нулевом уровне, что позволяет двунаправленному шинному формирователю работать в режиме выдачи данных на ШД МП. Процесс записи данных во внешнее устройство аналогичен записи данных в память. Единственное отличие этого процесса заключается в том, что вместо сигнала “Зп.память” формируется сигнал “Зп.в ВУ”, т.е. в первом случае выполнялась сборка по “И” для сигналов “Запись” с МП и “Память” с РгСС, а во втором - сборка по “И” для сигналов “Запись” и “Вывод”. Работа в режиме ЗАХВАТ Режим “Захват” используется для приостановки процесса управления работой всех периферийных устройств. При работе в этом режиме выходные магистрали МП переводятся в третье состояние и отключаются от магистралей внешних устройств, обеспечивая тем самим возможность обмена информацией по каналу прямого доступа к памяти. Режим “Захват” инициируется подачей лог.1 на вход управления МП “З.Зх”. Переход МП в этот режим подтверждается путем выдачи сигнала лог.1 на выходе МП “П.Зх”. Состояние “Захват” будет длиться целое число машинных тактов. Снятие сигнала “Захват”, т.е. появление лог.0 на входе “З.Зх” проверяется на каждом сигнале Ф2 и при его обнаружении МП перейдет к выполнению очередного машинного цикла начиная с такта Т1. Работа в режиме ОСТАНОВ Режим ОСТАНОВ является результатом выполнения команды HALT. Находясь в этом режиме, магистрали МП БИС не отключаются от магистралей микро-ЭВМ, а процессор просто отмечает время, в течение которого он ничего не выполняет. Состояние микро-ЭВМ в этом режиме аналогично состоянию ОЖИДАНИЕ, за исключением того, что это состояние устанавливается программно. Обычно режим ОСТАНОВ оканчивается тогда, когда ВУ выдают запрос на обслуживание. Одним из методов формирования запроса на обслуживание является подача запроса прерывания на вход З.Пр процессора. Если сигналы прерывания не воспринимаются процессором (например, после выполнения команды DI), то остается один выход из состояния ОСТАНОВ - подача сигнала начальной установки на вход R процессора. Специфика режима ОСТАНОВ заключается в том, что в этом состоянии МП может входить в режим ЗАХВАТ и выходить из него. В режиме ОСТАНОВ запрос на ЗАХВАТ не будет удовлетворяться, если запрос на прерывание был уже подан на вход З.Пр., но не было еще подтверждено его обслуживание. После подтверждения получения прерывания (уровень “0” на выходе П.Пр) микро-ЭВМ может войти в состояние ЗАХВАТ. Обслуживание запросов на прерывание Внешние устройства выдают сигнал запроса прерывания асинхронно по отношению к работе МП путем подачи уровня “1” на вход З.Пр. Запрос может быть удовлетворен только в том случае, если МП находится в состоянии разрешения восприятия запросов прерывания. МП автоматически устанавливается в состояние запрета запросов прерывания после выполнения начальной установки, а также после начала обслуживания запроса прерывания. Управление состоянием восприятия запросов прерывания может осуществляться программно с помощью команд: EI - “Разрешение прерываний” и DI - “Запрет прерываний”. Состояние восприятия запросов прерывания МП указывает на своем выходе Р.Пр. Если на этом выходе присутствует уровень “1”, то запросы прерывания могут быть восприняты, в противном случае (уровень “0” на выоде Р.Пр) запросы восприниматься не будут. Если запрос на прерывание принят, то начинается цикл обслуживания прерывания. Машинный цикл прерывания, который начинается в такте Т1 в условиях разрешенного прерывания, в основных чертах повторяет машинный цикл выборки команды. В течение времени, определяемого единичным значением сигнала синхронизацина ШД выставляется слово состояния “Разрешение прерывания”. На такте Т2 слово состояния записывается в регистр состояний и формируется единичный сигнал “Прием”, позволяющий поступление на ШД кода прерывания. Имеется два способа задания кода прерывания: с помощью команды RST (N) или команды CALL (A1), (A2). Отличие машинного цикла прерывания от машинного цикла извлечения кода команды из памяти состоит в том, что содержимое программного счетчика не увеличивается, а запоминается, чтобы оно могло быть восстановлено после окончания программы прерывания и возврата к прерванному процессу (программе). В такте Т3 по шине данных начальная команда программы прерывания RST, подготовленная периферийным устройством, помещается в регистр команд МП. Получив команду на первом машинном цикле, МП на циклах М2 и М3 записывает в область памяти, отведенной под стек, текущее значение программного счетчика РС. Сохранение содержимого РС в стеке необходимо для возврата к прерванной программе после окончания выполнения подпрограммы обслуживания прерывания. Возврат из подпрограммы осуществляется командой RET, которая загружает содержимое двух верхних ячеек стека в РС. Начальная установка В течение всего времени, пока входе R установлен уровень “1”, все операции в МП будут приостановлены. За это время обнуляются программный счетчик, триггер разрешения прерывания и внутренняя логика, связанная с формированием сигнала П.Зх. Следовательно, первая выполняемая команда будет считываться по адресу 0000. После начала выполнения программы прерывания остаются отключенными. Для восстановления возможности восприятия запросов прерывания в программу необходимо включить команду EI. Контрольные вопросы.

1. Микропроцессор КР580ИК80А является программируемой универсальной БИС, может считывать информацию из внешних устройств, памяти и производить над ней арифметические и логические операции, анализировать результаты вычислений и записывать данные в память и внешние устройства, функционируя при этом под управлением команд из некоторого фиксированного множества. Микропроцессорная БИС КР580ИК80 представляет собой однокристальный 8-разрядный МП с двумя магистралями: однонаправленной 16-разрядной адресной магистралью (МА), двунаправленной 8-разрядной магистралью данных (МД) и 12 сигналами управления (шесть входных и шесть выходных). 2. СИНХР (SYNC) - на этом выходе МП БИС формируется сигнал СИНХР в начале каждого машинного цикла; П (DBIN,прием) - сигнал ПРИЕМ на этом выходе указывает на готовность МП БИС к приему данных; ОЖД (WAIT,ожидание) - сигнал ОЖД на этом выходе указывает что МП находится в состоянии ожидания; ЗП (WR)- на этом выходе МП БИС сигнал ЗП указывает, что данные выданы МП БИС и установлены на МД (магистраль данных) и могут быть записаны в ВУ; П.ЗХ (HLDA, подтверждение захвата) - на этом выходе МП БИС сигнал П.ЗХ появляется в ответ на сигнал З.ЗХ (запрос захвата) и указывает, что МД и МА находятся в состоянии высокого сопротивления; Р.ПР (INTE, разрешение прерывания) - на этом выходе сигнал Р.ПР указывает на состояние внутреннего триггера разрешения прерывания МП БИС. Состояние триггера может быть установлено программно с помощью команд EI,DI. При уровне “0” на выходе Р.ПР прием запросов прерывания МП БИС невозможен. Шина управления (входная): Г (READY, готов) - сигнал ГОТОВ на этом входе информирует о готовности ВУ к обмену информацией с МП БИС . При уровне “0” МП БИС будет находиться в состоянии ОЖИДАНИЕ. З.ЗХ (HOLT, запрос захвата) - вход, используемый для подачи сигнала З.ЗХ на переход МП БИС в состояние ЗАХВАТ, в котором МА и МД переходят в третье состояние (высокое сопротивление). Обычно состояние используется для организации обмена информацией по каналу прямого доступа к памяти; З.ПР (INT, запрос прерывания) - вход, используемый для подачи сигнала З.ПР. Сигнал поступает от внешнего источника на прерывание выполнения основной программы и переход на выполнение подпрограмм обслуживания прерывания. Сигнал запроса прерывания не воспринимается МП БИС при работе его в режимах ЗАХВАТ, ОЖИДАНИЕ или нулевом состоянии внутреннего тригера разрешения прерывания; R (RESET)- вход, по которому поступает сигнал на начальную установку МП БИС, при этом обнуляется его программный счетчик, внутренние триггеры, формирующие сигналы Р.ПР и П.ЗХ; CLK1,2 - входы для подачи тактовых сигналов Ф1(СДК1) и Ф2(СДК2). Эти сигналы являются не пересекающимися во времени сигналами, определяющими тактовую частоту работы МП БИС. 3. |