Первая часть. Декодер с обнаружением и исправлением ошибок

Скачать 85.64 Kb. Скачать 85.64 Kb.

|

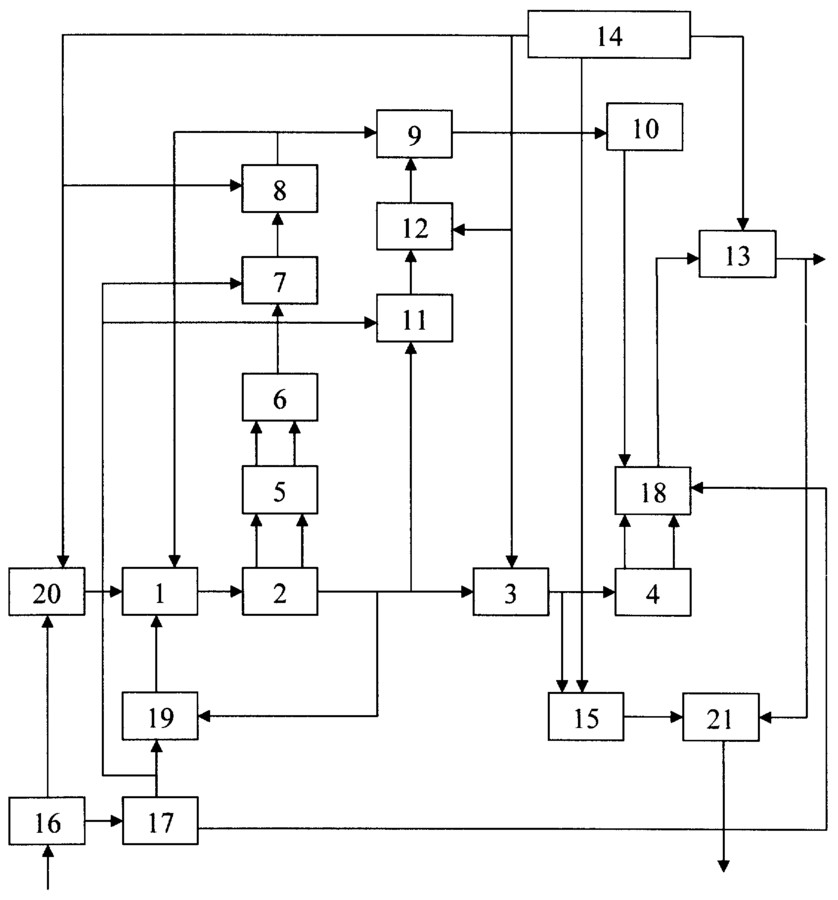

Белорусский национальный технический университет Белорусский национальный технический университетФакультет информационных технологий и робототехники Кафедра «Робототехнические системы» Курсовая работа по дисциплине «Схемотехника» Тема: «Декодер с обнаружением и исправлением ошибок» Выполнил: студент группы Руководитель: ст. пр. кафедры РТС Тимошевич В. Б. Минск 2018 Белорусский национальный технический университет Факультет информационных технологий и робототехники Кафедра «Робототехнические системы» Пояснительная записка к курсовой работе по дисциплине «Схемотехника» Тема: «Декодер с обнаружением и исправлением ошибок» Выполнил: студент группы Руководитель: ст. пр. кафедры РТС Тимошевич В. Б. Минск 2018 Введение В общем случае декодер — это некоторое звено, которое преобразует информацию из одного внешнего вида в другой вид, применяемый в каком-нибудь устройстве. В цифровой микросхемотехнике: микросхема, модуль или устройство, преобразующее форматы, системы счисления, виды представления данных. Передача данных — физический перенос данных в виде сигналов от точки к точке или от точки к нескольким точкам средствами электросвязи по каналу передачи данных, как правило, для последующей обработки средствами вычислительной техники. Передача данных может быть аналоговой или цифровой, а также модулирована посредством аналоговой модуляции, либо посредством цифрового кодирования. Изобретение относится к технике передачи данных и может использоваться в системах с решающей обратной связью для приема информации, закодированной циклическим кодом, допускающим мажоритарную процедуру декодирования. Технический результат - повышение помехоустойчивости и точности декодирования. ОПИСАНИЕ РАБОТЫ ФУНКЦИОНАЛЬНОЙ СХЕМЫ  Декодер с обнаружением и исправлением ошибок содержит первый элемент ИЛИ 1, регистр 2 сдвига, первый ключ 3, вычислитель 4 синдрома, сумматоры 5, мажоритарный элемент 6, второй ключ 7, третий ключ 8, сумматор 9 по модулю два, счетчик 10 исправлений, четвертый ключ 11, пятый ключ 12, шестой ключ 13, счетчик 14 сдвигов, седьмой ключ 15, блок 16 дискретного интегрирования, счетчик 17 недостоверных символов, второй элемент ИЛИ 18, восьмой ключ 19, девятый ключ 20 и буферный регистр 21 сдвига. Выход первого элемента ИЛИ 1 соединен со входом регистра 2 сдвига, выход которого через первый ключ 3 соединен со входом вычислителя 4 синдрома. Вторые выходы регистра 2 сдвига через сумматоры 5 соединены со входами мажоритарного элемента 6, выход которого через второй ключ 7 соединен с сигнальным входом третьего ключа 8. Выход третьего ключа 8 соединен одновременно с третьим входом первого элемента ИЛИ 1 и со входом сумматора 9 по модулю два, выход которого соединен со входом счетчика 10 исправлений. Выход регистра 2 сдвига подключен ко входу четвертого ключа 11, выход которого через пятый ключ 12 соединен со вторым входом сумматора 9 по модулю два. Первый выход счетчика 14 сдвигов подключен к управляющим входам первого 3, третьего 8 и пятого 12 ключей, а второй и третий выходы счетчика сдвигов 14 подключены к управляющим входам соответственно шестого 13 и седьмого 15 ключей, к сигнальному входу которого подключен выход первого ключа 3. Первый выход блока 16 дискретного интегрирования через счетчик 17 недостоверных символов подключен к первому входу второго элемента ИЛИ 18, ко второму входу которого подключен выход счетчика 10 исправлений, третьи входы второго элемента ИЛИ 18 соединены с выходами вычислителя 4 синдрома, а выход второго элемента ИЛИ 18 подключен к сигнальному входу шестого ключа 13, выход которого подключен к первому входу буферного регистра 21 сдвига. Второй выход блока 16 дискретного интегрирования через девятый ключ 20 соединен с первым входом первого элемента ИЛИ 1, к второму входу которого через восьмой ключ 19 подключен выход регистра 2 сдвига. Второй выход счетчика 17 недостоверных символов подключен к управляющим входам второго 7, четвертого 11 и восьмого 19 ключей. Выход седьмого ключа 15 подключен ко второму входу буферного регистра 21 сдвига. При этом вход блока 16 дискретного интегрирования является входом декодера, выходом которого является выход буферного регистра 21 сдвига. Регистр сдвига 2, сумматоры 5, мажоритарный элемент 6, сумматор 9 по модулю два совместно со вторым 7, третьим 8, четвертым 11 и пятым 12 ключами выполняют функции устройства исправления ошибок мажоритарным способом. Буферный регистр сдвига 21 содержит элементы памяти для хранения в них информации и выдачи ее потребителю. Одновременно он выполняет функции элемента задержки кодовых слов на время анализа элементов кодового слова, что способствует исключению возможности выдачи искаженной информации потребителю. |