порт. Дипломный проект дп 09. 02. 01 Эвм475102020 2020 Министерство образования и молодежной политики Свердловской области

Скачать 1.19 Mb. Скачать 1.19 Mb.

|

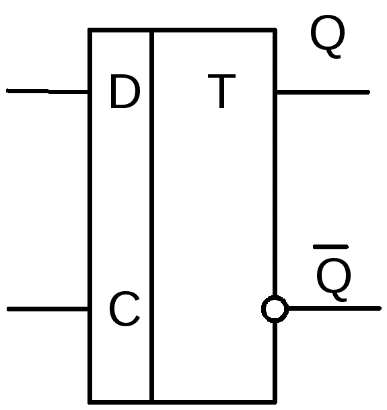

4.10 Синтез синхронного D-триггераD-триггер называют триггер-защелка (от англ. Delay – задержка). Логика работа D-триггера заключается в следующем: триггер D-типа устанавливает на выходе состояние, совпадающее с сигналом на входе D, и удерживает это состояние до прихода следующего входного сигнала. Таблица 18 - Переходы асинхронного D-триггера

Уравнение переходов D-триггера:  Синхронный D-триггер имеет такую же логику работу, но она реализуется только при наличии на синхронизирующем входе “C” уровня логической единицы. Если на тактирующем входе “C” действует уровень логического нуля, то состояние триггера не меняется. Таблица 19 - Переходы синхронного D-триггера

Рисунок 31 - Условно графическое изображение синхронного D-триггера Заполним карту Карно, согласно таблице 2 переходов D-триггера  Рисунок 32 - Карта Карно составленная по таблице переходов D-триггера В результате склейки единиц получаем следующее уравнене переходов, соотвествующее логике работы синхронного D-триггера:  Если ввести следующие обозначения  , то получим : , то получим : Это уравнение соответсвует функции переходов асинхронного RS-триггера. Если на вход S асинхронного RS-триггера подавать сигнал CD, а на вход R – сигнал C, то получим синхронный D-триггер. Однако, в связи с тем, что синхронный D-триггер работает, как было установлено, при наличии на тактирубщем входе “C” уровня логической единицы, то при наличии на входе “D”, так же, уровня логической единицы, получим на входах R и S одновременно выской логический потенциал, что, как известно, является запрещенным состоянием для асинхронного RS-триггера. Поэтому для реализации синхронного D-триггера на основе асинхронного RS-триггера при рассмотрении карты Карно вводят дополнительную избыточную склейку, выделенную на рисунке 3 красным пунктиром.  Рисунок 33 - Карты Карно переходов D-триггера В этом случае уравнение переходов синхронного D-триггера приобретает следующий вид:  Преобразуем полученную формулу:  Теперь, если в качестве S взять CD, а в качестве  , то в этом случае возможность одновременного появления на входах R и S логической единицы исключается. , то в этом случае возможность одновременного появления на входах R и S логической единицы исключается.С учетом изложенного, схема синхронного D-триггера, реализованного на основе асинхронного RS-триггера с негативной логикой на входе, будет иметь следующий вид:  Рисунок 34 - Синхронный D-триггер на основе RS-триггера с негативной логикой на входе |