курсачь по электронике ат. АТ-006-КР Смирнов.И.В. Федеральное агенство железнодорожного

Скачать 1.03 Mb. Скачать 1.03 Mb.

|

1 2

| |||||||||||||||||||||||||||||||||||||||||||||||||||||

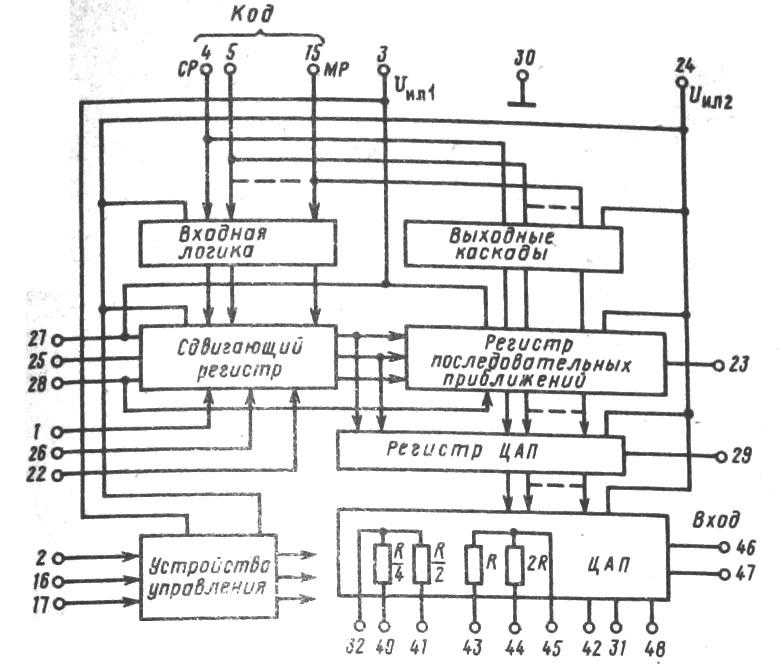

| 1 – последовательный вход 2 – входы управления СР 3 – напряжение питания UИП1 4-15 – цифровые входы (выходы) 16 – вход управления МР 17 – вход управления режимом Р 22 – выход «цикл» 23 – вход сравнения 24 – напряжение питания UИП2 25 – вход ТИ 26 – выход «конец преобразования» 27 – вход «запуск» 28 – вход «цикл» 29 – вход стробирования ЦАП 30 – цифровая земля 31 – конечный вывод матрицы R-2R | 32 – общий вывод резисторов R1, R2 40 – вывод резистора R1 41 – вывод резистора R2 42 – опорное напряжение 43 – аналоговый вход 1 44 – аналоговый вход 2 45 – общий вывод резисторов аналоговых входов 1, 2 46 – аналоговый выход 1 47 – аналоговый выход 2 48 – аналоговая земля |

Устройство управления обеспечивает следующие режимы работы микросхемы: АЦП, ЦАП, раздельное управление старшими и младшими разрядами, хранение информации в регистре ЦАП. Управление режимами осуществляется в соответствии с табл. 1.

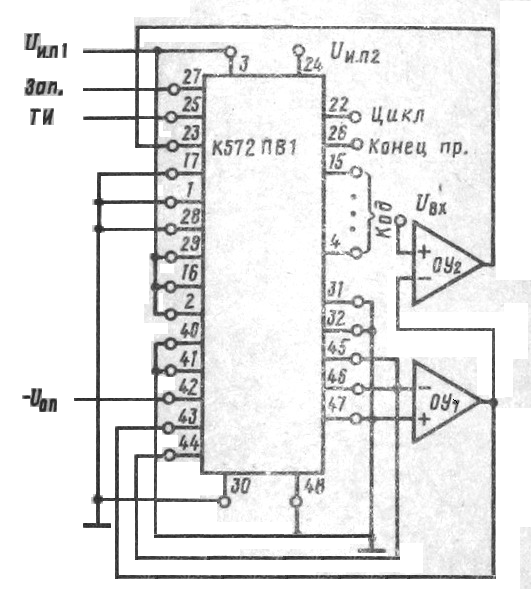

На рис. 5 показан вариант включения АЦП, обеспечивающий повышенную точность и стабильность преобразования. В АЦП имеется дополнительный буферный усилитель ОУ1, напряжение АЦП и входное напряжение сравниваются на ОУ2.

Преобразователь может работать в режиме сравнения токов АЦП и входного сигнала на компараторе ОУ1. При этом обеспечивается максимальное быстродействие. Для включения АЦП в этом режиме необходимо вывод ОУ соединить непосредственно с выводом 23, на вывод 43 подать UВХ, вывод 40 соединить с выводом 44. Включение резисторов R/2 и 2R на входе ОУ1 позволяет изменять UВХ от 0,5UОП до 2UОП. Полярность UВХ может быть любой и определяется полярностью UОП.

Рис. 4 Функциональная схема АЦП.

Таблица 1 Режимы работы микросхемы.

| Режим | Информационно-цифровые разряды | Входы управления | Вход строб | |||

| СР | МР | Р | ||||

| АЦП | 1…12 | 1 | 1 | 0 | 1 | |

| 1…4 | 1 | 0 | 0 | |||

| 5…12 | 0 | 1 | 0 | |||

| разомкнуты | 0 | 0 | 0 | |||

| ЦАП | 1…12 | 1 | 1 | 1 | 1 | |

| 1…4 | 0 | 1 | 1 | |||

| 5…12 | 1 | 0 | 1 | |||

| Хранение информации в регистре ЦАП | − | − | − | − | 0 | |

Основные параметры преобразователя

При следующих значениях входных данных:

UИП1 = 5 В, UИП2 = 15 В, UОП = 10,24 В, U0ВЫХ = 0,4 В, U1ВЫХ = 2,4 В,

fТ = 250 кГц

δЛ = ± 0,05%, δЛД = ± 0,1% для КР572ПВ1А;

δД = ±0,1%, δЛД = ± 0,2% для КР572ПВ1Б;

δД = ±0,2%, δЛД = ± 0,4% для КР572ПВ1В;

δПШ = ± 122 ед. МР;

tСРБ = 170 мкс.

Преобразователь может работать в режиме ЦАП. Микросхема переводится в режим ЦАП при подаче напряжения высокого уровня на вывод 17. Запись информации осуществляется подачей на вывод 25 сдвоенного импульса при наличии напряжения низкого уровня на выводе 27. При подаче сдвоенного импульса на вывод 25 и напряжения высокого уровня на вывод 27 информация стирается. Запоминание информации происходит при подаче на вывод 29 напряжения высокого уровня. Для ввода информации в последовательном коде он подаётся на вывод 1 синхронно со сдвоенными импульсами на выводе 25, начиная с МР.

Рис. 5 Включение АЦП.

Преобразователь согласуется с ТТЛ ИС при UИП1 = 5 В ± 5% и с КМДП ИС при UИП1 = 15 В ± 5%. Микросхема может быть согласована с восьмиразрядной шиной данных микропроцессорной системы. Выходы имеют три устойчивых состояния. При работе с микросхемой необходимо соблюдать последовательность включения напряжений и меры защиты.

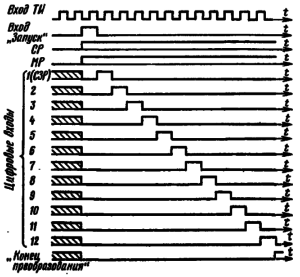

Временные диаграммы работы микросхемы К572ПВ1 (А-В) в режиме АЦП изображены на рисунке 6. Заштрихованы области неопределенного состояния выходов. Напряжение на входе сравнения (вывод 23) U1вк.к = 0

Рис.6. Временные диаграммы работы микросхемы К572ПВ1 (А-В) в режиме АЦП.

2. Расчет элементов схемы управляющего задающего таймера для АЦП К1113ПВ1.

Частота управляющего задающего таймера f0 = 50 кГц, скважность 5.

Выберем для проектирования управляющего задающего таймера микросхему КР1006ВИ1 [2] – рис.7, рис.8.

Выбор микросхемы обосновывается тем, что эта схема представляет собой аналог широко использующейся за рубежом ИС однотактного таймера 555 (по номеру серии первого производителя). Эта микросхема специально предназначена для построения различных высокостабильных импульсных генераторов и таймеров [2,5]. Особо следует отметить высокое быстродействие ИМ, что позволяет проектировать автогенераторы и ждущие генераторы (импульсные) с фронтами до нескольких наносекунд и получать на выходе импульсные сигналы с большой скважностью S≥200 [5]. По количеству областей применения эта интегральная микросхема может конкурировать даже со стандартными операционными усилителями. Остановимся несколько подробнее на её описании структуры и технических характеристик.

Микросхема представляет собой времязадающее устройство (таймер), формирующее импульсы напряжения длительностью от нескольких микросекунд до десятков минут. Выполнена на биполярных транзисторах с изоляцией p-n переходом. Предназначена для применения в стабильных датчиках времени, генераторах импульсов, широтно-импульсных и фазовых модуляторах, преобразователях напряжения, ключевых схемах, преобразователях сигналов, исполнительных устройствах. Корпус типа 2101.8-1 Масса не более 1г.

Функциональный состав: 1 – компаратор напряжения; 2- триггер; 3 – выходной усилитель.

Рисунок 7 - Функциональная схема К1006ВИ1

Приведём ниже принципиальную схему управляющего задающего таймера, выполненную на базе микросхемы КР1006ВИ1 – рис.8.

Рисунок 8 - Принципиальная схема генератора импульсов на микросхеме КР1006ВИ1 в режиме автогенерации

При этом:

;

;  - не более10 МОм при Uп=15В и не более 3 Мом при Uп=5В.

- не более10 МОм при Uп=15В и не более 3 Мом при Uп=5В. 2.1. Расчет уапрвляющего задающего таймера на микросхеме КР1006ВИ1.

Скважность есть отношение периода к длине импульса и по условию = 5, заданная частота управляющего задающего таймера

.

.Период

тогда учитывая, что скважность = 5 имеем:

тогда учитывая, что скважность = 5 имеем:

Исходя из соотношений:

;

; .

.Приняв С1 = 15 нФ рассчитаем номиналы сопротивлений:

;

;Выберем из стандартного ряда Е96 типа С3-23±5%

R2 = 280 Ом, R1 = 820 Ом.

Выберем из стандартного ряда конденсаторы типа К73–9-25±5%

С1 = 15 нФ, С2 = 1 мкФ.

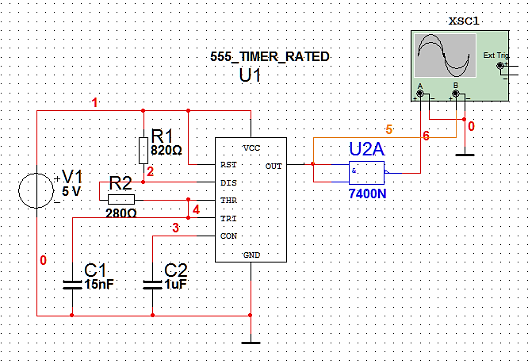

2.2. Моделирование схемы управляющего задающего таймера для АЦП-К1113ПВ1.

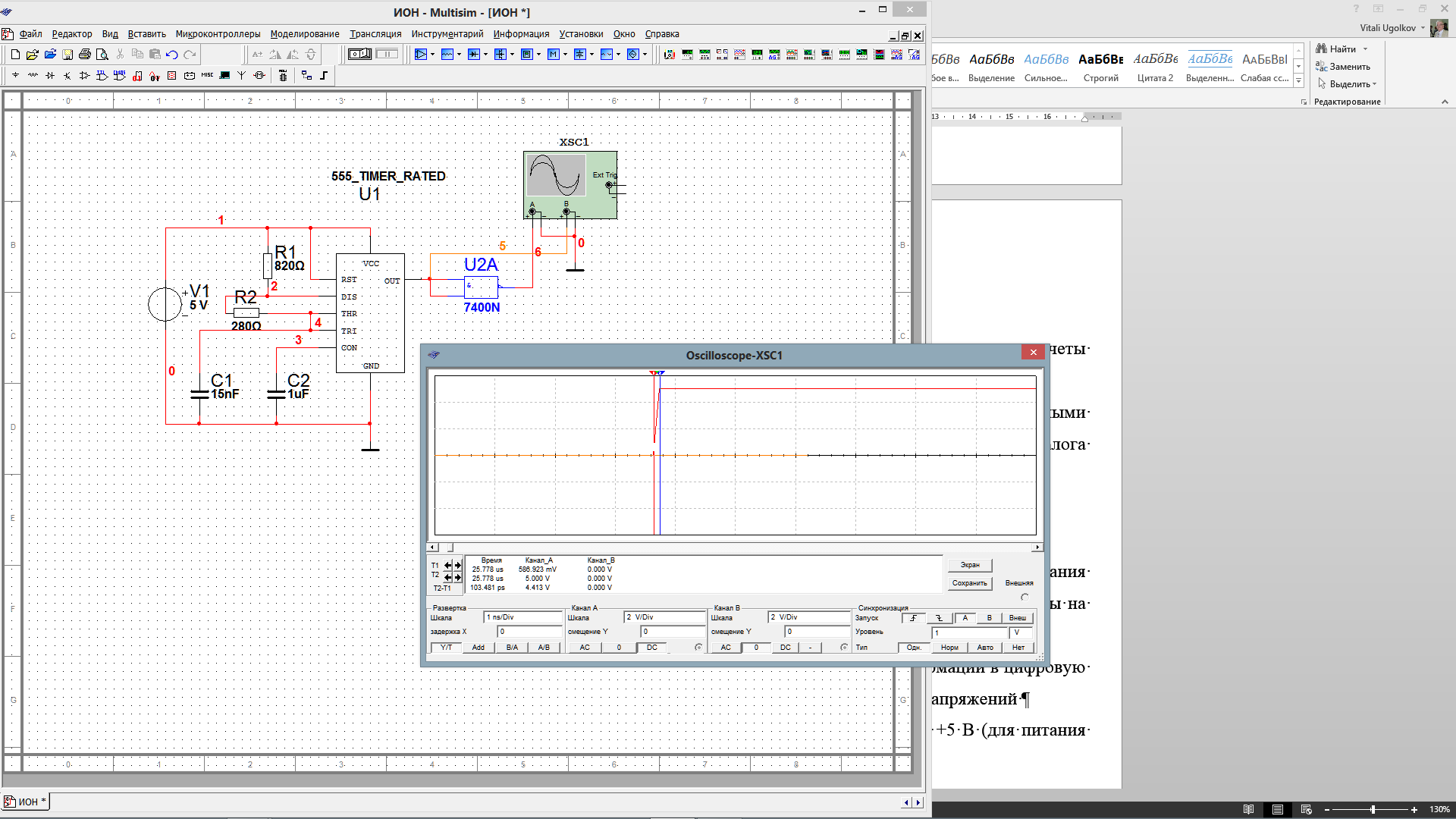

Проверим правильность расчета величин элементов управляющего мультивибратора собранного на микросхеме таймера КР1006ВИ1. Для этого используем систему моделирования электронных схем Multisim 10.

Рисунок 9– Модель схемы управляющего таймера К1006ВИ1 –

аналог NE555.

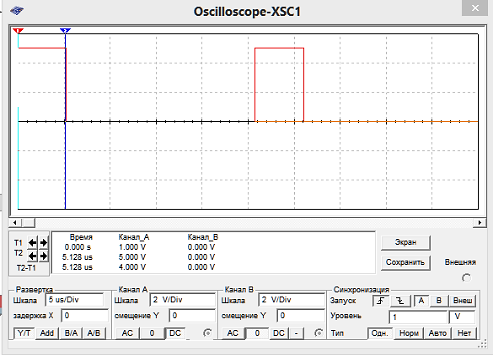

Рисунок 10 – Временная диаграмма работы схемы управляющего таймера К1006ВИ1 – аналог NE555, основной период Т≈25 мкс, длительность импульса Т1≈5 мкс и соответственно скважность равна 25/5=5.

Скважность выходного сигнала с таймера равна 5, что с высокой точностью соответствует заданной.

Рисунок 11 – Измерение длительности фронта сигнала управляющего таймера К1006ВИ1, длительность фронта Тф≈0,1 мкс.

Получилась длительность фронта Тф≈0,1 мкс<0,5 мкс, что соответствует заданию.

Исходя из данных моделирования можно сделать выводы, что расчеты величин элементов произведены правильно.

Небольшое различие в длительности импульсов объясняется различными характеристиками микросхем К1006ВИ1 и модели её зарубежного аналога NE555..

3 Расчет преобразователя уровней (ПУ)

3.1 Расчетные параметры:

Согласуемые элементы серии ИMC: ТТЛШ(К1533)>КМДП(K176):

Нагрузочная способность ПУ: 2

Частота переключения f, МГц: 1

Температурный диапазон, °С: -10 ÷ 70

Монтажная емкость

входная емкость элементов

.

.Преобразователи уровней (ПУ) — специальные элементы цифровых устройств, предназначенные для обеспечения совместимости уровней цифровых элементов различных серий. Иногда ПУ называют транслятором уровней.

При проектировании микроэлектронной аппаратуры на цифровых интегральных микросхемах (ИМС) на практике возникает необходимость в совместном использовании цифровых ИМС различных серий. Эти ИМС могут существенно различаться как конструктивно-технологическими, схемотехническими решениями, так и электрическими параметрами, вследствие чего они не могут сопрягаться непосредственно. ПУ позволяет обеспечить управление интегральным логическим элементом (ЛЭ) одной серии с помощью интегрального логического элемента другой серии, т. е. добиться электрического и временного сопряжении этих двух элементов.

и

и  — входное и выходное напряжения;

— входное и выходное напряжения;  и

и  — уровни логической 1 и логического 0;

— уровни логической 1 и логического 0;  — входные и выходные токи ЛЭ в состояниях логического 0 и логической 1 по входу и выходу;

— входные и выходные токи ЛЭ в состояниях логического 0 и логической 1 по входу и выходу;  — допустимая статическая помеха на нулевом уровне (помехозащищенность снизу) и

— допустимая статическая помеха на нулевом уровне (помехозащищенность снизу) и  — допустимая статическая помеха на единичном уровне (помехозащищенность сверху).

— допустимая статическая помеха на единичном уровне (помехозащищенность сверху).В отличие от логических элементов, у которых значения уровней входных и выходных сигналов, как правило, совпадают, у ПУ значения входных и выходных сигналов всегда различны. Это характерный признак ПУ. Поэтому простейшим способом обеспечения полного сопряжения уровней ЛЭ1 и ЛЭ2 является способ построения схемы, при котором входной каскад ПУ - П1 был реализован аналогично схеме выходного каскада ЛЭ1. Аналогично выходной каскад ПУ - ПЗ должен быть реализован по схеме входного каскада ЛЭ2. Чтобы обеспечить выполнение этих условий при таком способе построения ПУ необходимо одновременно использовать питающие напряжения как ЛЭ1, так и ЛЭ2.

В практических случаях, когда ЛЭ1, ПУ, ЛЭ2 размещены на одной и той же плате или в одном корпусе микросхемы, схему ПУ можно упростить, исключив из нее каскады П1 или ПЗ или оба. В интегральном варианте ПУ может содержать все три каскада П1-П2-ПЗ, так как при этом ограничения на соединения между ПУ и цифровыми ИС с ЛЭ будут такими же, как для связей между цифровыми ИС в данной аппаратуре. Это в определенной степени облегчит конструирование электронных блоков аппаратуры.

3.2 Логический элемент КМПД серия К176

Тип логики: НСТЛМ (дополняющие МОП структуры);

Состав серии: К176ЛА7 – четыре элемента 2ИЛИ-НЕ;

Напряжение питания:

;

;Входной ток уровня логического нуля:

;

;Входной ток уровня логической единицы:

;

;Выходной ток уровня логического нуля:

;

;Выходной ток уровня логической единицы:

;

;Выходное напряжение логического нуля:

;

;Выходное напряжение логической единицы:

;

;Время задержки переключения с нуля на единицу:

;

;Время задержки переключения с единицы на ноль:

;

;Коэффициент разветвления по выходу:

Температурный диапазон:

;

;3.3 Логический элемент ТТЛШ серия К1533.

Тип логики: ТТЛШ.

Состав серии: К1533ЛА1 – два элемента 4И-НЕ;

Напряжение питания:

;

;Входной ток уровня логического нуля:

;

;Входной ток уровня логической единицы:

;

;Выходной ток уровня логического нуля:

;

;Выходной ток уровня логической единицы:

;

;Выходное напряжение логического нуля:

;

;Выходное напряжение логической единицы:

;

;Время задержки переключения с нуля на единицу:

;

;Время задержки переключения с единицы на ноль:

;

;Коэффициент разветвления по выходу:

;

;Температурный диапазон:

;

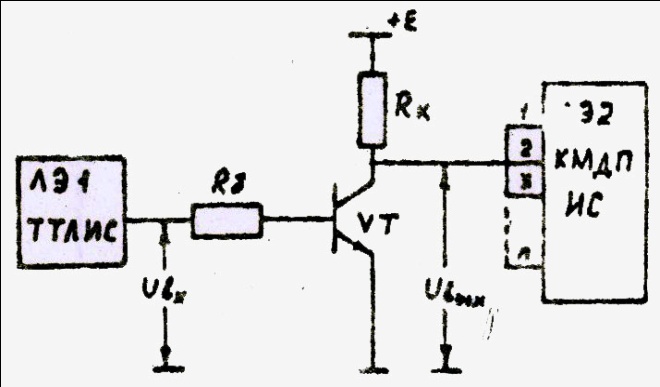

;3.4 Выбор схемы преобразователя уровней.

Необходимо спроектировать и рассчитать преобразователь уровней ТТЛ КМПД. При непосредственно сопряжении ЛЭ ТТЛ-типа с ЛЭ КМПД-типа выходные токи ТТЛ элементов

и

и  могут быть недостаточными для управления входами КМПД-элементов. Для усиления этих токов и согласования уровней используется преобразователь уровней.

могут быть недостаточными для управления входами КМПД-элементов. Для усиления этих токов и согласования уровней используется преобразователь уровней.

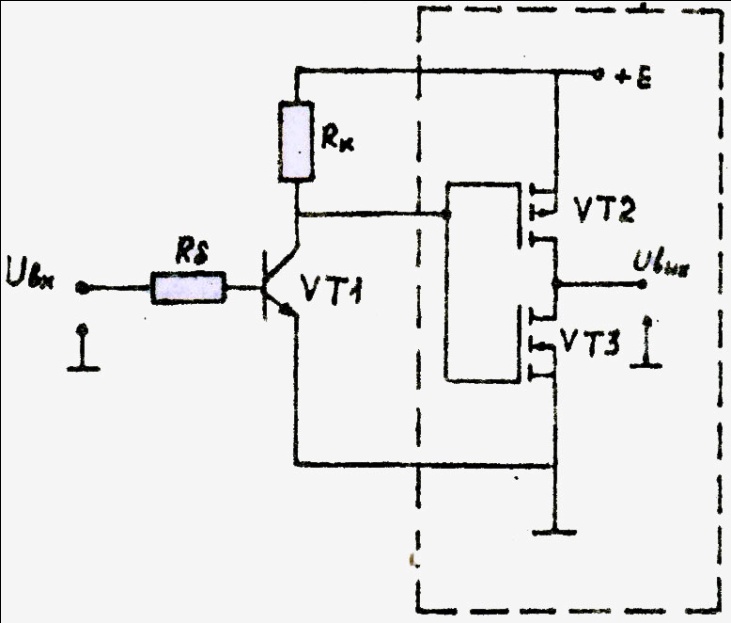

Рис.13. Схема преобразователей уровня ТТЛ-типа в КМДП-типа

Схема ПУ работает следующим образом:

При Uвх = U°ттл транзистор VT1 находится в отсечке, и на выходе первого каскада U= +E. Транзистор VT2 заперт, а VТ3 открыт, на выходе схемы Uвых = 0 < U°кмдп.

При Uвx — U1ттл транзистор VT2 отпирается до насыщения благодаря базовому току, равному (Uвх — e0б)/Rб> где eоб — напряжение на р—n-переходе Б—Э насыщенного транзистора (для кремниевых транзисторов еоб0,6 В). Остаточное напряжение между коллектором и эмиттером насыщенного транзистора близко к нулю и транзистор VT2 открыт, a VT3 заперт. Следовательно, Uвых = + E >Uкмдп.

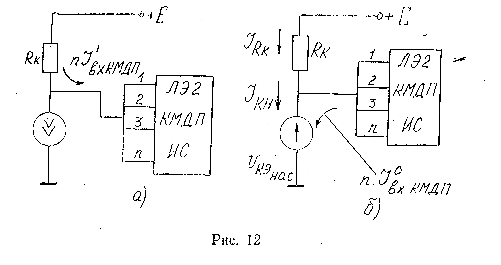

Рис.14. Режимы работы преобразователей уровней.

ЕслиUих= Uттл

, то VT находится в режиме отсечки (рис.14, а), и напряжение на его коллекторе, равное напряжению на выходе ПУ, не должно быть меньше уровня логической 1 КМПД – элементов , т. е.

, то VT находится в режиме отсечки (рис.14, а), и напряжение на его коллекторе, равное напряжению на выходе ПУ, не должно быть меньше уровня логической 1 КМПД – элементов , т. е.  :

:

где n — нагрузочная способность ПУ.

Если UBX=Uттл ,то целесообразно обеспечить насыщение транзистораVT со степенью насыщения 5=1,5÷2, т. е.

Ток Iб, протекающий в цепи базы транзистора VTпри условии, что UQX = U1ttji» равен

Вычисленный ток Iб не должен превышать выходной ток I] , обеспечиваемый ТТЛ - элементом в состоянии логической 1, а также должен быть меньше максимально допустимого тока /б макс выбранного транзистора VT, т. е.:

В коллектор насыщенного транзистора VT втекает ток Iкн который складывается из тока Iк, протекающего через резистор Rк, и я входных токов I°вхкмдп КМДП-элемента, т. е.

Ток Iкн, найденный должен быть меньше максимально допустимого тока Iкмакс выбранного транзистора VT, т. е.

Напряжение UBh]Xна выходе ПУ, равное потенциалу на коллекторе насыщенного транзистора VTUKэнне должно превышать уровня логического О КМДП элемента U°кмдп.

Статические свойства схемы ПУ наглядно отражаются ее передаточной характеристикой — зависимостью UBblx — f (UBX).

На передаточной характеристике рассматриваемой схемы ПУ можно выделить три участка.

Если Uвх<еоб, то VTнаходится в режиме отсечки и1/ви определяется.

Если UBX> еоб ,то VTоткрыт и ток базы определяется пока VTработает в активном режиме.

Расчёт преобразователя уровней ТТЛ КМПД проводится с использованием выражений:

а) Зависимость обратного тока от температуры окружающей среды:

, где T – температура, при которой определяют ток

, где T – температура, при которой определяют ток  ;

; - значение тока

- значение тока  , при некоторой исходной температуре

, при некоторой исходной температуре  , которое приводится в справочнике;

, которое приводится в справочнике; - температура удвоения, при которой ток

- температура удвоения, при которой ток  удваивается (для кремния

удваивается (для кремния  );

);б) Первое ограничение сверху, накладываемое на

:

:  ;

;в) Второе ограничение сверху, накладываемое на

:

:  ,

,где

=1 мГц- заданная частота переключения; Сн=n*Свх+См – емкость нагрузки; n=2;

=1 мГц- заданная частота переключения; Сн=n*Свх+См – емкость нагрузки; n=2;Свх= 11 пФ – входная ёмкость элемента К561ЛА7; См = 50 пФ – емкость монтажа.

г

) Ограничение, накладываемое на

) Ограничение, накладываемое на  максимальным током коллектора используемого биполярного транзистора:

максимальным током коллектора используемого биполярного транзистора:3.5 Выбор биполярного транзистора.

Для преобразователя уровней выбираем биполярный транзистор КТ361А.

3.6 Расчёт схемы преобразователя уровней в заданном температурном диапазоне и выбор номиналов резисторов.

Выбор номинала резистора

.

. Если на входе ПУ уровень логического "0" элемента K1533ЛA1: UВХ=U0ТТЛ

= 0,4 В, то транзистор КТ503А, выполняющий в ПУ функции VT, находится в отсечке, т.к. UВХ

Из неравенства для наихудшего соотношения параметров определяем первое ограничение сверху на величину Rк

.

. ,

,где Е = 10 В – 0,5 В = 9,5 В – минимальное напряжение питания при допуске 5%

U1КМДП = U1ВЫХ КМДП= 7,2 В – уровень логической «1» на выходе элемента К561ЛА7.

n = 2 – нагрузочная способность

I1вхкмдп, Iко - максимальные значения входного тока элемента К176ЛА7 и обратного тока коллектора транзистора КТ361А.

Для нахождения

воспользуемся выражением:

воспользуемся выражением: ,

,где Т*- температура удвоения при которой обратный ток

удваивается (Т*≈6оС для кремния);

удваивается (Т*≈6оС для кремния); - значение тока при некоторой исходной температуре;

- значение тока при некоторой исходной температуре;Т- температура, при которой измеряют ток Io.

Подставив значения, получим первое ограничение сверху на величину Rк:

Второе ограничение сверху на величину Rк из условия:

,

,где

=1 мГц- заданная частота переключения; Сн=n*Свх+См – емкость нагрузки; n=2;

=1 мГц- заданная частота переключения; Сн=n*Свх+См – емкость нагрузки; n=2;Свх= 11 пФ – входная ёмкость элемента К561ЛА7; См = 50 пФ – емкость монтажа.

Подставив значения, получим второе ограничение сверху на величину Rк:

Из неравенства для наихудшего соотношения параметров определяем ограничение снизу на величину Rк

.

. ,

,где Е = 10 В + 0,5 В = 10,5 В – максимальное напряжение питания при допуске 5%

UКЭ НАС = 0,2 В – напряжение насыщения коллектор-эмиттер транзистора КТ503А

n = 2 – нагрузочная способность

IКМАХ =0,15 А – максимально допустимый ток транзистора КТ361А

I0ВХКМДП - максимальные значения входного тока элемента К176ЛА7

Для нахождения

воспользуемся выражением:

воспользуемся выражением:

Подставив значения, получим ограничение снизу на величину Rк:

Таким образом, получили двусторонние ограничения на величину сопротивления Rк

С точки зрения уменьшения мощности, потребляемой ПУ необходимо выбрать величину

наибольшей, удовлетворяющей двухстороннее ограничение и в соответствии со стандартным рядом номиналов резистора

наибольшей, удовлетворяющей двухстороннее ограничение и в соответствии со стандартным рядом номиналов резистора .

.Выбираем величину сопротивления резистора

=6 кОм ± 5%.

=6 кОм ± 5%.Выбор номинала резистора

.

.Из неравенств получим первое и второе ограничение снизу на величину

;

;  ,

,где

= 2,4 В- уровень логической «1» на выходе элемента К1533ЛА1

= 2,4 В- уровень логической «1» на выходе элемента К1533ЛА1 = 0,8 В – напряжение насыщения база-эмиттер транзистора КТ361А

= 0,8 В – напряжение насыщения база-эмиттер транзистора КТ361А = 0,04 А – выходной ток логической «1» элемента К1533ЛА1

= 0,04 А – выходной ток логической «1» элемента К1533ЛА1 = 0,1 А – максимально допустимый ток базы транзистора КТ361А

= 0,1 А – максимально допустимый ток базы транзистора КТ361АПодставив значения, получим ограничение снизу на величину

:

: ;

;

Для определения ограничения сверху на величину

потребуем, чтобы для выбранного транзистора КТ503А обеспечивалась бы степень насыщения S =1,5.

потребуем, чтобы для выбранного транзистора КТ503А обеспечивалась бы степень насыщения S =1,5.Из неравенства для наихудшего соотношения параметров определяем соотношение сверху на величину

:

: ,

,где β = 40 – минимальное значение статического коэффициента передачи тока в схеме с общим эмиттером транзистора КТ361А

=6 кОм – 0,3 кОм = 5,7 кОм – минимальное сопротивление резистора

=6 кОм – 0,3 кОм = 5,7 кОм – минимальное сопротивление резистора при допуске 5%

при допуске 5% = 2,4 В

= 2,4 В = 0,2 В

= 0,2 ВЕ = 10,5 В

Подставив значения, получим ограничение сверху на величину

:

:

Таким образом, мы получаем двухстороннее ограничение на величину сопротивления

:

: 40 Ом;

40 Ом;  16 Ом;

16 Ом;  ≤ 23,6кОм

≤ 23,6кОмС точки зрения обеспечения требуемой степени насыщения S = 1,5 транзистора VT необходимо выбрать величину

наибольшей, удовлетворяющей двухстороннее ограничение и в соответствии со стандартным рядом номиналов резистора.

наибольшей, удовлетворяющей двухстороннее ограничение и в соответствии со стандартным рядом номиналов резистора.Выбираем величину сопротивления резистора

=22кОм ± 5%.

=22кОм ± 5%.Расчёт мощности, потребляемой преобразователем уровней от источника питания.

Мощность, потребляемая ПУ от источников питания E в состоянии логической «1» на выходе для наихудшего соотношения параметров определяется выражением:

Где: Е = 10,5 В; n = 2;

= 0,3 мкА;

= 0,3 мкА;  = 1 мкА.

= 1 мкА.Подставив значения, получим:

Мощность потребляемая ПУ от источника питания Е в состоянии логического «0» на выходе для наихудшего соотношения параметров определяется выражением:

,

,где Е = 10,5 В; n = 2;

=0,2 В,

=0,2 В,  = 5,7 кОм,

= 5,7 кОм,  = 0,3 мкА.

= 0,3 мкА.Подставив значения, получим:

.

.Расчёт передаточной характеристики преобразователя уровней

для номинальных параметров и

для номинальных параметров и  .

.На характеристике преобразователя уровней

можно выделить 3 участка. Таким образом, используя расчётные данные, вычислим необходимые для построения характеристики величины:

можно выделить 3 участка. Таким образом, используя расчётные данные, вычислим необходимые для построения характеристики величины:Так как

, то:

, то:

Заключение

В курсовом проекте разработан АЦП последовательного приближения с К572 ПВ1 на основе микросхем отечественного производства.

Произведены расчеты преобразователя уровней, его потребляемой мощности, построена передаточная характеристика.

Литература

Волович Г.И. Схемотехника аналоговых и аналого-цифровых устройств.-М.: Додэка хх1, 2007.

Интегральные микросхемы и их зарубежные аналоги. Справочник. Т.3,4,5.-М.: Радиософт, 2008.

Микросхемы ЦАП и АЦП. Справочник+СД.-М.: Додэка хх1,2008.

Миловзоров О.В. Электроника. Гриф МО РФ.-М.: Высшая школа, 2008.

Наундорф У. Аналоговая электроника. Основы, расчет, моделирование.-М.: Техносфера,2008.

Прянишников В.А. Электроника. Полный курс лекций. –СПб.: Корона принт, 2004.

Титце У., Шенк К. Полупроводниковая схемотехника: В 2-х томах.-М.:Додэка хх1,2008.

Ю.А. Мячин Справочник. 180 аналоговых микросхем.-М.:1993.

1 2

устанавливается низкий уровень, на выходах 1-12 – высокий уровень. На выходе окончания преобразования Р появляется высокий уровень. Такое состояние триггера будет сохраняться до тех пор, пока на входе ER удерживается низкий уровень.

устанавливается низкий уровень, на выходах 1-12 – высокий уровень. На выходе окончания преобразования Р появляется высокий уровень. Такое состояние триггера будет сохраняться до тех пор, пока на входе ER удерживается низкий уровень.