Лаба ЦУМП 2. Ход работы Интегральные схемы серии 74xx. Дешифратор

Скачать 3.85 Mb. Скачать 3.85 Mb.

|

|

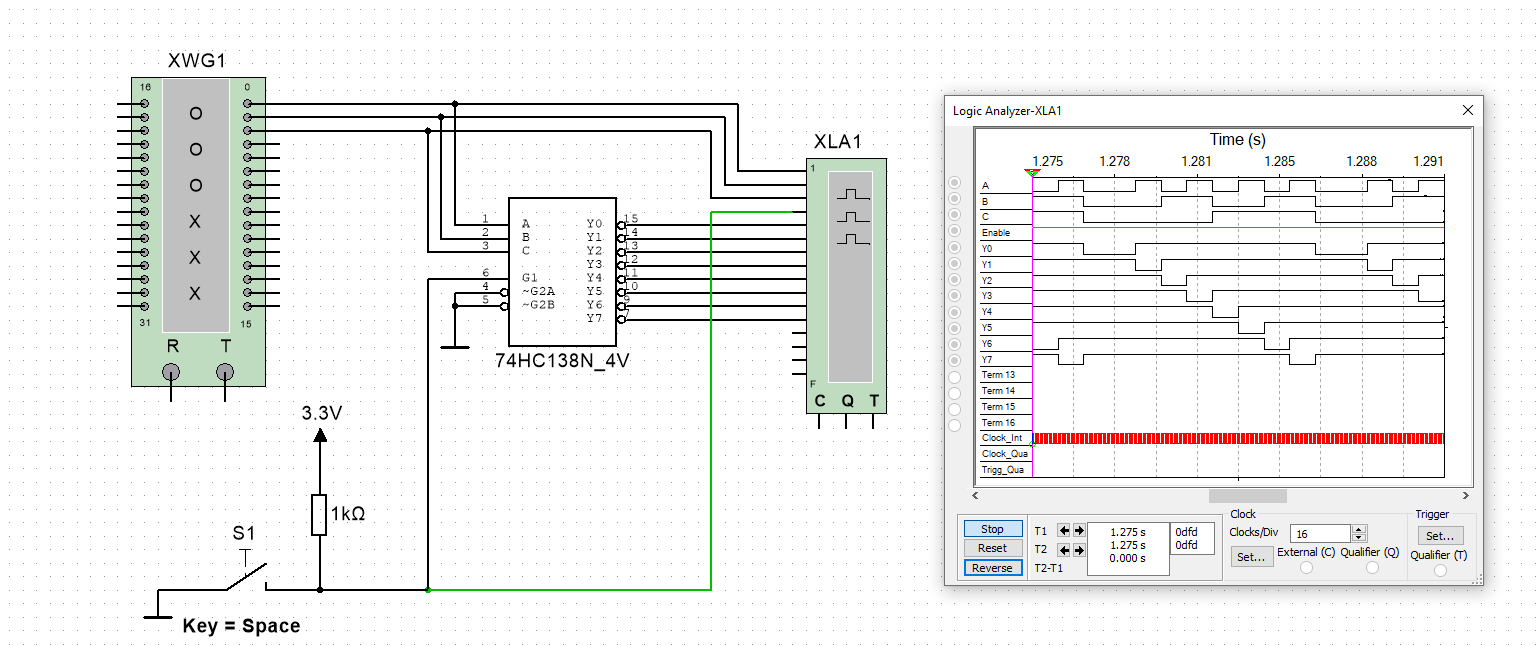

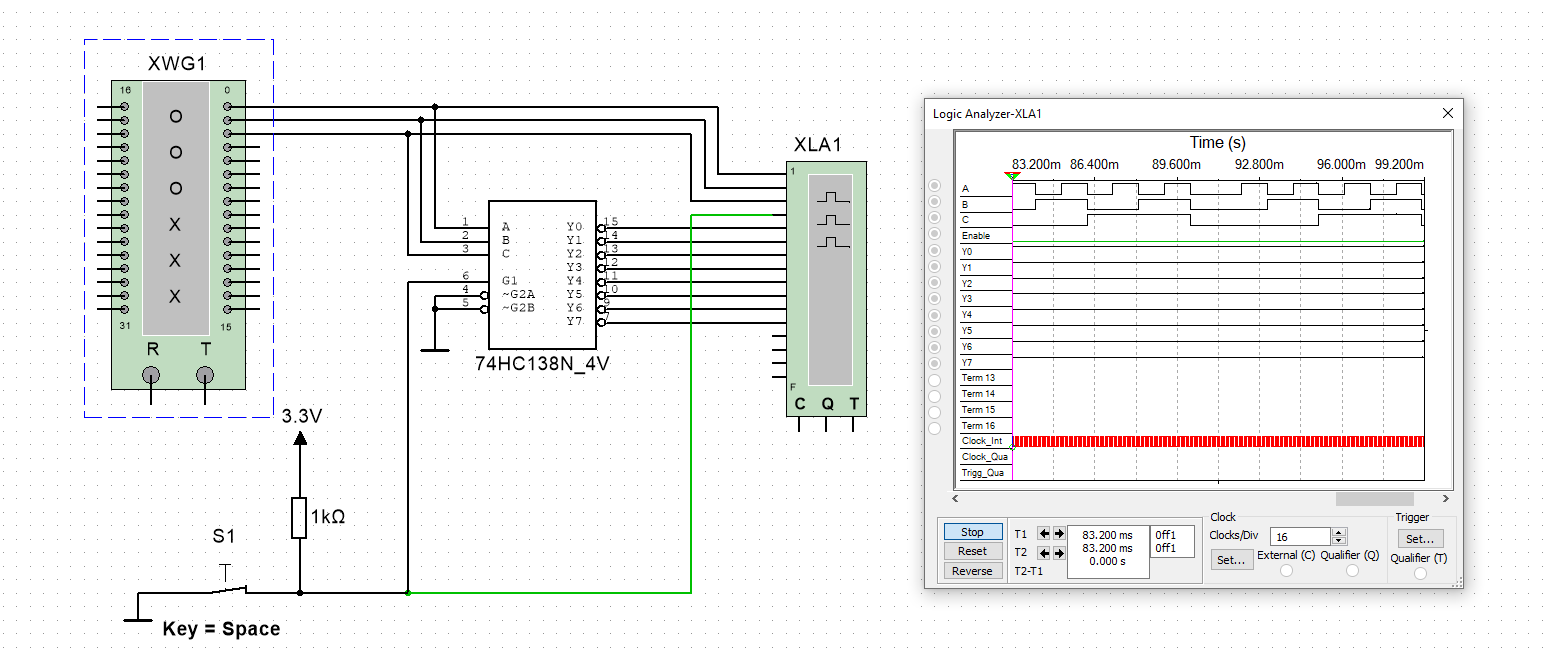

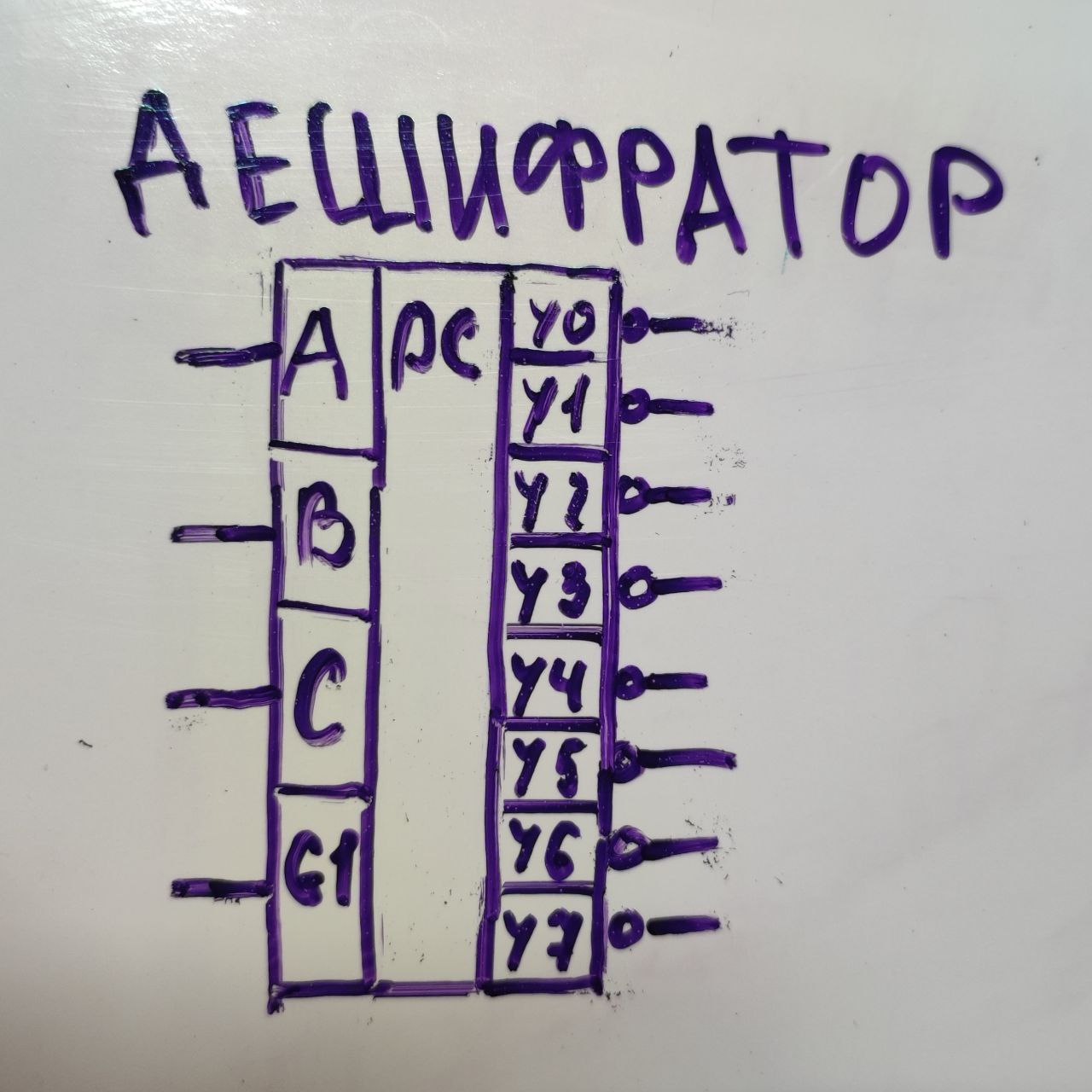

Ход работы Интегральные схемы серии 74xx. Дешифратор. Мы запустили схему и сняли с неё показатели входных и выходных данных (Рис. 1).  Рис. 1 На схеме представлены генератор слов (XWG1), дешифратор и логический анализатор для вывода графического представления данных, высокоомный резистор для препятствия току, а также ключ и земля. На Рис.1 ключ разомкнут, поэтому мы наблюдаем сигнал на выходе. Затем мы замкнули ключ на выход и получили картинку входных и выходных данных (Рис. 2)  Рис. 2 При замкнутом ключе на выход (Y0-Y7) ничего не поступает, так как весь ток уходит на землю. Затем мы показали, как выглядит дешифратор в соответствии с ГОСТ (ЕСКД) (рис. 3), а также нарисовали таблицу истинности для него (таблица 1).  Рис. 3 Таблица 1

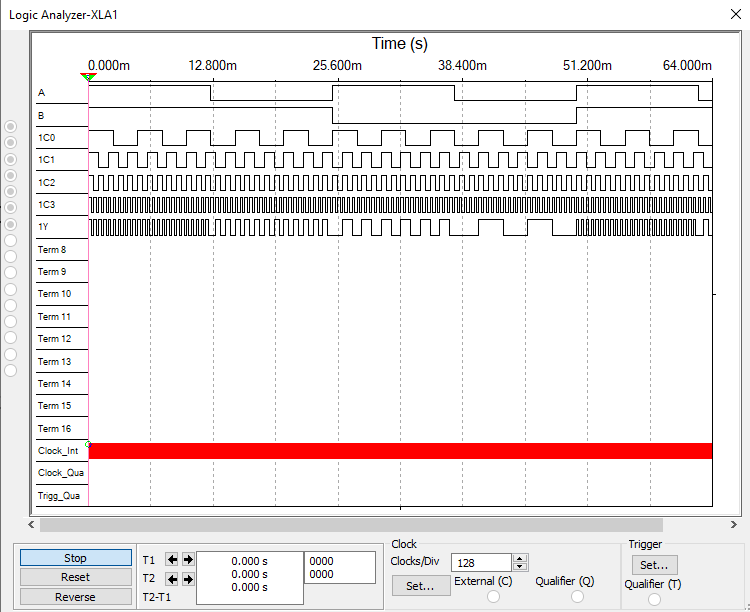

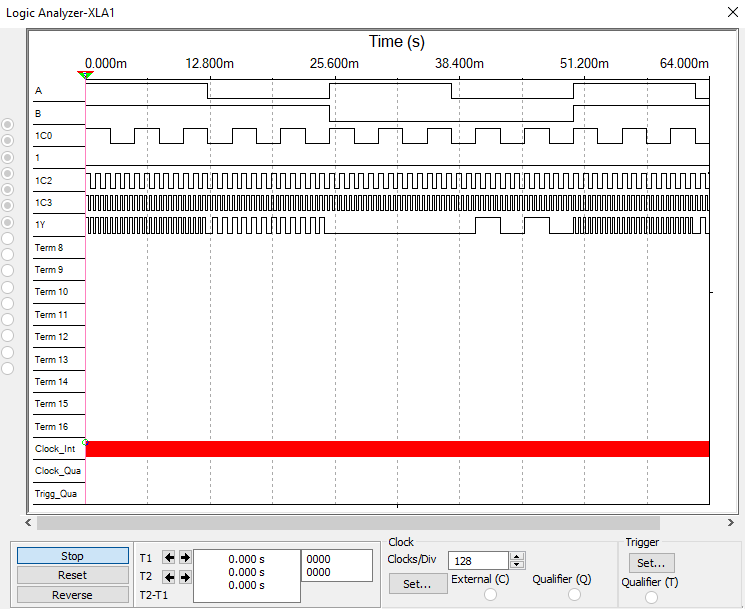

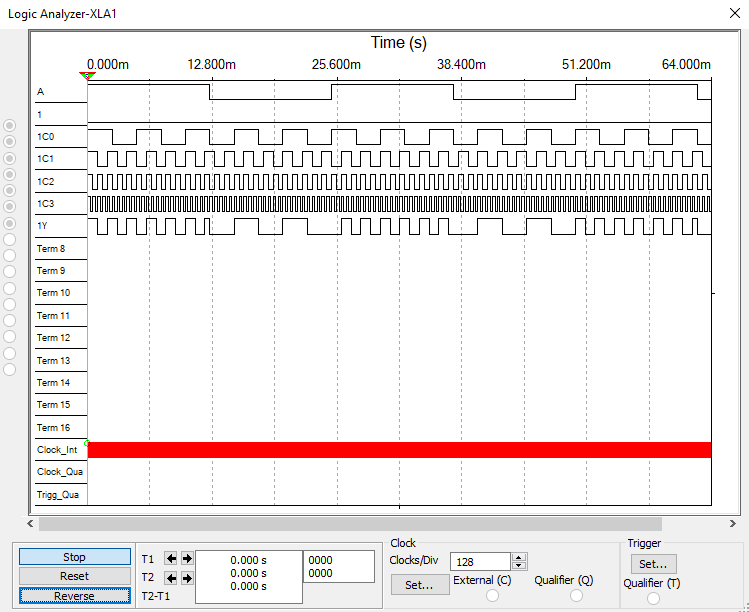

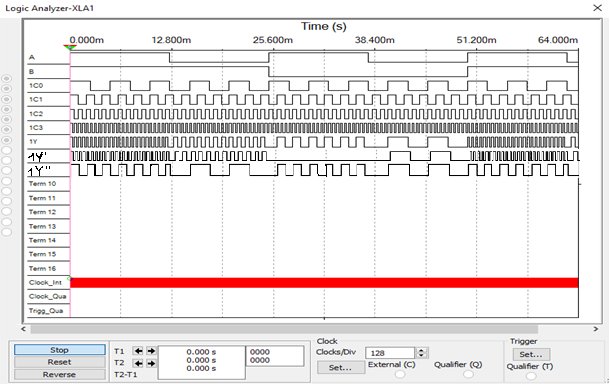

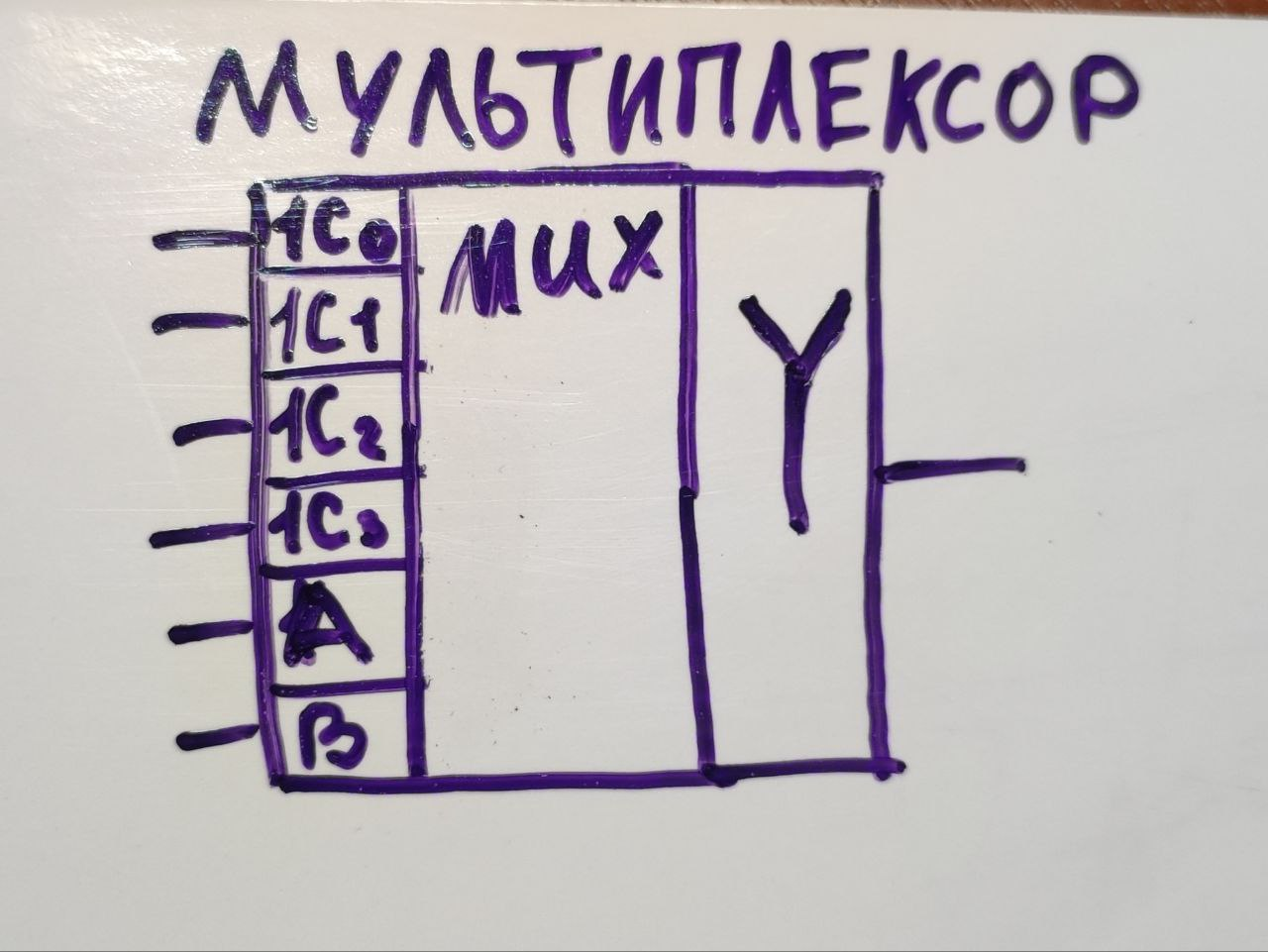

Интегральные схемы серии 74хх. Мультиплексор. Мы запустили схему, содержащую 6 генераторов сигнала, мультиплексор и анализатор сигналов (Рис. 4).  Рис. 4 Выходные данные с анализатора представлены на Рис. 5  Рис. 5 Согласно заданию, мы удалили второй генератор, который соответствует выходу 1C1 (Рис. 6).  Рис. 6 Затем мы вернули второй генератор и удалили другой, который отвечает за вход B, и получили следующие выходные данные (Рис. 7).  Рис. 7 Затем мы получили диаграммы для всех полученных сигналов при случаях удаления 1C1(1Y’) и B(1Y’’) (рис. 8)  Рис. 8 Нарисовали таблицу истинности и схему мультиплексора по ГОСТу (Рис. 9) Таблица 2:

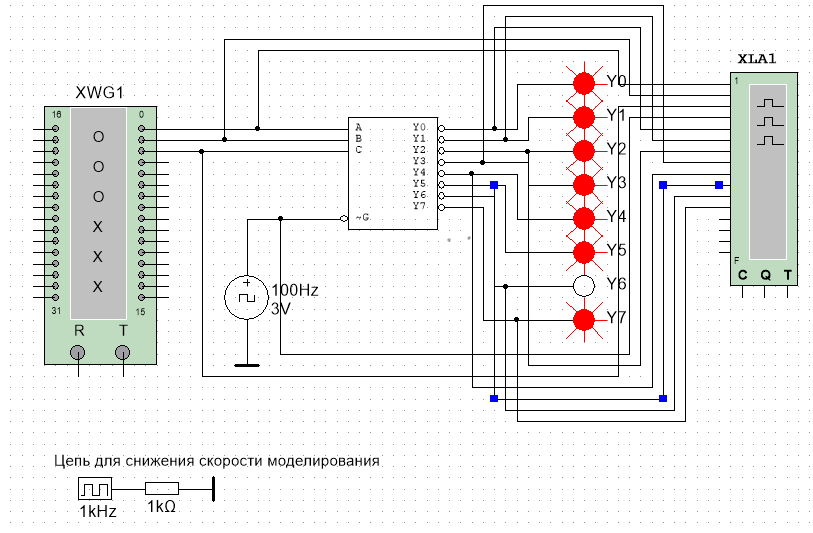

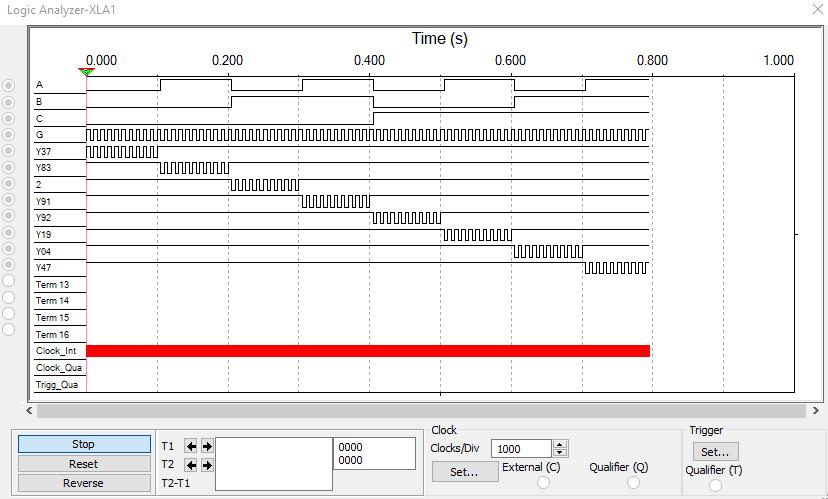

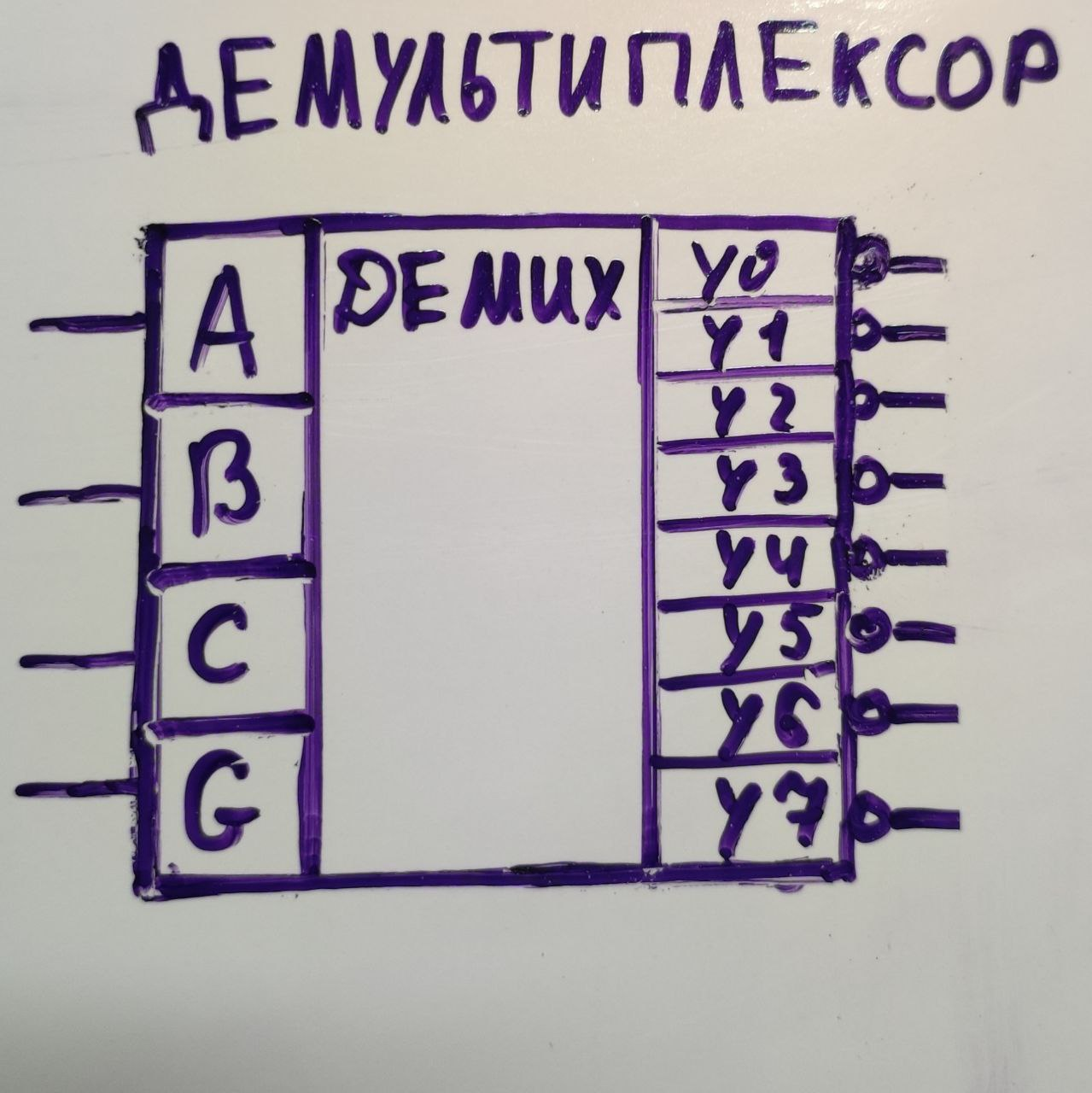

Рис. 9 Исследование демультиплексора Мы запустили схему, содержащую генератор сигнала, демультиплексор, генератор слов (XWG1) и логический анализатор (Рис. 10)  Рис. 10 Получили выходную картинку с логического анализатора (Рис. 11)  Рис. 11 Затем мы нарисовали по ГОСТ (ЕСКД) демультиплексор (Рис. 12) и его таблицу истинности.  Рис. 12 Таблица 3

Исследование приоритетного шифратора Мы построили схему приоритетного шифратора, который выводит сигнал с большим значением (Рис. 13)  Рис. 13 Затем мы построили таблицу истинности приоритетного шифратора (Рис. 14)  Рис. 14 Исследование сумматора Мы запустили схему сумматора и относительно своего варианта выбрали числа A и B, затем сложили их без учёта знака и с их учётом. Вариант 4  Рис. 15 – Схема сумматора Относительно полученных данных мы построили таблицу 4 Таблица 4

|