Исследование дешифраторов. Исследование дешифраторов" по курсу "Электроника и микропроцессорная техника (часть 2)"

Скачать 181.6 Kb. Скачать 181.6 Kb.

|

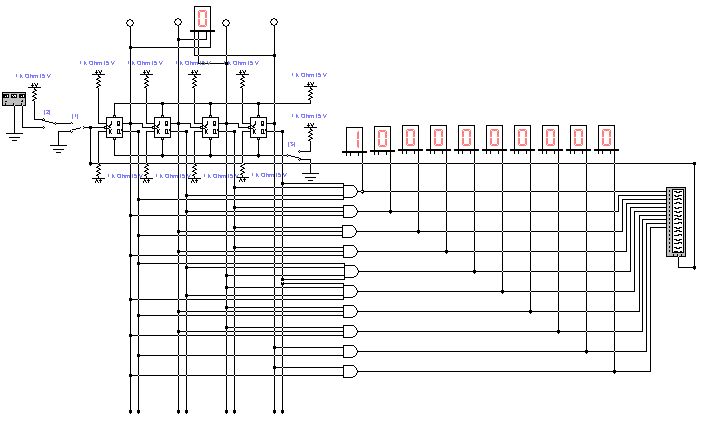

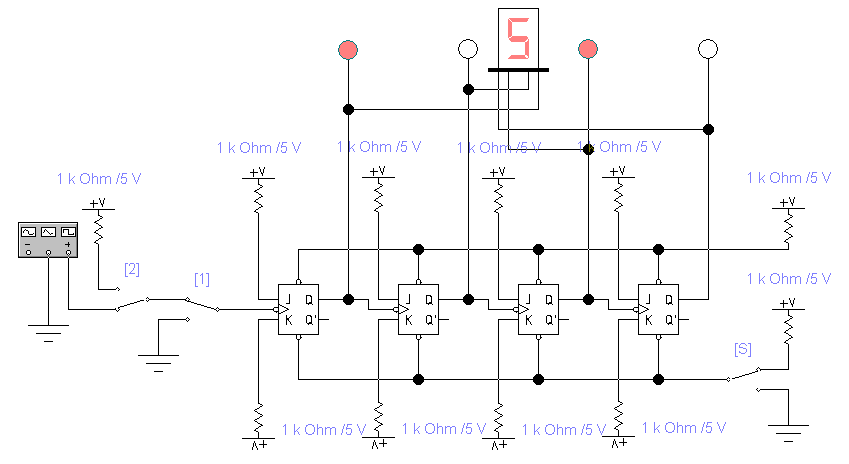

Д-кода) с весами 5-2-1-1 определяется системой логических функций:          Последующие пункты Задания 1 будем выполнять с использованием пакета для схемотехнического моделирования Electronics Workbench v. 5.12. Схема 1. Линейный дешифратор Д-кода на элементах НЕ и И.  Схема 2. Четырехразрядный счетчик на JK-триггерах.  Таблица 5. Таблица истинности JK-триггера.

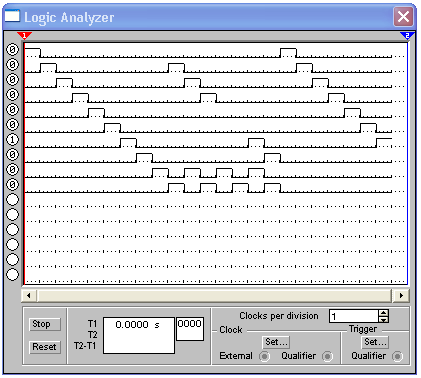

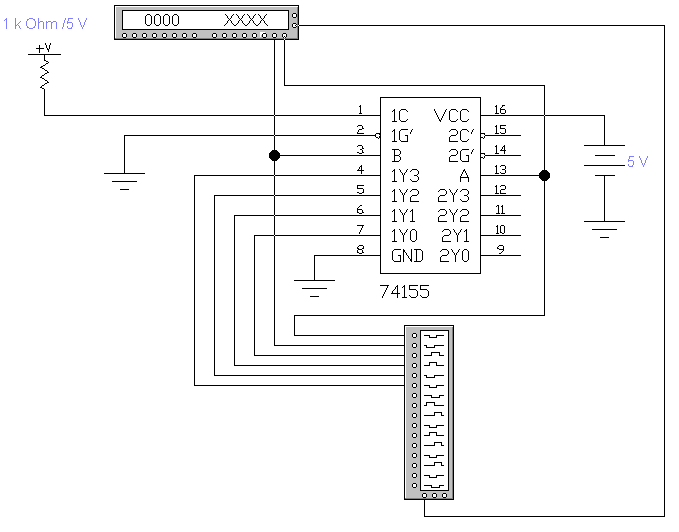

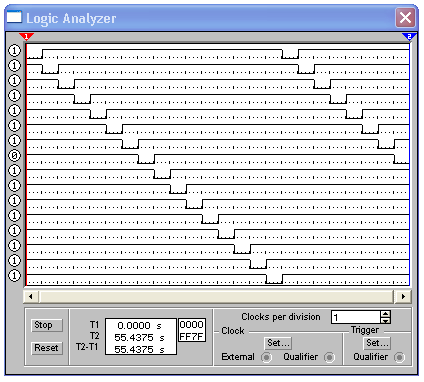

В счетном T-триггере используется только четвертая строка Таблицы 5. Для этого входы J и K присоединяются к потенциалу, соответствующему логической единице:  . В момент среза тактового импульса триггер переключается на противоположное состояние . В момент среза тактового импульса триггер переключается на противоположное состояние  . Таким образом, счетный триггер имеет единственный тактовый вход, который обозначается T. Частота повторения сигнала Q вдвое меньше, чем частота повторения импульсов T, т. е. T-триггер делит частоту импульсов на 2. Счетные триггеры широко применяются в счетчиках, распределителях и делителях частоты, а также в различных переключателях. Для реализации счетного триггера обычно пользуются ИМС JK-триггера, входы J и K которого соединяют с источником питания. . Таким образом, счетный триггер имеет единственный тактовый вход, который обозначается T. Частота повторения сигнала Q вдвое меньше, чем частота повторения импульсов T, т. е. T-триггер делит частоту импульсов на 2. Счетные триггеры широко применяются в счетчиках, распределителях и делителях частоты, а также в различных переключателях. Для реализации счетного триггера обычно пользуются ИМС JK-триггера, входы J и K которого соединяют с источником питания.Счетчики импульсов позволяют подсчитать количество поступающих на вход импульсов. Результат счета в них записывается в двоичном коде. Максимальное число N, которое может быть записано в счетчике, равно (2n-1), где n – число разрядов счетчика. Каждый разряд счетчика включает в себя триггер. Наиболее проста схема счетчика на синхронных T-триггерах. На Схеме 2 показана схема четырехразрядного счетчика на сложение. Он осуществляет счет импульсов от 0 до 15. Число N может быть увеличено при подключении к выходу счетчика дополнительных разрядов. Первый триггер счетчика образует младший разряд, сигнал A0 поступает на вход второго разряда, выходное напряжение которого подается на вход третьего разряда и т. д. Рассмотри функционирование счетчика. Пусть в схеме подачей сигналов на установочные входы всех триггеров установлено исходное состояние  . Срезом входных импульсов T переключается триггер младшего разряда счетчика. Срезом напряжения A0 переключается триггер второго разряда счетчика. Срез сигнала A1 вызывает переключение триггера третьего разряда. . Срезом входных импульсов T переключается триггер младшего разряда счетчика. Срезом напряжения A0 переключается триггер второго разряда счетчика. Срез сигнала A1 вызывает переключение триггера третьего разряда.Нетрудно видеть, что состояние разрядов представляет собой запись числа поступивших импульсов в двоичном коде. После записи максимального числа N счетчик автоматически обнуляется, т. е. устанавливается  . При поступлении дальнейших импульсов начинается новый цикл счета. Частота повторения выходного сигнала в i-ом разряде в 2i раза меньше частоты повторения импульсов T. . При поступлении дальнейших импульсов начинается новый цикл счета. Частота повторения выходного сигнала в i-ом разряде в 2i раза меньше частоты повторения импульсов T. Временные диаграммы сигналов дешифратора:  На основании временных диаграмм выходных сигналов можно сделать вывод о соответствии работы дешифратора его таблице истинности. 3. Исследование дешифраторов ИМС К155ИД4: а) снять временные диаграммы двухвходового дешифратора, подавая на его адресные входы сигналы Q0 и Q1 с выходов счетчика, а на стробирующие входы E1 и E2 – импульсы, СИ-1, задержанные линией задержки макета; б) определить время задержки стробирующего сигнала, необходимое для исключения помех на выходах дешифратора; в) собрать схему трехвходового дешифратора на основе дешифратора К155ИД4, задавая входные сигналы A0, A1, A2 с выходов Q0, Q1, Q2 счетчика; снять временные диаграммы сигналов дешифратора и составить по ней таблицу истинности. Схема 3. Исследование дешифратора ИМС К155ИД4 (74155 – К155ИД4 – 2 дешифратора-мультиплексора 2x4).  Временные диаграммы входных и выходных сигналов дешифратора ИМС К155ИД4.  Составим по временным диаграммам таблицу истинности дешифратора. Таблица 6. Таблица истинности дешифратора ИМС К155ИД4.

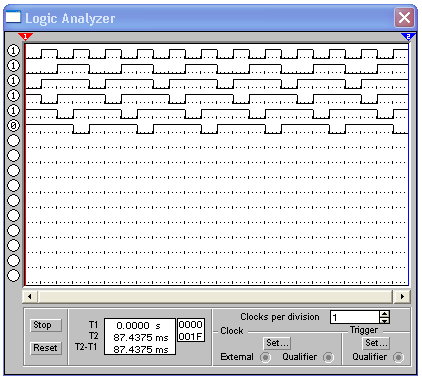

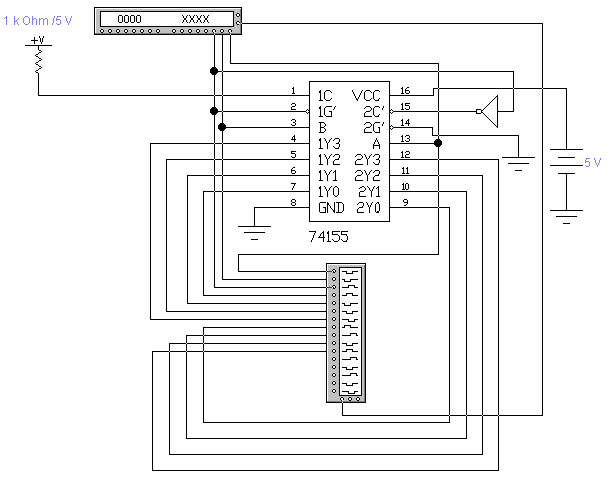

Схема 4. Схема трехвходового дешифратора на основе дешифратора К155ИД4.  Временные диаграммы входных и выходных сигналов трехвходового дешифратора на основе дешифратора К155ИД4.  Составим по временным диаграммам таблицу истинности дешифратора. Таблица 7. Таблица истинности трехвходового дешифратора на основе дешифратора К155ИД4.

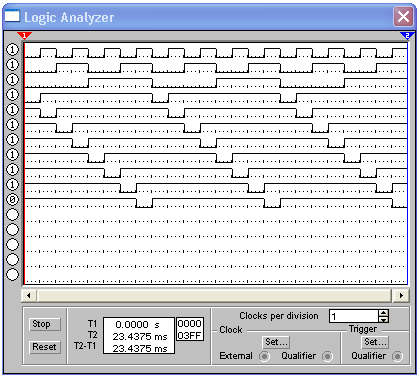

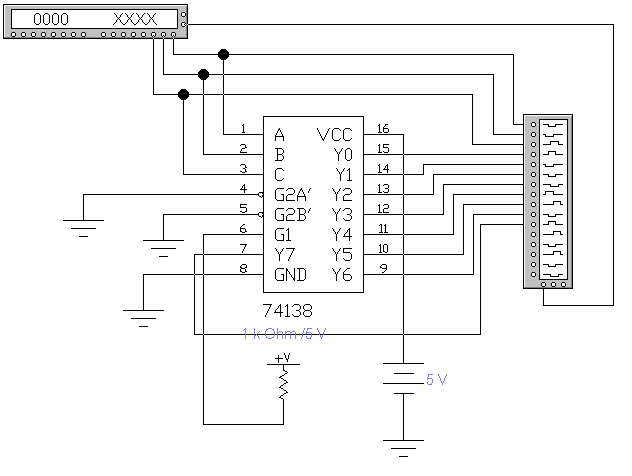

Схема 5. Исследование дешифратора ИМС К155ИД7 (ИМС 74138 – К155ИД7 – дешифратор-демультиплексор 3x8).  Временные диаграммы входных и выходных сигналов дешифратора ИМС К155ИД7.  Составим по временным диаграммам таблицу истинности дешифратора. Таблица 8. Таблица истинности дешифратора ИМС К155ИД7.

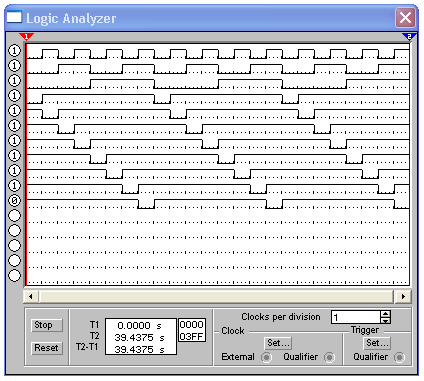

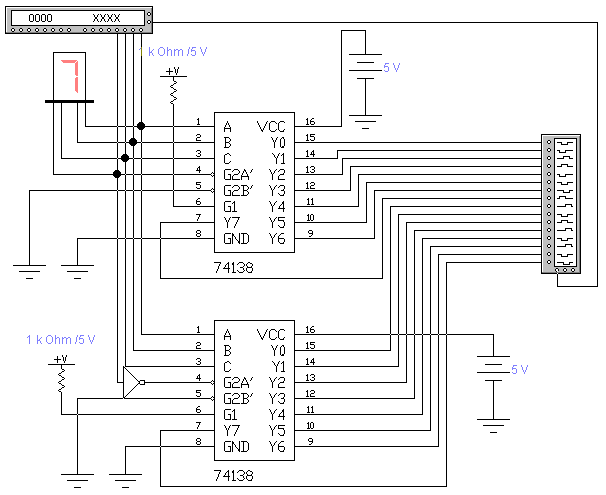

Схема 6. Схема четырехвходового дешифратора на основе дешифратора К155ИД7.  Временные диаграммы входных и выходных сигналов четырехвходового дешифратора на основе дешифратора К155ИД7.  Составим по временным диаграммам таблицу истинности дешифратора. Таблица 9. Таблица истинности четырехвходового дешифратора на основе дешифратора К155ИД7.

Контрольные вопросы. 1. Что называется дешифратором? 2. Какой дешифратор называется полным (неполным)? 3. Определите закон функционирования дешифратора аналитически и таблично. 4. Поясните основные способы построения дешифраторов. 5. Что называется гонками и как они устраняются? 6. Каковы способы наращивания дешифраторов по количеству входов и выходов и как они реализуются схемотехнически? 7. Объясните схему включения дешифратора-демультиплексора. 8. Поясните методику синтеза неполных дешифраторов. Ответы. 1. Дешифратором называется комбинационный узел, преобразующий каждый набор двоичных входных сигналов в информационный сигнал на выходе, соответствующий этому набору. 2. Число выходов дешифратора равно числу разрешенных наборов входных сигналов. В дешифраторе с | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||