Исследование дешифраторов. Исследование дешифраторов" по курсу "Электроника и микропроцессорная техника (часть 2)"

Скачать 181.6 Kb. Скачать 181.6 Kb.

|

n входами и K выходами  . .Дешифратор, имеющий  выхода, называется полным, при меньшем числе выходов – неполным. выхода, называется полным, при меньшем числе выходов – неполным.3. Функционирование дешифратора описывается системой логических функций:  (1) (1)где  – входные переменные (сигналы); – входные переменные (сигналы); – выходы дешифратора. – выходы дешифратора.Для  система функций (1) имеет следующий вид: система функций (1) имеет следующий вид: (2) (2)Функционирование дешифратора поясняется Таблицей 10. Таблица 10. Табличное определение закона функционирования трехвходового дешифратора.

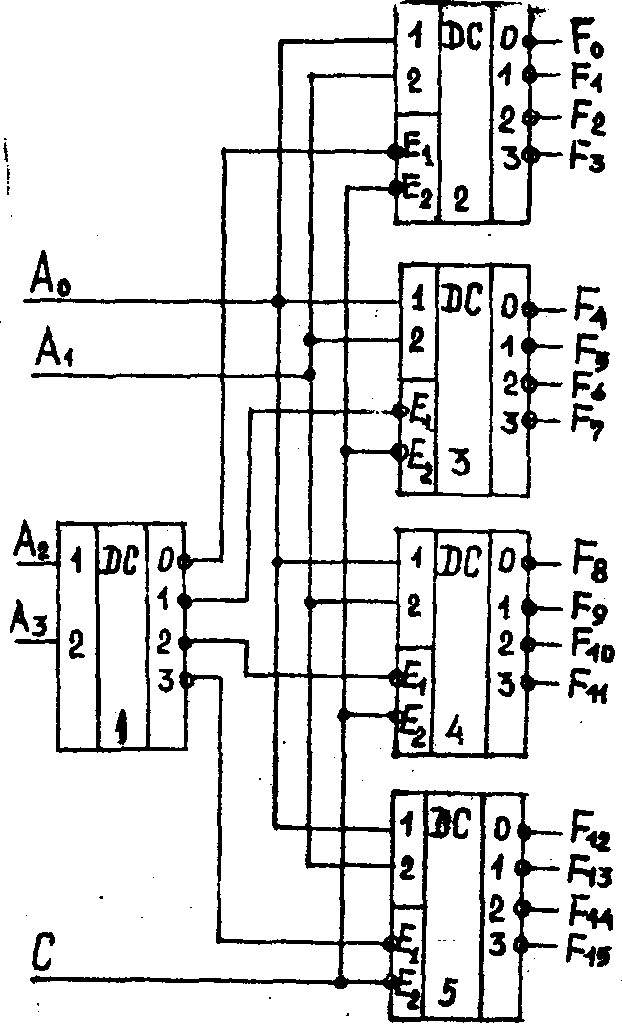

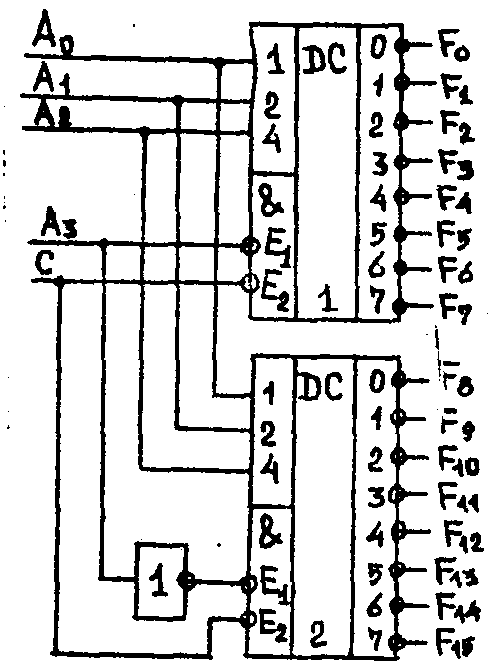

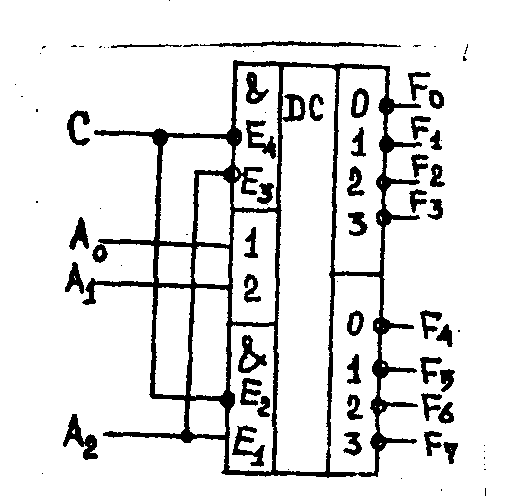

4. Существует три основных способа построения дешифратора: линейный; пирамидальный; ступенчатый. Линейный дешифратор строится непосредственно в соответствии с системой функций (1) и состоит из  конъюнкторов с конъюнкторов с  входами каждый. входами каждый.Пирамидальный дешифратор строится на основе последовательной (каскадной реализации выходных функций). На первом этапе реализуется конъюнкция двух переменных:  , ,  , ,  , ,  . .На втором – все конъюнкции трех переменных путем логического умножения каждой ранее полученной конъюнкции двух переменных на переменную  : : , ,  , ,  , ,  , , , ,  , ,  , ,  . .На третьем этапе каждую из полученных выше конъюнкций трех переменных умножают на  и т. д. Таким образом, на каждом последующем этапе получают вдвое больше конъюнкций, чем на предыдущем. и т. д. Таким образом, на каждом последующем этапе получают вдвое больше конъюнкций, чем на предыдущем.Пирамидальные дешифраторы независимо от числа их входов строятся на основе двухвходовых конъюнкторов. Величина коэффициента разветвления конъюнктора по выходу равна двум. Ступенчатый дешифратор строится на основе двух дешифраторов на  и и  входов и входов и  двухвходовых конъюнкторов. Если двухвходовых конъюнкторов. Если  – четное, то – четное, то  , при нечетном , при нечетном  величины величины  и и  отличаются на единицу: отличаются на единицу: , ,  . .При большом числе входов  ступенчатые дешифраторы имеют существенно меньшие аппаратурные затраты, чем линейные и пирамидальные. ступенчатые дешифраторы имеют существенно меньшие аппаратурные затраты, чем линейные и пирамидальные.5. Гонки (состязания) – появление ложных сигналов на выходах схемы вследствие переходных процессов и временных задержек сигналов в цепях логических элементов. Основным средством, позволяющим исключить гонки, является стробирование (выделение из информационного сигнала той части, которая свободна от искажений). 6. Для наращивания по количеству входов и выходов используется стробирующий вход. На рис. 1. приведена схема ступенчатого дешифратора с двумя E-входами. При этом один стробирующий вход используется для наращивания дешифратора, а второй – для стробирования выходной ступени. При увеличении числа входов на единицу получим схему, показанную на рис. 2. ИМС К155ИД4 – сдвоенный дешифратор с общими адресными входами A0, A1. Первый дешифратор имеет прямой E1 и инверсный E2 стробирующие входа, второй – два инверсных входа E3 и E4. При наращивании дешифратора объединенные входы E1 и E3 являются адресным входом A2, а объединенные стробирующие входы E2 и E4 – входом стробирования (рис.3). 7. Дешифратор-демультиплексор. Стробируемый дешифратор может выполнять функцию демультиплексирования, т. е. передавать сигналы (поступающие на стробирующий вход) на выход, номер которого задается входными сигналами. Поэтому  – сигналы и входы, на которые они поступают, называются также адресными. – сигналы и входы, на которые они поступают, называются также адресными.8. Дешифратор двоично-десятичного кода (Д-кода) имеет 4 входа и 10 выходов, т. е. является неполным. Неиспользуемые, т. е. запрещенные наборы входных сигналов используются для минимизации системы функций. Минимизируя функции  , можно получить все выходные функции. Затем на основе системы минимизированных функций строится линейный дешифратор. Подробнее о методике синтеза неполных дешифраторов см. выполнение Задания 2 настоящей лабораторной работы. , можно получить все выходные функции. Затем на основе системы минимизированных функций строится линейный дешифратор. Подробнее о методике синтеза неполных дешифраторов см. выполнение Задания 2 настоящей лабораторной работы.   Рис. 1. Рис. 2. Рис. 3. - - | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||