светофор. Исследование модели модулей Разработка интерфейса и архитектуры модулей

Скачать 2.58 Mb. Скачать 2.58 Mb.

|

|

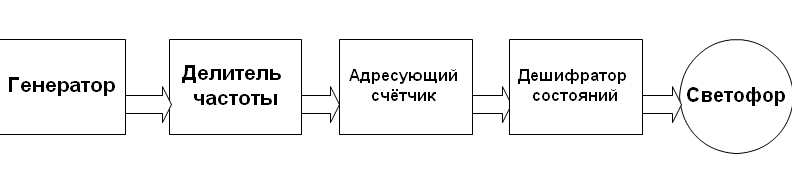

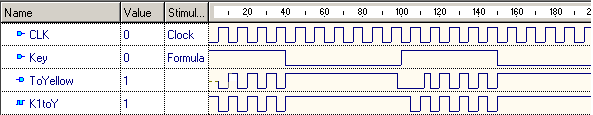

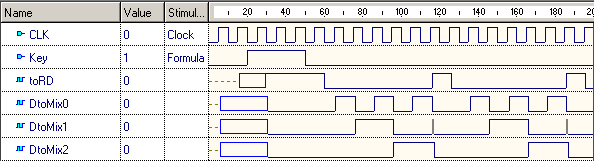

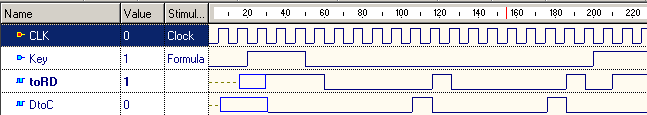

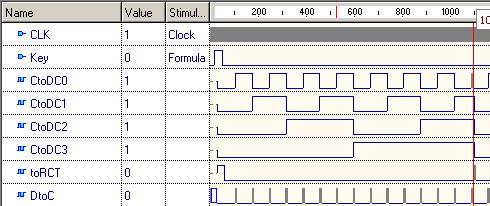

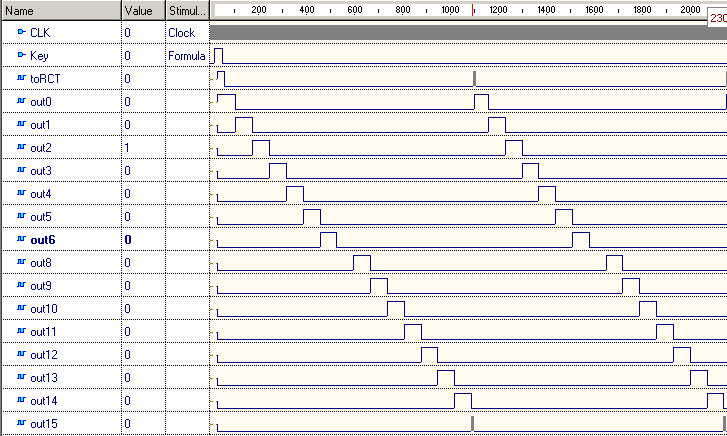

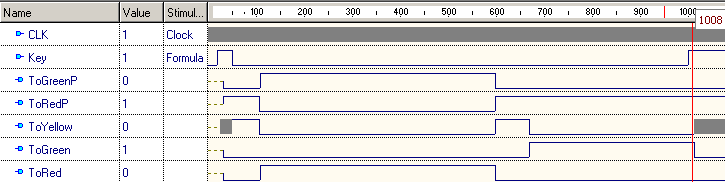

Содержание Введение 1. Теоретическая часть 2. Построение структурной схемы 3. Разработка и исследование модели модулей Разработка интерфейса и архитектуры модулей Разработка модели дешифратора 4 х 16 х 1 бит Разработка модели двоичного счётчика со сбросом Разработка элемента обработки сигнала для жёлтого света Разработка элемента обработки сигнала для зелёного света Разработка элемента обработки сигнала для красного света пешеходу Разработка элемента обработки сигнала для красного света Разработка элемента превращения счётчика в делитель частоты на 5 Исследование работы моделей модулей 4. Исследование структурной модели устройства в целом с использованием моделей узлов 5. Анализ пригодности разработанных моделей для имплементации в PLD Заключение Введение В нашей жизни нас сплошь окружают цифровые автоматы, хотя мы этого можем даже не замечать. Одним из таких автоматов является объект, с которым мы сталкиваемся каждый день – это дорожный светофор. Светофор представляет собой практически идеальный объект для автоматизации, при программировании которого (аппаратном или программном) могут быть использованы автоматы. Для светофоров, как и для других объектов управления, документация является закрытой, но создание данного цифрового автомата является решаемой задачей, что и показано в данной курсовой работе. При выполнении данного проекта при помощи графа состояний и триггеров, а затем в аппаратном виде - он может служить наглядным пособием по дисциплине «Прикладная Теория Цифровых Автоматов (ПТЦА)»! Но так как задача разработчика состоит в том, чтобы выбрать наиболее оптимальное решение для данного проекта, то в этой курсовой работе предложено другое решение, основанное на программируемой логике. Теоретическая часть Рассмотрим дорожный светофор, один из четырёх светофоров обычно стоящих на переходе. Он двухсторонний, одна сторона обращена к водителям, а другая к пешеходам. Сторона обращённая к пешеходам имеет 2 света: красный и зелёный, а к водителям – три: красный, жёлтый и зелёный. Кроме того для водителя некоторое время перед сменой состояния мигает зелёный свет. Следовательно автомат управления светофором имеет 5 состояний, определённых для водителя, и 2 состояния, определённых для пешехода. Эти состояния можно наглядно представить в виде графов приведённых на рис. 1 и рис. 2.  Рис. 1. Граф состояний светофора для водителя  Рис. 2. Граф состояний светофора для пешехода Также светофор можно перевести в мигание, то есть неработающее состояние – светофор мигает жёлтым светом и должен интерпретироваться участниками дорожного движения как неработающий Построение структурной схемы По техническому заданию светофор имеет как статические так и динамические состояния – мигание, поэтому воспользуемся генераторам сигналов. Затем для получения кратных интервалов времени для включения света используем делитель частоты, затем последовательно включаем счётчик для адресации дешифратора. А от дешифратора, после обработки, выходные сигналы вызывают зажигание необходимого света. Структурная схема приведена на рис 3.  Рис. 3. Структурная схема управления светофором. Схема работает следующим образом. Генератор частоты создаёт прямоугольные импульсы с заданной частотой. Затем они используются в делителе, а также для мигания зелёного и жёлтого света. Делитель на 5, основанный на счётчике типа К155ИЕ7 – выдаёт кратный сигнал на счётчик адресующий – перебирающий адреса на дешифраторе. Дешифратор поочерёдно подаёт “1” на каждый из выходов, объединив эти выводы в группы мы тем самым получили необходимую продолжительность горения каждого из цветов. Также при подаче входного сигнала на ключ – светофор включается или выключается (нормальный режим или мигание жёлтого света). Выводы схемы подсоединим к индикаторам (диоды или лампы). 3. Разработка и исследование модели модулей Разработка интерфейса и архитектуры модулей Разработка модели дешифратора 4 х 16 х 1 бит entity DEC416 is port ( A3,A2,A1,A0 : in std_logic ; Z7,Z6,Z5,Z4,Z3,Z2,Z1,Z0 : out std_logic ; Z15,Z14,Z13,Z12,Z11,Z10,Z9,Z8 : out std_logic ) ; end DEC416 ; architecture dc1 of DEC416 is begin process(A3,A2,A1,A0) begin Z15 <= A3 and A2 and A1 and A0 after 1 ns ; Z14 <= A3 and A2 and A1 and (not A0) after 1 ns ; Z13 <= A3 and A2 and (not A1) and A0 after 1 ns ; Z12 <= A3 and A2 and (not A1) and (not A0) after 1 ns ; Z11 <= A3 and (not A2) and A1 and A0 after 1 ns ; Z10 <= A3 and (not A2) and A1 and (not A0) after 1 ns ; Z9 <= A3 and (not A2) and (not A1) and A0 after 1 ns ; Z8 <= A3 and (not A2) and (not A1) and (not A0) after 1 ns ; Z7 <= (not A3) and A2 and A1 and A0 after 1 ns ; Z6 <= (not A3) and A2 and A1 and (not A0) after 1 ns ; Z5 <= (not A3) and A2 and (not A1) and A0 after 1 ns ; Z4 <= (not A3) and A2 and (not A1) and (not A0) after 1 ns ; Z3 <= (not A3) and (not A2) and A1 and A0 after 1 ns ; Z2 <= (not A3) and (not A2) and A1 and (not A0) after 1 ns ; Z1 <= (not A3) and (not A2) and (not A1) and A0 after 1 ns ; Z0 <= (not A3) and (not A2) and (not A1) and (not A0) after 1 ns ; end process ; end dc1 ; Разработка модели двоичного счётчика со сбросом library ieee ; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all; entity CNTB4UR is port( CLK,RST : in std_logic; Q3,Q2,Q1,Q0 : out std_logic ) ; end CNTB4UR ; architecture v1 of CNTB4UR is signal count_i : unsigned (3 downto 0); begin process(CLK,RST,count_i) begin if (RST='1') then count_i <= x"0" ; elsif (CLK = '1' and CLK'event) then count_i <= count_i + "1" ; end if; end process; Q3 <= count_i(3) after 1 ns ; Q2 <= count_i(2) after 1 ns ; Q1 <= count_i(1) after 1 ns ; Q0 <= count_i(0) after 1 ns ; end v1; Разработка элемента обработки сигнала для жёлтого света library ieee ; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all; entity Ylw is port (In0, In8, K1: in std_logic; OnYlw: out std_logic ); end Ylw; architecture ye1 of Ylw is begin process(In0,In8,K1) begin OnYlw<=(In0 or In8) and K1; end process; end ye1; Разработка элемента обработки сигнала для зелёного света library ieee ; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all; entity Green is port (In9, In10, In11, In12, In13, In14, In15, CLK: in std_logic; OnGreen: out std_logic); end green; Architecture g1 of Green is begin process(In9, In10, In11, In12, In13, In14, In15, CLK) begin OnGreen<=In9 or In10 or In11 or In12 or In13 or In14 or (In15 and CLK); end process; end g1; Разработка элемента обработки сигнала для красного света пешеходу library ieee ; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all; entity OR4 is port ( IN0,IN8,green,IN15 : in std_logic ; OnRedP : out std_logic ) ; end OR4 ; architecture v1 of OR4 is begin process(IN0,IN8,green,IN15) begin OnRedP <= IN0 or IN8 or IN15 or green; end process; end v1 ; Разработка элемента обработки сигнала для красного света library ieee ; use ieee.std_logic_1164.all ; entity OR7 is port ( IN6,IN5,IN4,IN3,IN2,IN1,IN0 : in std_logic ; Z : out std_logic ) ; end OR7 ; architecture v1 of OR7 is begin Z <= IN6 or IN5 or IN4 or IN3 or IN2 or IN1 or IN0 after 1 ns ; end v1 ; Разработка элемента превращения счётчика в делитель частоты на 5 library ieee ; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all; entity AND3B1 is port ( IN2,IN1,IN0 : in std_logic ; del5 : out std_logic ) ; end AND3B1 ; architecture v1 of AND3B1 is begin del5 <= IN2 and IN0 and (not IN1); end v1 ; Исследование работы моделей модулей Исследование работоспособности моделей проводилось с помощью анализа временных диаграмм сигналов. Задавая входное возмущение, производится анализ соответствующих ему выходных сигналов. По таблице соответствий выносится заключение о работоспособности модели. Ниже приведены временные диаграммы, полученные по каждому из модулей. В идеальном случае при тестировании модели необходимо подать все возможные входные комбинации и проанализировать выходные возмущения. Однако не всегда это является возможным и оправданным, на практике выбирается множество тестовых комбинаций описывающих основные свойства разрабатываемой модели  Рис. 4. Временная диаграмма элемента обработки сигнала для жёлтого света. Видно что имеются 2 состояния: рабочее и нерабочее, задаваемое KEY.  Рис. 5. Временная диаграмма счётчика Используются 3 выхода, при этом мы обязательно должны произвести первоначальный сброс системы, т.к. первоначальное состояние счётчика- неопределённость. Видно что счётчик работоспособен и соответствует требованиям.  Рис. 6. Временная диаграмма деления на 5.  Рис. 7. Временная диаграмма адресующего счётчика от 0 до 15.  Рис. 8. Временная диаграмма дешифратора 4х16.  Рис. 9. Временная диаграмма, полученная при анализе модели устройства Из полученных диаграмм можно сделать заключение о работоспособности отдельных модулей. 4. Исследование структурной модели устройства в целом с использованием моделей узлов Для построения модели устройства в целом используется структурное описание. При этом модель представляется в виде совокупности отдельных модулей описанных ранее и связей между ними. Это позволяет применить принцип декомпозиции, значительно упрощающий процесс разработки модели. В качестве внешних портов ввода-вывода устройства используются следующие: Входной тактовый сигнал; вход сброса и переключения состояний (Key); выход на жёлтый цвет; выход на красный цвет; выход на зелёный цвет; выход на красный цвет пешеходу; выход на зелёный цвет пешеходу; - Дополнительно при подготовке под прошивку добавлен выход адресации 7-сегментного индикатора “adres7” entity svet is port( CLK:in std_logic; Key: in std_logic; ToRed,ToGreen,ToYellow,ToRedP,ToGreenP:out std_logic ); end svet; Ниже приведен листинг, описывающий работу устройства. Так же используются некоторые простейшие логические элементы (и, или), их описание не приводилось в виду очевидности. library ieee ; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all; -- 4 to 16-bit Decoder -- Philips CPLD Applications -- Aug 26, 1998 entity DEC416 is port ( A3,A2,A1,A0 : in std_logic ; Z7,Z6,Z5,Z4,Z3,Z2,Z1,Z0 : out std_logic ; Z15,Z14,Z13,Z12,Z11,Z10,Z9,Z8 : out std_logic ) ; end DEC416 ; architecture dc1 of DEC416 is begin process(A3,A2,A1,A0) begin Z15 <= A3 and A2 and A1 and A0 after 1 ns ; Z14 <= A3 and A2 and A1 and (not A0) after 1 ns ; Z13 <= A3 and A2 and (not A1) and A0 after 1 ns ; Z12 <= A3 and A2 and (not A1) and (not A0) after 1 ns ; Z11 <= A3 and (not A2) and A1 and A0 after 1 ns ; Z10 <= A3 and (not A2) and A1 and (not A0) after 1 ns ; Z9 <= A3 and (not A2) and (not A1) and A0 after 1 ns ; Z8 <= A3 and (not A2) and (not A1) and (not A0) after 1 ns ; Z7 <= (not A3) and A2 and A1 and A0 after 1 ns ; Z6 <= (not A3) and A2 and A1 and (not A0) after 1 ns ; Z5 <= (not A3) and A2 and (not A1) and A0 after 1 ns ; Z4 <= (not A3) and A2 and (not A1) and (not A0) after 1 ns ; Z3 <= (not A3) and (not A2) and A1 and A0 after 1 ns ; Z2 <= (not A3) and (not A2) and A1 and (not A0) after 1 ns ; Z1 <= (not A3) and (not A2) and (not A1) and A0 after 1 ns ; Z0 <= (not A3) and (not A2) and (not A1) and (not A0) after 1 ns ; end process ; end dc1 ; -- 4-bit Binary Up Counter with asynchronous reset -- Philips CPLD Applications -- Aug 26,1998 library ieee ; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all; entity CNTB4UR is port( CLK,RST : in std_logic; Q3,Q2,Q1,Q0 : out std_logic ) ; end CNTB4UR ; architecture v1 of CNTB4UR is signal count_i : unsigned (3 downto 0); begin process(CLK,RST,count_i) begin if (RST='1') then count_i <= x"0" ; elsif (CLK = '1' and CLK'event) then count_i <= count_i + "1" ; end if; end process; Q3 <= count_i(3) after 1 ns ; Q2 <= count_i(2) after 1 ns ; Q1 <= count_i(1) after 1 ns ; Q0 <= count_i(0) after 1 ns ; end v1; --Жёлтый library ieee ; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all; entity Ylw is port (In0, In8, K1: in std_logic; OnYlw: out std_logic ); end Ylw; architecture ye1 of Ylw is begin process(In0,In8,K1) begin OnYlw<=(In0 or In8) and K1; end process; end ye1; --Зелёный library ieee ; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all; entity Green is port (In9, In10, In11, In12, In13, In14, In15, CLK: in std_logic; OnGreen: out std_logic); end green; Architecture g1 of Green is begin process(In9, In10, In11, In12, In13, In14, In15, CLK) begin OnGreen<=In9 or In10 or In11 or In12 or In13 or In14 or (In15 and CLK); end process; end g1; --Красный пешеходу -- 4-input OR -- Philips CPLD Applications -- Aug 26, 1998 library ieee ; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all; entity OR4 is port ( IN0,IN8,green,IN15 : in std_logic ; OnRedP : out std_logic ) ; end OR4 ; architecture v1 of OR4 is begin process(IN0,IN8,green,IN15) begin OnRedP <= IN0 or IN8 or IN15 or green; end process; end v1 ; -- 3-input AND with 1 input inverted -- Philips CPLD Applications -- Aug 26, 1998 library ieee ; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all; entity AND3B1 is port ( IN2,IN1,IN0 : in std_logic ; del5 : out std_logic ) ; end AND3B1 ; architecture v1 of AND3B1 is begin del5 <= IN2 and IN0 and (not IN1); end v1 ; -- 2-input AND -- Philips CPLD Applications -- Aug 26, 1998 library ieee ; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all; entity AND2 is port ( CLK,K : in std_logic ; K1 : out std_logic ) ; end AND2 ; architecture v1 of AND2 is begin K1 <= not(CLK and K); end v1 ; -- 2-input OR -- Philips CPLD Applications -- Aug 26, 1998 library ieee ; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all; entity OR2 is port ( IN1,IN0 : in std_logic ; Z : out std_logic ) ; end OR2 ; architecture v1 of OR2 is begin Z <= IN1 or IN0 after 10 ns; end v1; -- 7-input OR -- Philips CPLD Applications -- Aug 26, 1998 library ieee ; use ieee.std_logic_1164.all ; entity OR7 is port ( IN6,IN5,IN4,IN3,IN2,IN1,IN0 : in std_logic ; Z : out std_logic ) ; end OR7 ; architecture v1 of OR7 is begin Z <= IN6 or IN5 or IN4 or IN3 or IN2 or IN1 or IN0 after 1 ns ; end v1 ; library ieee ; use ieee.std_logic_1164.all ; use ieee.std_logic_arith.all; entity svet is port( CLK:in std_logic; Key: in std_logic; ToRed,ToGreen,ToYellow,ToRedP,ToGreenP:out std_logic ); end svet; architecture svt1 of svet is component OR7 is port ( IN6,IN5,IN4,IN3,IN2,IN1,IN0 : in std_logic ; Z : out std_logic ) ; end component ; component DEC416 port ( A3,A2,A1,A0 : in std_logic ; Z7,Z6,Z5,Z4,Z3,Z2,Z1,Z0 : out std_logic ; Z15,Z14,Z13,Z12,Z11,Z10,Z9,Z8 : out std_logic ) ; end component; component CNTB4UR is port( CLK,RST : in std_logic; Q3,Q2,Q1,Q0 : out std_logic ) ; end component ; component Ylw is port (In0, In8, K1: in std_logic; OnYlw: out std_logic ); end component; component Red is port (In1, In2, In3, In4, In5, In6, In7: in std_logic; OnRed: out std_logic); end component; component Green is port (In9, In10, In11, In12, In13, In14, In15, CLK: in std_logic; OnGreen: out std_logic); end component; component OR4 is port ( IN0,IN8,green,IN15 : in std_logic ; OnRedP : out std_logic ) ; end component ; component AND3B1 is port ( IN2,IN1,IN0 : in std_logic ; del5 : out std_logic ) ; end component ; component AND2 is port ( CLK,K : in std_logic ; K1 : out std_logic ) ; end component ; component OR2 is port ( IN1,IN0 : in std_logic ; Z : out std_logic ) ; end component ; signal CtoDC0, CtoDC1, CtoDC2, CtoDC3, toRCT:std_logic; signal toRD, z, DtoMix0, DtoMix1, DtoMix2, DtoC:std_logic; signal out0,out1,out2,out3,out4,out5,out6,out7,out8,out9,out10,out11,out12,out13,out14,out15: std_logic; signal K1toY, grtorp, tor :std_logic; begin m1:OR2 port map (In1=>Key, In0=>DtoC, Z=>toRD); m2:OR2 port map (In1=>out15, In0=>Key, Z=>toRCT); m3:CNTB4UR port map (CLK=>CLK, RST=>toRD, Q3=>z, Q2=>DtoMix2, Q1=>DtoMix1, Q0=>DtoMix0); m4:AND3B1 port map (IN2=>DtoMix2,IN1=>DtoMix1,IN0=>DtoMix0, del5=>DtoC); m5:CNTB4UR port map (CLK=>DtoC, RST=>toRCT, Q3=>CtoDC3, Q2=>CtoDC2, Q1=>CtoDC1, Q0=>CtoDC0); m6:AND2 port map (CLK=>CLK, K=>Key, K1=>K1toY); m7:DEC416 port map (A3=>CtoDC3, A2=>CtoDC2, A1=>CtoDC1, A0=>CtoDC0, Z15=>out15, Z14=>out14, Z13=>out13, Z12=>out12, Z11=>out11, Z10=>out10, Z9=>out9, Z8=>out8, Z7=>out7, Z6=>out6, Z5=>out5, Z4=>out4, Z3=>out3, Z2=>out2, Z1=>out1, Z0=>out0); m8:Ylw port map (In0=>out0, In8=>out8, K1=>K1toY, OnYlw=>ToYellow); m9:OR7 port map (IN1=>out1, IN2=>out2, IN3=>out3, IN4=>out4, IN5=>out5, IN6=>out6, IN0=>out7, Z=>tor); m10:Green port map (In9=>out9, In10=>out10, In11=>out11, In12=>out12, In13=>out13, In14=>out14, In15=>out15, CLK=>CLK, OnGreen=>grtorp); m11:OR4 port map (IN0=>out0, IN8=>out8, green=>grtorp,IN15=>out15, OnRedP=>ToRedP); ToGreen<=grtorp; ToRed<=tor; ToGreenP<=tor; end svt1; 5. Анализ пригодности разработанных моделей для имплементации в PLD При проектировании цифрового устройства, для последующего имплементации в PLD, появляется ряд дополнительных трудностей, связанных с невозможностью использования некоторых типов данных и языковых конструкций. Так же приходится учитывать особенности имплементации для ПМЛ разных фирм и устанавливаемые ограничения: максимальная частота, количество доступных элементов и т.д. Наиболее эффективным способом в этом случае является построение структурных моделей с использованием библиотек компонентов поставляемых производителем конкретного типа ПМЛ. В данной расчетно-графической работе этого было сделано, так как основной целью было – приобретение навыков построение моделей отдельных узлов и структурных моделей. В целом при построении моделей цифровых узлов не использовались запрещенные языковые конструкции и типы данных, также были учтены ограничения на количество доступных элементов памяти и максимальную частоту сигнала. Заключение В ходе выполнения работы была построена и исследована модель Цифровий автомат “Дорожний светлофор”. Модель построенна упрощённо по сравнению со схемотехническим решением, что обусловлено особенностями синтеза на VHDL. |