Лабораторная работа по дисциплине ВТиИТ. Исследование работы Шифраторов и Дешифраторов

Скачать 170.15 Kb. Скачать 170.15 Kb.

|

|

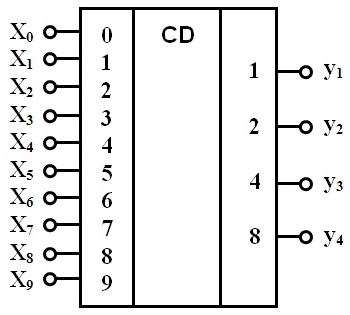

Министерство цифрового развития, связи и массовых коммуникаций Российской Федерации Уральский технический институт связи и информатики (филиал) ФГБОУ ВО «Сибирский государственный университет телекоммуникаций и информатики» в г. Екатеринбурге (УрТИСИ СибГУТИ) Кафедра Инфокоммуникационных технологий и мобильной связи Дисциплина (Вычислительная техника и информационные технологии) Отчёт по лабораторной работе №4 «Исследование работы Шифраторов и Дешифраторов» Выполнил студент гр. ИТ-01б Мельникова Е.А. Проверил Плеханов С.М. Екатеринбург 2022 г. 1 Цель работы: 1.1 Ознакомление с основными характеристиками интегральных преобразователей кодов: дешифраторов, шифратораторов. 2 Основное оборудование 2.1 Персональный компьютер 2.2 Программа NI Multisim 3 Вопросы для допуска к работе: 3.1 Какое комбинационное устройство называется шифратором? Шифратор – ЛУ выполняющий преобразование позиционного n-разрядного кода в m-разрядный двоичный, троичный или k-ичный код. 3.2 Нарисуйте условное графическое обозначение шифратора (рисунок 1).  Рисунок 1 - Условное графическое обозначение шифратора 3.3 Какой шифратор называется полным, а какой – неполным? Если шифратор использует все возможные комбинации на выходе, то такой шифратор называется полным, если не все, то неполный. Число входов и выходов в полном шифраторе связано отношением n=2m, где n – число входов, m – число выходных двоичных разрядов. 4 Задание для допуска к работе: 4.1 По таблице истинности шифратора (кодера) - таблица 1, составить для него систему уравнений. Таблица 1 – Таблицы истинности шифратора

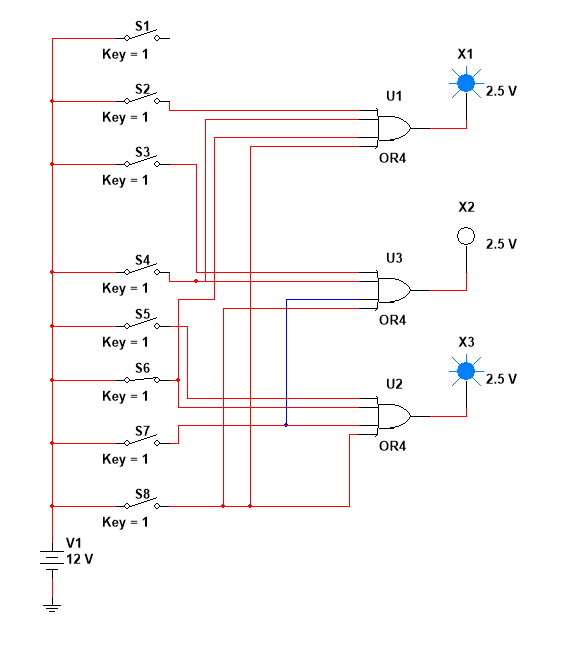

5 Порядок выполнения работы: 5.1 Построить 8-входовый шифратор на логических элементах «ИЛИ», составить его таблицу истинности (таблица 2). Исправить ошибки схемы (рисунок 2).  Рисунок 2 - Логическая схема 8-входовый шифратора Таблица 2 – Таблицы истинности 8-входового шифратора

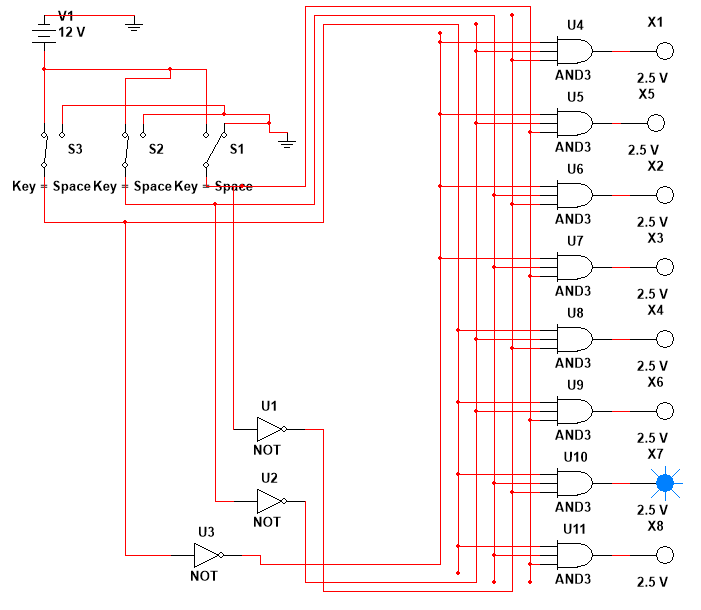

5.2 Собрать трехвходовый дешифратор на логических элементах «И» и «НЕ» (рисунок 3) и составить для него таблицу истинности (таблица 3).  Рисунок 3 - Логическая схема трехвходового дешифратора «И» и «НЕ» Таблица 3 – Таблицы трехвходового дешифратора «И» и «НЕ»

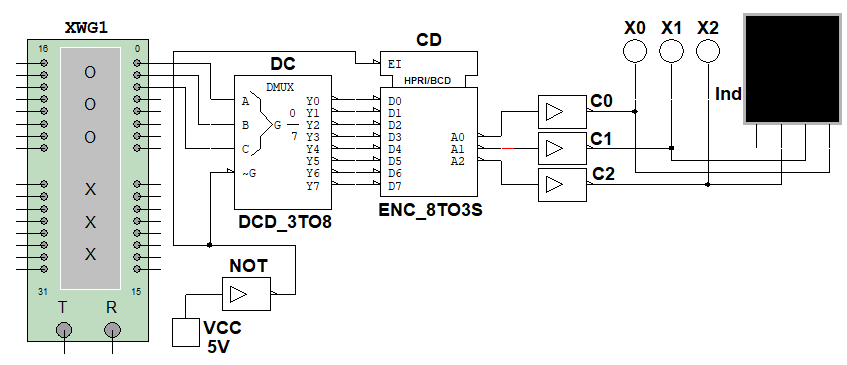

5.3 Изобразить схему для испытания интегрального шифратора CD 8х3 (рисунок 4) и составить для него таблицу истинности (таблица4). Содержимое ячеек памяти генератора слова XWG1: 000, 001, …, 111.  Рисунок 4 – Схема для исследования шифратора CD 8x3 Таблица 4 – Таблица интегрального шифратора CD 8х3

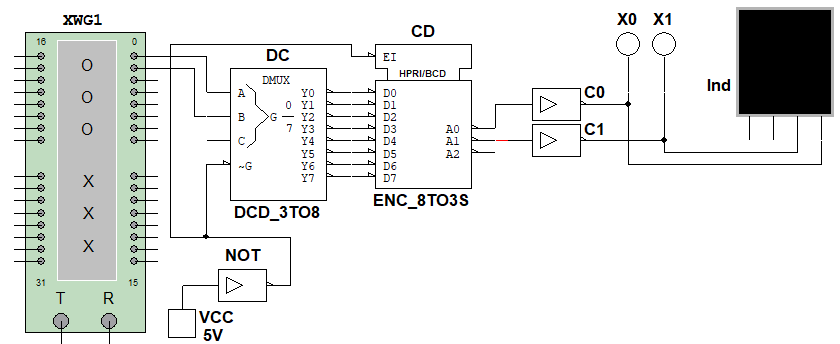

Преобразовать схему дешифратора DC 3х8 и шифратора CD 8х3 в схему DC 2х4 и шифратора CD 4х2, отсоединив провод С, подходящий к дешифратору, и провод A2 с выхода шифратора (рисунок 5), и составить таблицы переключений дешифратора 2х4 (таблица 5) и шифратора 4х2 (таблица 6).  Рисунок 5 – Схема для исследования шифратора CD 4x2 Таблица 5 – Таблица шифратора CD 2x4

Таблица 6 – Таблица шифратора CD 4x2

6 Выводы по проделанной работе: В ходе проделанной работы ознакомились с основными характеристиками интегральных преобразователей кодов: дешифраторов, шифратораторов. 7 Контрольные вопросы: 7.1 В каком случае возникает необходимость в применении шифраторов с приоритетом? Для обработки однопозиционных кодов (сигналов). В таких шифраторах код двоичного числа соответствует наивысшему номеру входа, на который подают сигнал «1», то есть на шифратор с приоритетом допускается подача сигналов на несколько входов, а на выходе выдаётся код числа, соответствующего старшему. 7.2 Объясните принцип действия шифратора. Шифратор работает следующим образом: шифратор имеет n входов, в текущий момент времени только на один, из которых подаётся сигнал (эго вход будет активным) по номеру активного входа на выходах дешифратора формируется двоичный вход, соответствующей позиции активного входа. Например, если активный был пятый вход, то на выходах будет комбинация (за исключением старших нулей): 510=1012. 7.3 Объясните принцип действия дешифратора. Обычно дешифратор имеет n-входов и 2n выходов, при этом n — разрядность дешифрируемого кода. Определенной комбинации на входе соответствует активный сигнал на одном из выходов, или при сигнале «00» — мы имеем «1» на нулевом выходе схемы; при «01» имеем — «1» на первом выходе, сигнал «10» трансформируется в 1 – на втором выходе и т.д. Другими словами, эти элементы схем могут преобразовывать двоичный код в различные системы исчисления (это может быть десятичная, шестнадцатеричная и пр.), поскольку все зависит от конкретной задачи, выполняемой микросхемой. В стандартные типы дешифраторов входят модели на 4, 8 и 16 выходов, при этом на выходе — 2, 3 и 4 разрядов входного кода. Входы дешифраторов называют часто адресными, и на схемах нумеруют 1,2,4,8, при этом цифра соответствует весу двоичного кода. Сигнал на выходе 1,2,4,8 устанавливает номер активного выхода. С1, С2 – входы разрешения (или стробирования), которые работают с условием «и». Сигнал на этом входе сообщает о моменте срабатывания дешифратора. Также их можно использовать для увеличения разрядности логических устройств. 7.4 При решении каких задач цифровой техники используется дешифратор? Эти устройства используются в цифровой технике для преобразования двоично-десятичного характера, применяющегося для управления индикаторными и летающими устройствами. 7.5 Где применяются шифраторы и дешифраторы? Эти устройства наиболее широко применяются в устройствах ввода и устройствах вывода информации. Например: клавиатура имеет шифратор, для преобразования языковых символом в двоичный код. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||