Конспект_СвСУ. Конспект лекций для студентов специальности 153 01 07 Информационные технологии и управление в технических системах

Скачать 8.24 Mb. Скачать 8.24 Mb.

|

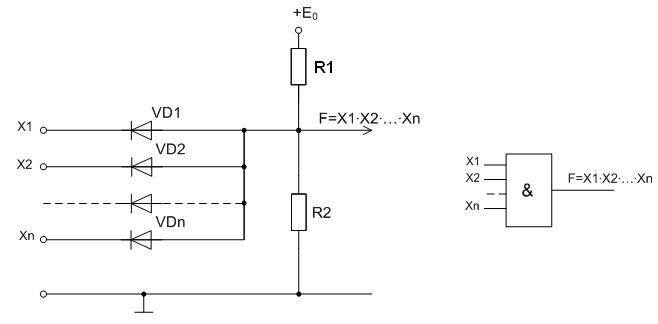

2.2 Диодные логические схемыЭто самые простые схемы, имеют наивысшую помехоустойчивость. Число входов в среднем достигает десяти. Нагрузкой обычно является один элемент. Имеется ввиду, что нагрузка – точно такой же ЛЭ. Малая нагрузочная способность потому, что эти схемы относятся к пассивным, нет усилителей мощности. Частотный диапазон невысокий (до 1 МГц), так как объединенные параллельные диодные входы эквивалентны объединению параллельных конденсаторов, которые заряжаются, разряжаются. На это необходимо время, снижается быстродействие. На рисунке 2.2 представлена диодно–логическая схема сложения. Возможны два состояния: 1 Входы соединены с землей через открытые выходы таких же логических схем. Иногда принимают это состояние эквивалентным соединению всех входов с землей посредством проводников. 2 Для того, чтобы открыть диоды необходимо подать напряжение, уровень которого в несколько раз больше зоны нечувствительности диодов. 5 В – минимальное стандартное напряжение, но оно может быть и 500 В и 5 кВ, если диоды высоковольтные. В этом случае и нагрузочная способность может быть больше единицы, но потребление схем становится большим.  Рисунок 2.2 – Диодно–логическая схема сложения Схема работает следующим образом. Принимаем, что на вход Х1 подается высокий уровень напряжения, который называется единицей. Этот уровень должен поступать с выхода точно такой же логической схемы, или каким–то другим способом, имитирующим те же условия. Но так как единица поступает только на вход Х1, то на остальных входах Х2…Хn должны быть нули. Они тоже должны быть организованы выходами таких же логических схем. В простейшем случае это могут быть проводники (перемычки), соединяющие входы Х2…Хn с землей. Следовательно, диод VD1 будет открыт, высокий уровень Х1 через VD1 проходит на выход, на котором выделяется также этот высокий уровень, из которого вычитается падение напряжения на диоде, т.е. на выходе будет уже меньший высокий уровень, тем не менее, его называют единицей. Диоды VD2… VDn в это время будут закрыты, так как на входах Х2…Хn низкие уровни, их барьерные емкости включены параллельно, накапливают заряд. Если теперь подать высокий уровень на вход Х2, то откроется VD2 но состояние выхода F почти не изменится, т.е. там сохраняется высокий уровень – единица. То же самое будет при подаче единицы на все входы одновременно. Таким образом, удовлетворяется операция логического сложения. Принцип двойственности состоит здесь в том, что если единицами назвать низкие уровни на входах и на выходе, то эта логическая схема сложения будет выполнять логическую операцию умножения (см. рисунок 2.2). Физический смысл заключается в том, что низкий уровень на выходе, который назван единицей, будет только в том случае, если на всех входах одновременно будут низкие уровни, которые тоже названы единицами. На рисунке 2.3 представлена диодная схема логического умножения. Если все диоды закрыты высокими уровнями (единицами), то ток протекает по цепи  . На выходе выделяется результат деления E0 между R1 и R2, который называется высоким уровнем. В том случае, когда на одном любом из входов низкий уровень, образованный такой же, другой диодной схемой, образуется цепь . На выходе выделяется результат деления E0 между R1 и R2, который называется высоким уровнем. В том случае, когда на одном любом из входов низкий уровень, образованный такой же, другой диодной схемой, образуется цепь  выход предыдущей логической схемы выход предыдущей логической схемы . Следовательно, на выходе F выделяется в сущности падение напряжения на VD1 и к нему добавляется падение напряжения на внутреннем сопротивлении такой же, но другой логической схемы, т. е. низкий уровень “0”, удовлетворяется операция логического умножения. . Следовательно, на выходе F выделяется в сущности падение напряжения на VD1 и к нему добавляется падение напряжения на внутреннем сопротивлении такой же, но другой логической схемы, т. е. низкий уровень “0”, удовлетворяется операция логического умножения. Рисунок 2.3 – Диодная схема логического умножения Принцип двойственности: Если низкий уровень на входе назвать единицей, то низкий уровень на выходе тоже единица будет в том случае, когда хотя бы на одном любом входе будет “1”. Широко применяется схема умножения в ИМС 533, 555 серии. 2.3 ТТЛ логические схемыТипичный представитель этих микросхем – 155 серия. Она уже не выпускается, но так как основные схемные решения те же, что и в более современных, отличие только в особенностях, то есть смысл, с учебной целью, начать рассмотрение именно этой логической схемы. Кстати, микросхемы 155 серии взаимозаменяемы с более современными. Основные параметры: – напряжение питания +5 В (современные ТТЛ схемы – 2…3В); – уровень нуля в диапазоне от +0,05 до +0,4 В; – уровень единицы в диапазоне от +2,4 до +4,9 В; – помехоустойчивость средняя – это диапазон между нижним уровнем единицы и верхним уровнем нуля; – потребление среднее (1 – 10 мВт); – среднее время задержки 10 нс; – температурный диапазон –10 – +70 °C; Принципиальная схема одной из логических ТТЛ–схем ЛА-3 изображена на рисунке 2.4, а). В корпусе б) размещены четыре совершенно одинаковых схемы. На его поверхности, сверху или снизу располагается метка (точка или вмятина). Смотреть на микросхему (корпус) снизу, на электроды, считать от метки по часовой стрелке. Седьмой электрод предназначен для подключения минуса источника питания, четырнадцатый – для плюса. По такому же принципу производится отсчет электродов и в других, более сложных случаях.  Рисунок 2.4 – ТТЛ логическая схема ЛА-3, а); цоколевка, б) Диоды VD1 и VD2 имеют два назначения: 1 Противозвонное назначение. Смысл в том, что при переходе от нуля к единице или наоборот возникают колебательные процессы. И эти колебательные процессы затухают быстрее, если есть диоды VD1, VD2. 2 Входы ЛЭ не допускают даже кратковременную подачу отрицательных уровней, но иногда такое случается. Диоды их закорачивают, защищают входы. VT1 – многоэмиттерный транзистор. Каждый отдельный эмиттер – отдельный вход. Количество в среднем до десяти, т. е. эта схема содержит усилительные элементы в отличие от предыдущей, поэтому к выходу можно подключить до десяти точно таких же логических схем. Многоэмиттерный транзистор действует в двух режимах: 1 В прямом режиме, если на одном или на всех входах низкие уровни, образованные открытым транзистором VT5 предыдущей логической схемы. В этом случае входной электрод или оба одновременно действуют в эмиттерном режиме, коллекторный – в коллекторном режиме, базовый – в базовом. Токи протекают по следующим цепям:  предыдущей логической схемы…земля. предыдущей логической схемы…земля. 2 Если одновременно на все входы без исключения подается высокий уровень с выхода другой логической схемы, то VT1 действует в инверсном режиме, а именно: оба эмиттерных электрода действуют в коллекторном режиме, а коллекторный электрод VT1 в эмиттерном режиме. Токи:  , а часть тока протекает в цепь ГСТ, образованного R2, R3, VT3. Открывается VT2, начинает протекать ток по цепи: , а часть тока протекает в цепь ГСТ, образованного R2, R3, VT3. Открывается VT2, начинает протекать ток по цепи:  Эта цепь открывает VT5, следовательно, выход F через открытый VT5 соединяется с землей, выходное сопротивление F невелико, этим ускоряется разряд емкостей нагрузки, повышается быстродействие схемы. Т.к. выход F почти соединен с землей, на нем низкий уровень, называемый нулем. Резистор R1 устанавливает необходимую величину базового тока VT1 (≈4кОм). Транзистор VT2 предназначен для усиления по току, действует в основном в эмиттерном режиме, хотя есть и коллекторный резистор R4, с которого снимается ток в цепь базы VT4. R2, R3, VT3 – генератор стабильного тока (ГСТ). Физический смысл работы схемы заключается в следующем. В некоторых случаях, в книгах, изображают резистор вместо этой схемы, подразумевая эту схему. Для того, чтобы уменьшить потери на подложке, а также площадь на поверхности подложки, используют процессы, изображенные на рисунке 2.5.  Рисунок 2.5 – Процессы в схеме ГСТ По отношению к VT3, цепь VT2–R4 имеет небольшое сопротивление. Поэтому нагрузочная прямая изображается с малым наклоном влево из точки EI0. При повышении напряжения до ЕII0 происходит одновременное смещение нагрузочной прямой.  (высокое) (высокое)Таким образом, в случае нестабильности напряжения питания в диапазоне от E0’до E0’’ динамическое сопротивление высокое. С другой стороны, высокое сопротивление только в диапазоне ∆U, а статическое сопротивление постоянного тока примерно на порядок меньше. Следовательно, потери тоже небольшие. В сравнении с эквивалентным резистором, снижается нагрев подложки микросхемы. Транзистор VT5 совместно с VT4 образует инвертор, который в литературе называют мощным инвертором. Если на входы Х1 и Х2 одновременно подать высокие уровни, транзистор VT1 работает в инверсном режиме, через переходы Б –Э VT2, VT5 протекают токи, следовательно, VT2, VT5 открыты. С одной стороны выход F через открытый транзистор VT5 соединен с землей. На нем низкий уровень, “0”. Выходное сопротивление выхода F минимальное. С другой стороны, так как VT2 открыт, образуется цепь  – это основная токовая цепь, открывающая транзистор VT5. Т. е. ток резистора R4 не ответвляется в цепь базы VT4, а уходит в открытый VT2. На диоде VD3 выделяется падение напряжения в соответствии с рисунком 2.6 – это основная токовая цепь, открывающая транзистор VT5. Т. е. ток резистора R4 не ответвляется в цепь базы VT4, а уходит в открытый VT2. На диоде VD3 выделяется падение напряжения в соответствии с рисунком 2.6 Рисунок 2.6 – Типовая диодная характеристика Плюс падения напряжения на VD3 прикладывается к эмиттерному электроду транзистора VT4, а минус через  к базе VT4, удерживают VT4 закрытым. Следовательно, на выходе F будет наблюдаться низкий уровень при двух высоких на входах Х1, Х2. к базе VT4, удерживают VT4 закрытым. Следовательно, на выходе F будет наблюдаться низкий уровень при двух высоких на входах Х1, Х2. Так как в цепях Б – Э VT2, Б – Э VT5 протекают открывающие токи, то образуются диффузионные заряды в объемах баз. Условно считаем, что это эквивалентно подключению двух конденсаторов Сдифф.1 и Сдифф.2 (в действительности их нет). Напряжение каждого такого конденсатора равно падению напряжения на переходе Б – Э 0.6 ÷ 0.7 В (см. рисунок 2.6, как у диода). Теперь подадим на любой из входов (Х1, Х2 или на оба одновременно) низкий уровень. Транзистор VT1 переходит в нормальный для него режим. Эмиттерный электрод выполняет эмиттерную роль, коллекторный – коллекторную. Из базы транзистора VT2 вытекает ток, поэтому VT2 закрыт. Вместе с ним закрыт VT5, следовательно, ток резистора R4 не может протекать через закрытый VT2, направление ему в Б – Э VT4, VD3, выход F и нагрузку, не изображенную на схеме и т. д. Следовательно, VT4 открыт. Образуется цепь  . На выходе F выделяется высокий уровень, называемый единицей. Выходное сопротивление F невелико, т.к. VT4 открыт, а источник питания E0 по переменной составляющей считается связанным с землей. . На выходе F выделяется высокий уровень, называемый единицей. Выходное сопротивление F невелико, т.к. VT4 открыт, а источник питания E0 по переменной составляющей считается связанным с землей.Выводы: 1 Схема инвертирует входные логические сигналы. 2 Это схема безусловного подчинения нулю (низкому уровню) по одному или всем входам. Если на любой из входов подать нуль, на выходе принудительно выделится единица. Включение ускоряется потому, что в схеме три транзистора включены как один, а именно: если на все входы одновременно подать высокие уровни, то протекают токи, открывающие VT2, VT5 по цепи.  инверсный режим инверсный режим Форсирование закрывания объясняется тем, что условные конденсаторы Сдифф.1,2 были заряжены на интервале открытого состояния VT2, VT5, и после подачи низкого уровня на любой из входов образуется цепь  предыдущей логической схемы предыдущей логической схемы . .Собственно в этой цепи включены два источника с напряжением 0.6 ÷ 0.7 В (в сумме 1.2 ÷ 1.4 В), которые образуют этот разрядный ток для диффузионных емкостей, одновременно форсирующий закрывание VT2, VT5. При переключении транзисторов VT4, VT5, на интервале времени, равном десятым долям наносекунды, когда один транзистор из пары открылся, а второй еще не закрылся из–за наличия этапа рассасывания, протекает сквозной ток по цепи:   . Этот сквозной ток в среднем на порядок превышает ток нагрузки, образуя выброс. В соседних цепях печатной платы, в жгутах возникают наводки, которые могут привести в ложному срабатыванию соседних микросхем. Для предотвращения рекомендуется к электродам питания микросхем (например 7, 14) припаивать конденсаторы емкостью до 100 ПФ. В моменты переключений транзисторов выбросы сквозных токов потребляются из конденсаторов, тем более потому, что цепи питания имеют распределенные индуктивности, представляющие для быстро протекающих процессов повышенное сопротивление. Следовательно, уровень помех в цепях питания снижается. . Этот сквозной ток в среднем на порядок превышает ток нагрузки, образуя выброс. В соседних цепях печатной платы, в жгутах возникают наводки, которые могут привести в ложному срабатыванию соседних микросхем. Для предотвращения рекомендуется к электродам питания микросхем (например 7, 14) припаивать конденсаторы емкостью до 100 ПФ. В моменты переключений транзисторов выбросы сквозных токов потребляются из конденсаторов, тем более потому, что цепи питания имеют распределенные индуктивности, представляющие для быстро протекающих процессов повышенное сопротивление. Следовательно, уровень помех в цепях питания снижается. Сквозные токи – один из основных недостатков ТТЛ серии. На электрических принципиальных схемах часто изображают несколько конденсаторов, включенных параллельно. Объяснение здесь в том, что разные конденсаторы неодинаково фильтруют помехи. Например, электролитические конденсаторы с большой емкостью плохо фильтруют высокочастотные составляющие. Электролитическая лента внутри конденсатора свернута в трубку, представляющую собой индуктивность, препятствующую прохождению высокочастотных помех. Поэтому параллельно электролитическим включают керамические конденсаторы, емкость которых меньше, но они лучше фильтруют высокочастотный спектр. Некоторые особенности ТТЛ–серии: 1 Состояние типа “Z”. Выходы микросхемы, изображенной на рисунке 2.4, нельзя соединять напрямую с выходами такой же схемы, потому что, если транзистор VT5 одной из них открыт, а второй – закрыт, то произойдет короткое замыкание. В таком случае необходимы микросхемы, у которых не два состояния, а три (третье – типа “Z”, при котором VT4, VT5 одновременно закрыты). Программированием исключается состояние короткого замыкания. Выход F в этом случае имеет высокое выходное сопротивление, так как оба транзистора закрыты. Схема логического элемента с состоянием типа Z изображена на рисунке 2.7.  Рисунок 2.7 – Логический элемент с состоянием типа “Z”. Если на входе U0 инвертора “1”, то на выходе будет “0”, следовательно, образуется цепь, соединяющая VT2 с землей (коллекторный электрод). VT2 открыт, VT4, VT5 одновременно закрыты, так как ток транзистора VT1 уходит через Б–К VT2 на землю и ток R4 тоже уходит на землю. 2 Объединение выходов. Используется микросхема (см. рисунок 2.8) с открытым коллектором (бывает с открытым эмиттером).  Рисунок 2.8 – Микросхема с открытым коллектором Выходы этих микросхем можно соединить друг с другом, но величину тока необходимо рассчитывать по наихудшему случаю. Обычно последовательно с коллекторным электродом включают элементы индикации, светодиоды, обмотки реле, цепи других логических элементов. Если на входы подавать импульсы, то на выходе в этом виде импульсов не будет, так как нет напряжения. Чтобы наблюдать импульсы, необходимо дополнить схему резистором R. Тогда в цепи этого резистора и транзистора VT4 появится импульсный ток, а на экране осциллографа импульсы напряжения. Допустимые величины тока для ЛА7 – 15 мА, ЛА8 – 5 мА. Ромбик с подставкой означает открытый коллектор. |