Конспект лекций. Заочная форма 2021 г

Скачать 332.5 Kb. Скачать 332.5 Kb.

|

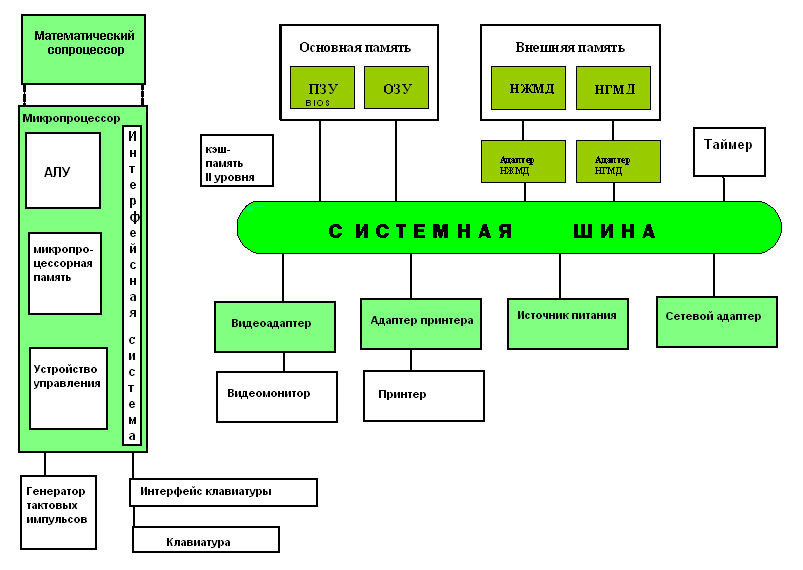

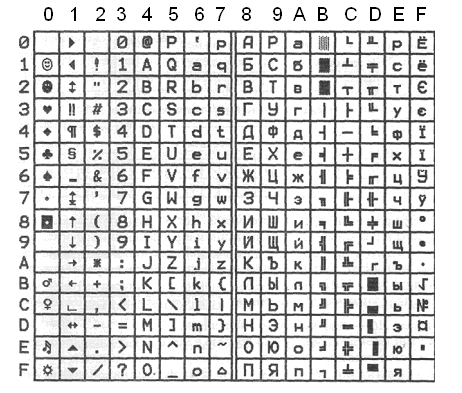

Вычислительные машины, системы и сети.(Краткий конспект лекций. Заочная форма 2021 г.) 1.Понятие архитектуры и структуры ЭВМ. Архитектура ЭВМ определяется совокупностью свойств, существенных для пользования. При этом основное внимание уделяется структуре компьютера и функциональным возможностям. Функциональные возможности делятся на основные и дополнительные: Основные: Обработка и хранение данных; Обмен данными с внешними объектами. Дополнительные предназначены для повышения эффективности выполнения основных функций. Структура – модель, устанавливающая состав, порядок и принципы взаимодействия входящих в неё компонентов. Разберём на примере ПК: ПК – переносная или настольная ЭВМ, удовлетворяющая принципам доступности и универсальности применений. Положительные моменты: - автономность эксплуатации без жестких требований к окружающей среде; - гибкость архитектуры, адаптивность к различным сферам деятельности; - высокая надежность работы и возможность замены компонентов; - сопоставимость операционных систем и прочего программного обеспечения, позволяющая использовать возможность работы с ПК без специальной подготовки; - небольшая стоимость по сравнению с серверными системами. 2.Структурная схема ЭВМ на примере ПК. Микропроцессор – центральный блок компьютера, предназначенный для управления всех устройств ЭВМ, выполнения арифметических и логических операций. АЛУ – арифметико-логическое устройство. Предназначено для выполнения арифметических-логических операций над числовой и символьной информацией. УУ – устройство управления. Формирует и подаёт в нужные моменты времени определённые управляющие импульсы (сигналы управления), которые обусловлены спецификой выполняемой операции и результатами выполненной операции (предыдущей). Устройство управления также формирует адреса ячеек памяти, которые используются выполняемой операцией и передаёт эти адреса в соответствующие блоки ЭВМ. Опорную последовательность импульсов устройство управления получает от генератора тактовых импульсов.  Микропроцессорная память (состоит из регистров) – предназначена для кратковременного хранения, записи и выдачи данных, которые непосредственно используются в вычислениях в ближайшие такты работы процессора в данные моменты времени. Регистры – быстродействующие ячейки памяти различной длины, обеспечивающие высокое быстродействие вычислительного процесса и процесса управления. Микропроцессорная память (состоит из регистров) – предназначена для кратковременного хранения, записи и выдачи данных, которые непосредственно используются в вычислениях в ближайшие такты работы процессора в данные моменты времени. Регистры – быстродействующие ячейки памяти различной длины, обеспечивающие высокое быстродействие вычислительного процесса и процесса управления.Интерфейсная система МП – предназначена для реализации сопряжения и связи процессора с другими блоками компьютера. Включает в себя внутренний интерфейс МП, буферные запоминающие регистры и схемы управления портами ввода-вывода и системной шиной. Порт – аппаратура сопряжения, позволяющая подключить к процессору другие устройства. Математический сопроцессор находится в микросхеме основного процессора и используется для выполнения операций над двоичными числами с плавающей запятой. И над двоично-десятичными кодированными числами. А также для вычисления некоторых математических функций. Математический сопроцессор имеет свою систему команд, работает параллельно с основными МП, но строго под его управлением. Кэш первого уровня (I) – предназначен для ускорения выполнения команд и передачи данных. Генератор тактовых импульсов – предназначен для выработки или генерации опорной последовательности электрических импульсов, которые подаются на устройство управления МП. Частота генерируемых импульсов определяет тактовую частоту процессора. Промежуток времени между соседними импульсами определяет время одного такта (такт работы компьютера). Частота генерируемых импульсов – одна из основных характеристик компьютера, которая определяет быстродействие. Кэш второго уровня (II и так далее) – предназначен для ускорения выполнения команд и передачи данных. Системная шина – основная интерфейсная система компьютера, предназначенная для обеспечения сопряжения и связи всех устройств ЭВМ между собой. Она включает в себя: Кодовую шину данных (физически – набор проводников и микросхем); Предназначается для параллельной передачи всех разрядов чисел кода операции. Размерность – до 64 бит. Кодовая шина адреса; Предназначена для параллельной передачи всех разрядов числового кода адреса ячейки основной памяти или адреса порта ввода-вывода внешнего устройства. Кодовая шина инструкций; Предназначена для параллельной передачи управляющих сигналов во все блоки компьютера. Шина питания; Предназначена для подключения всех составляющих ЭВМ к системе энергопитания. Системная шина обеспечивает три основных направления передачи информации и данных. - между процессором и основной памятью; - между процессором и портами ввода-вывода; - между основной памятью и портами ввода-вывода (режим прямого доступа к памяти). Управление шиной осуществляется процессором либо контроллером. Основная память предназначена для хранения и оперативного обмена данными между устройствами компьютера. Состоит из двух частей: ОЗУ и ПЗУ. ПЗУ предназначено для хранения неизменных данных (либо справочной информации, либо программ). Позволяет оперативно считывать хранящуюся в нём информацию. ОЗУ предназначено для оперативной записи, хранения и считывания программ и данных, непосредственно участвующих в информационно-вычислительном процессе, который выполняет компьютерная система в текущий момент времени. Главное достоинство – высокое быстродействие, возможность обращения к любой ячейке памяти отдельно. Это называется прямой адресный доступ к памяти. Внешняя память используется для долговременного хранения данных. Также возможны считывание и запись. Таймер – внутримашинные электронные часы, обеспечивающие автономный съём текущего момента времени. Питается от батарейки. Сетевой адаптер – относится к устройствам связи и телекоммуникаций, которые используются для связи с приборами и другими средствами автоматизации, различными согласовательными интерфейсами (ЦАП, АЦП) и для подключения компьютера к каналам связи с другими компьютерными системами и сетями. Сетевой адаптер – внешний интерфейс компьютера для подключения к каналам связи, для обмена информацией с другими устройствами. Функции сетевого адаптера выполняет модулятор-демодулятор. Обмен информацией осуществляется по определённым протоколам, в зависимости от того, с какими устройствами устанавливается связь. Монитор – устройство для отображения вводимой и выводимой информации. Принтер – устройство для вывода информации на бумажный носитель, фотобумагу, пластик и другие материалы. Клавиатура – устройство для ввода информации (символьной, числовой и управляющей). Мышь – устройство для ввода информации (управляющей). Остальные устройства: Сканер – устройство ввода графической информации. Планшет – устройство ввода графической и управляющей информации. Микрофон, динамики, веб-камера, проектор, интерактивная доска. Контроллеры – предназначены для осуществления интерфейса между устройствами и обмена по протоколу между устройством и системной шиной. Контроллер прямого доступа к памяти – предназначен для прямого управления накопителями на магнитных дисках, освобождая процессор от данных действий, чем увеличивает быстродействие. Контроллер прямого доступа к памяти осуществляет обмен данными между ОЗУ и внешними запоминающими устройствами без участия процессора. Контроллер прерываний Прерывание – временная остановка выполнения одной программы в целях оперативного выполнения другой, более важной в данный момент времени. Контроллер прерываний предназначен для обслуживания процедуры прерывания. Принимает запрос на прерывание от внешнего устройства, определяет уровень приоритета данного запроса и выдаёт сигнал прерывания в процессор. Процессор, получив сигнал прерывания от контроллера, приостанавливает выполнение текущей программы и переходит к выполнению программы обслуживания прерывания, которое запросило внешнее устройство. После завершения выполнения программы обслуживания прерываний процессор переходит к выполнению прерванной программы. Контроллер прерываний программируемый. 3. Представление информации в ЭВМ. В большинстве компьютеров используется двоичная система счисления. В ней наименьшая единица информации – 1 бит. Минимальное машинное слово – 2 байта. Полуслово – 1 байт. Расширенное слово – 8 байт. Система счисления. Способ наименования и изображения чисел с помощью символов, имеющих определённое количественное значение. Система счисления бывают позиционные и непозиционные. Непозиционная система – система, в которой цифры не меняют своё количественное значение при изменении их расположения в числе. Позиционная – система, в которой цифры меняют своё количественное значение при изменении их положения в числе. Название любой позиционной системы счисления определяется количеством различных цифр, с помощью которых можно записать число. Перевод из десятичной в любую другую. Десятичное число последовательно делится на основание системы счисления, в которую переводим до тех пор, пока последнее частное не станет меньше основания системы счисления. Перевод из любой системы в десятичную. Число записывается в позиционной записи и вычисления проводятся в десятичной системе счисления. Принцип эквивалентности. Включает в себя замену соответствующего количества цифр одной системы счисления на соответствующее количество цифр другой системы счисления. Для перевода шестандцатиричных чисел в двоичную систему, каждая шестнадцатеричная цифра числа заменяется тетрадой двоичных чисел. Тетрада – четыре последовательных цифры. Для перевода восьмеричных – триадой. Триада – три последовательных. Таблица эквивалентности… Перевод нецелых чисел из десятичной в двоичную. Дробное и целое части переводятся отдельно. Целая часть – по правилу последнего деления, а дробная – по правилу последнего умножения на основание системы счисления, в которую переводится. Арифметические действия над целыми двоичными числами. (Подробнее см. ФАЙЛ «Системы счисления Переводы.» Прямой, обратный и дополнительный коды. (выполнение арифметических действий с отрицательными числами в 1 байте). Числа в компьютерных системах вводятся в прямом коде. При выполнении операций сложения двоичных положительных и отрицательных двоичных чисел, отрицательные числа переводятся в дополнительный код. Дополнительный код положительного числа совпадает с прямым кодом. Дополнительный код отрицательного числа получается посредством перевода прямого кода в обратный, а обратного в дополнительный. Обратный перевод осуществляется также – сначала в обратный, потом в прямой. Обратный код отрицательного числа получается инверсией всех двоичных разрядов отрицательного числа, кроме знакового. Дополнительный код получается из обратного кода прибавлением к младшему разряду двоичного числа единицы. В переводе из прямого в обратный и дополнительный коды знаковый бит не участвует. В выполнении арифметических операций знаковый бит участвует. Представление буквенной, числовой и символьной информации. Существует международный стандарт. ASCII – американский международный код для обмена информацией. Он имеет основной стандарт и его расширения. Для кодирования используются шестнадцатеричные коды. Основной стандарт – от 00 до 7F. Дополнительный – от 80 до FF. Все коды основного и дополнительного стандарта записываются в одном байте. Основной стандарт – международный. Предназначен для кодирования десятичных цифр и всех букв латинского алфавита, а также ряда служебных символов. Расширенный стандарт – предназначен для кодирования букв национального алфавита и символов псевдографики. Таблица кодов АSCII  В вычислительных сетях используются другие стандарты обмена информацией. В этих стандартах каждый код занимает 2 байта. В стандарте присутствуют практически все символы алфавитов мира и цифры. Он включает 65 тысяч закодированных знаков. Представление чисел с фиксированной и плавающей точкой. В компьютере применяются две формы представления двоичных чисел – с фиксированной и с плавающей. Поле символа – последовательность нескольких бит или байт. Поля делятся на поля постоянной и переменной длины. Биты в поле нумеруются справа налево. Поле переменной длины может иметь от 0 до 256 байт, но должно равняться целому числу байт. Числа с фиксированной точкой записываются в виде последовательности двоичных цифр с постоянным расположением точки. Число с фиксированной точкой, занимающее одно машинное слово: Знак находится в 15-м бите, значащая часть – всё остальное. Числа с плавающей точкой представляются в виде двух групп чисел: мантиссы и порядка. Мантисса всегда меньше единицы. Порядок – целое число. N = ±MPR R – порядок, P – основание системы счисления, M – мантисса. Нормализованная форма числа с плавающей точкой. Форма представления числа с плавающей точкой называется нормализованной, если мантисса имеет ненулевой левый разряд. Форма представления числа с плавающей точкой. Минимальная конфигурация. Двойное слово.

(Подробнее см. ФАЙЛ «Варианты представления информации в ПК.» Сложение чисел с плавающей точкой. При сложении чисел с плавающей точкой с одинаковым порядком их мантиссы складываются, а результату присваивается порядок, общий для исходных чисел. При сложении чисел с плавающей точкой с различными порядками, сначала выравниваются порядки чисел (число с меньшим порядком приводится к числу с большим порядком). Если при выполнении операции сложения мантисс возникает переполнение, то сумма мантисс сдвигается вправо на один разряд, а порядок суммы увеличивается на единицу. 0,01101 * 23+ 0,1001 * 23= 0,11111 * 23 0,01101 * 22 = 0,001101 * 23 + 0,1001 * 23 0,110001 * 23

4.Цифровой логический уровень Логические основы построения ЭВМ. Для анализа и синтеза схем в компьютерных системах, а также при алгоритмизации и программировании для решения конкретных задачи широко используется математический аппарат алгебры логики. Логические высказывания. Высказывание – любое предложение, в отношении которого имеет смысл утверждать о его истинности или ложности. Считается, что высказывание удовлетворяет закону исключающего третьего: каждое высказывание либо истинно, либо ложно. Простейшие операции алгебры логики. Логическое сложение (дизъюнкция). Операция «или», «\/», «+». Логическое умножение (конъюнкция). Операция «и», «/\», «*». Логическое отрицание. Операция «НЕ». Основные законы алгебры логики. Сочетательный; Переместительный; Распределительный. Логический синтез вычислительных схем. Логические блоки по международным стандартам. (логические схемы) Таблица истинности основных логических элементов.

логическая схема сумматора сумматор предназначен для нахождения суммы двух двоичных чисел и является основным элементом арифметико-логического устройства процессора логическая схема полусумматора полусумматор реализует сложение двух одноразрядных двоичных чисел в результате получается двухразрядное двоичное число, младшей цифрой которого является сумма , а старшей-перенос( перенос в следующий разряд) схема одноразрядного полусумматора  Таблица истинности одноразрядного полусумматора.

полный одноразрядный сумматор У полного одноразрядного сумматора есть возможность при сложении двух двоичных чисел учитывать наличие единицы переноса из старшего разряда. При построении его схемы используются два полусумматора, первый из которых суммирует два двоичных числа, а второй к полученному результату прибавляет перенос из старшего разряда.  Таблица истинности полного одноразрядного сумматора.

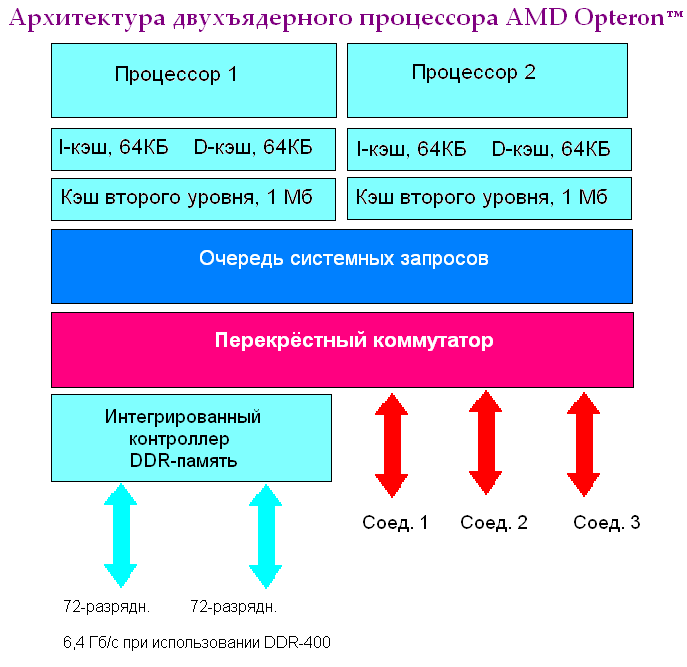

сложение трехразрядных двоичных чисел логическая схема суммирования в результате их сложения получается четырехразрядное двоичное число  Электронная реализация логического элемента рассмотрим электронную реализацию элемента *и не* построенного на двух NPN транзисторах кристаллы процессора состоят из транзисторов от их количества зависит производительность на транзисторах можно реализовать любую логическую схему работа транзистора  через транзистор от коллектора к эмиттеру может протекать ток при наличии положительного напряжения на базе, это состояние называется- транзистор открыт при отсутствии положительного напряжения на базе ток от коллектора к эмиттеру не протекает, такое состояние называется- транзистор закрыт (заперт) схема логического элемента * и-не*  питающее напряжение подается на левые входы резистор r создает падение напряжения x и y - входы через входы подается информация в виде электрического напряжения, т.е если есть напряжение соответствует логическому да или единице, если нет напряжения, то логическому нет либо 0 yy-выход наличие напряжения между выходом yy и z соответствует логическому да либо 1 отсутствие соответствует логическому нет если на входы x и y подается два 0 (напряжение отсутствует) то транзисторы закрыты, ток по цепи не протекает в связи с этим возникает разность потенциалов между yy и z и соответственно на выходе получаем 1 если на х подается напряжение что соответствует 1, а на у не подается напряжение, то есть 0, то первый транзистор открыт, а второй закрыт, в общем ток не протекает, соответственно возникает напряжение между уу и z и на выходе уу получается 1 на оба входа подается 1 тогда ток везде протекает ток и открыты все транзисторы разности потенциалов нет и на выходе 0 00-1 10-1 01-1 11-0 5. Классическая архитектура ЭВМ и принципы Джона фон Неймана. принцип двоичного кодирования( все системы работают в двоичной системе счисления) принцип программного управления(ЭВМ работает по программе которая состоит из набора команд, команды выполняются автоматически друг за другом в определенной последовательности) принцип адресности памяти( основная память состоит из пронумерованных ячеек, каждая из которых может быть доступна программе по двоичному адресу) принцип иерархической памяти( как минимум из двух уровней основной и внешней) принцип однотипности представления чисел и команд( программы как и данные записываются в двоичном коде) принцип хранимой программы( в процессе выполнения задачи ее программа должна размещаться в запоминающем устройстве, которое должно обладать высокой скоростью выборки и записи) В модели фон Неймана был один регистр. Память вмещала 4096 слов. Каждое слово состояло из 40 бит и могло содержать либо 2 команды (по 20 бит), либо целое число со знаком (40 бит). Для команды: в первых 8 битах размещался тип команды, в остальных 12 – адрес слова памяти в ОЗУ. Для числа: 1 бит знаковый, 39 бит – само число. Внутри АЛУ находился специальный регистр (аккумулятор) размерностью 40 бит. Машина фон Неймана работала только с целыми числами. 6. ПРОЦЕССОРЫ принцип построения элементарного процессора задача центрального процессора состоит в выполнении программ которые находятся в основной памяти процессор вызывает команды из памяти, определяет их тип затем выполняет одну за другой последовательность структурная схема элементарного процессора 1-Блок управления-отвечает за вызов команд из памяти и определения их типа 2-АЛУ-выполняет арифметико логические операции 3-регистры-память процессора предназначенная для хранения промежуточных данных результатов и некоторых команд управления размер регистра обычно одинаков регистр-самая быстродействующая память основной регистр - регистр указатель команд(счетчик команд) в нем находится информация о выполнении последующей команды другие регистры могут быть многофункциональные либо выполнять специальные действия Физическая структура микропроцессора ядро процессора исполняющий модуль арифметико логическое устройства для управления операциями с целыми числами регистры интерфейсные шины и выходы на системную шину кэш первого уровня, кэш данных и кэш адреса блок для работы с числами с плавающей точкой(математический сопроцессор) блок декодирования инструкций опережающего их исполнение и предсказание в ветвлении функциональная структура микропроцессора по функциональному назначению выделяют 2 части работающие параллельно: 1 часть - операционная(содержит УУ, АУ и микропроцессорную память(регистры)) 2 часть- интерфейсная содержит адресные регистры, блок регистров команд, и схемы управления шиной и портами интерфейсная часть работает с опережением Устройство управления формирует сигналы для следующих процедур: 1)выбор из регистра счетчика адреса команды и адреса ячейки основной памяти 2) выборки из ячейки основной памяти кода операции очередной команды и прием считываемой команды в регистр команд 3) расшифровка кода операции и признаков выбранной команды 4) выборка операндов и выполнение заданной операции для обработки этих операндов 5) запись результатов операции в память 6)считывание из регистров команд и микропроцессорной памяти отдельно составляющих которые должны участвовать в формировании полных адресов 7) формирование адреса следующей команды УУ предназначено для выработки управляющих сигналов, которые должны поступать ко всем устройствам компьютера по всем кодовым шинам и инструкциям. Схема функционирования УУ. Кодовые шины адреса данных и инструкций предназначены для передачи адреса данных и инструкций от УУ к остальным устройствам. Запоминающий регистр хранит код выполняемой операции и адреса операндов, участвующих в операции. Дешифратор операции. ПЗУ микропрограмм хранит в своих ячейках управляющие сигналы, необходимые для выполнения в блоках компьютера процедур обработки информации. Импульсы по выбранному дешифратору в соответствии с кодом операции выводу считывают из ПЗУ микропрограмм необходимую последовательность управляющих сигналов и передают их на шину инструкций. Узел формирования адреса. Устройства, вычисляющие полный адрес ячейки памяти по реквизитам, поступающим из регистров команд и регистров микропроцессорной памяти. Арифметико логическое устройство-вычислительная схема которая выполняет процедуру сложения поступающих на нее двоичных кодов сумматор и схемы управления Регистры центрального процессора-ячейки в центральном процессоре предназначенные для кратковременного хранения данных и доступные из машинных программ все регистры имеют определенный размер и за каждым регистром центрального процессора закреплено определенное имя по назначению и способу использования регистры делятся на группы( по назначению и способу) 1 группа регистры общего назначения 1) универсальные 2) регистры смещения 2 группа сегментные регистры 3 группа регистры указатели команд 4 группа регистр указатель Выполнение операции по тракту данных. В простейших процессорах тракт данных состоит из регистров, АЛУ и нескольких шин. Схема тракта данных: Два значения A и B, находящиеся в регистрах, поступают во входные регистры АЛУ, потом выполняется операция, затем результат заносится в один из регистров. Такая операция имеет тип «регистр-регистр». Этот процесс называется циклом тракта данных. Существует и другой тип операций: «регистр-память». Данные вызываются из оперативной памяти и помещают его во входные регистры АЛУ. Результат – либо в ОЗУ, либо в один из регистров. Выполнение команд центральным процессором (выборка, декодирование, исполнение). Центральный процессор выполняет каждую команду за несколько шагов. 1.ЦП вызывает команду из памяти и переносит её в регистр команд. 2.Изменяет положение регистра-указателя команд (счётчик команд). 3.Определяют тип вызванной команды. 4.Если команда использует слово из оперативной памяти, ЦП определяет, где находится это слово. 5.Переносит слово из памяти, если это необходимо, в регистры центрального процессора. 6.Выполняет команду. 7.Переходит к пункту 1 данного алгоритма для выполнения следующей команды. Микросхема ЦП. Каждая микросхема процессора содержит набор выводов, через которые происходит обмен данными с другими устройствами. Одни из выводов передают сигналы от центрального процессора к другим устройствам. По другим выводам принимаются сигналы от других устройств. По третьей группе выводов и принимаются, и передаются сигналы. Все выводы микросхемы ЦП можно подразделить на три основных типа: Адресные. Информационные. Управляющие. Все выводы ЦП связаны шинами с соответствующими выводами на микросхемах памяти и на микросхемах ввода-вывода. Пример: чтобы вызвать команду из памяти, центральный процессор сначала посылает в память адрес этой команды по адресным выводам. Затем он запускает одну или несколько линий управления (по управляющим выводам), чтобы сообщить памяти, что необходимо сделать. Память выдаёт ответ, помещая нужное слово данных на информационные выводы. А по управляющим выводам посылают сигнал, что это сделано. Когда ЦП получил по управляющим выводам соответствующий сигнал, он принимает слово по информационным выводам и выполняет команду. ЦП подаёт сигналы на выходы и принимает сигналы с входа. Цоколёвка центрального процессора. Основные выводы – адресные и информационные (выводы данных). Выводы данных Если микросхема содержит m адресных выводов, процессор может обращаться к 2m ячейкам ОЗУ. Выводы адреса Если микросхема содержит n выводов данных, процессор может считать (записать) n-битное слово за одну операцию. 8,16,32,64. Выводы адреса. Выводы управления. Предназначены для регулирования и синхронизации потоков данных от процессора и к процессору. Выводы управления подразделяются на основные группы: Управление шиной. Выводы прерывания. Выводы арбитраж-шины (разрешение конфликтов в шине). Выводы состояния. Прочие (различные для различных модификаций процессора). Выводы управления шиной. Обеспечивают передачу информации для процессора о том, что из шины поступают какие-либо данные, либо процессор хочет считать какую-либо информацию из памяти или записать в неё. Выводы прерывания. Входы из устройств ввода-вывода в микропроцессор. По ним посылаются сигналы прерывания от устройство ввода-вывода. Выводы арбитраж-шины. По данным выводам осуществляется разрешение конфликтов в шине, то есть регулирование потоков данных в шине. Чтобы два устройства одновременно не использовали шину. Процессор тоже является устройством. Выводы состояния. По ним выдаётся информация о состоянии процессора. Выводы для связи с сопроцессором. Предназначены для обеспечения обмена информацией и передачи сигнала между ЦП и сопроцессором. Выводы символа синхронизации сигнала. По ним передаётся синхроимпульс. Прочие специальные выводы: Вывод перезагрузки компьютера; выводы для обеспечения совместимости с устаревшими микросхемами устройств ввода-вывода и так далее. Вывод питания. По составу инструкций процессоры делятся на классификационные группы: Процессоры с полным набором системных команд (CISC-архитектура); Этот тип инструкций исполняется за 4 такта работы. Большинство процессоров имеют именно такой состав инструкций. Intel, AMD. Концепция данной архитектуры характеризуется следующими свойствами: Большое число различных по формату и длине команд. Введение большого числа различных режимов адресации. Достаточно сложная кодировка инструкций. Выполнение одиночной CISC-команды может происходить очень быстро, но параллельно обрабатывать данные команды достаточно сложно. Процессоры с усечённым набором системы команд (RISC-архитектура); Микропроцессоры этого типа содержат только наборы простых команд . При необходимости использовать более сложные команды, они собираются из простых (сборка производится автоматически). Все простые команды данного типа процессоров имеют один размер и выполняются за один такт работы. По составу инструкций данный тип характеризуется свойствами: Фиксированная длина машинных инструкций. Просто формат команды. Специализированные команды для операций с памятью (чтение-запись). Большое количество регистров общего назначения(32 и больше). Отсутствие микропрограмм внутри самого процессора. Используется данный набор команд. Alfa, Dec.7 Также существуют гибриды CISC и RISC. Процессоры со сверхбольшим командным словом (VLIW-архитектура). Характеризуются тем, что одна инструкция процессора содержит несколько операций, которые могут выполняться параллельно. Данный подход упрощает физическую архитектуру процессора, а распределение вычислительных устройств входит в задачу программного обеспечение. При написании программ для данного типа процессора программисты не имеют доступа к внутренним командам процессора. Все команды, включая операционные системы, работают поверх низкоуровневого программного обеспечения. Этот тип команд используется в суперскалярных компьютерах с параллельным выполнением команд. Процессоры с минимальным набором системы команд (MISC-архитектура). Обладают свойством минимального набора команд и достаточно высокого быстродействия. С увеличением разрядности процессора команды данного типа могут располагаться по нескольку команд в одном машинном слове. Это увеличивает производительность и обработку нескольких потоков данных. Порядок выполнения команд оптимален по критериям максимальной загрузки маршрутов потоков данных. Представление машинных команд. Машинные команды занимают 4-6 байт. Первые 1-2 байта занимает код операции. В одном байте можно представить 256 различных кодов. Если команда сложная, то в первом байте записывается код группы операций, во втором байте уточняется код операции. Указывается тип операции и способ операции. В остальных байтах располагаются операнды. Машинные команды имеют от 0 до 2х операндов. Размерность их может быть 1 байт или слово. Операнды также могут располагаться в самой команде либо в одном из регистров процессора. Если операнд находится в регистре процессора, то в команде указывается имя соответствующего регистра. Операнды также могут находиться в ячейке оперативной памяти. Тогда в команде указывается адрес ячейки. Если операнд должен находится в определённом фиксированном месте (зависит от типа команды), тогда в команде явно расположение команды не указывается. Результат выполнения команды может быть записан либо в регистр, либо в ячейку оперативной памяти. 7.Основная память. ОЗУ Память – часть компьютерной системы, где хранятся программы и данные. Все ячейки памяти содержат одинаковое число бит. Если ячейка содержит n бит, то она содержит 2^n комбинаций. Если адрес содержит m бит, то адресное пространство 2^m. Минимальная ячейка – 8 бит. Байты группируются в машинные слова. У INTEL – прямой порядок байт. У SPARC – обратный порядок байт. Оперативная память может состоять из двух типов микросхем: динамического и статического. DRAM – динамического. SRAM- статического. В динамической памяти ячейки построены на основе полупроводниковых областей с накоплением заряда. Они потребляют малое количество энергии. Эти области – конденсаторы, они расположены на пересечении вертикальных и горизонтальных шин матрицы памяти. Запись и считывание информации осуществляется подачей электрических импульсов по тем шинам матрицы, которые соединены с элементами, принадлежащими данной ячейке памяти. При обращении к микросхеме динамической памяти на её входы сначала подаётся адрес строки матрицы, затем адрес столбца. Ячейка динамической памяти по сравнению со статической имеет большее время срабатывания, но и большую удельную плотность хранения информации. Статическая память – ячейки построены на основе различных вариантов триггеров (схема с двумя устойчивыми состояниями). После записи в такую ячейку одного бита, она может в ней храниться сколь угодно долго при наличии питания. При обращении к микросхеме статической памяти на неё подаётся полный адрес , который при помощи дешифратора преобразуется в сигнал конкретно выбранной ячейки. Статическая память достаточно энергоёмкая. Структурная схема модуля основной памяти: 1 – регистр данных 2 – регистр адреса 3 – интерфейс инструкций 4 – регистр адреса по одной координате (х) 5 – регистр адреса по координате (y) 6 и 7 – дешифраторы адреса по координатам х и у соответственно. 8 – куб памяти. Постоянное запоминающее устройство. Предназначено для постоянного хранения неизменяемой информации или данных. Основное, что там хранится – BIOS. (Basic Input Output System). BIOS – интерфейс между аппаратной и программной частью компьютерной системы. Содержит драйверы основных компонент для начальной загрузки. Микросхемы ПЗУ присутствуют на материнской плате и адаптерах. Также в ПЗУ может заноситься статистическая служебная информация, которую заносит производитель компьютерной системы. Микросхема ПЗУ. Существуют 4 типа микросхем ПЗУ. ROM – прожигаемая при изготовлении. В нужных местах «прожигаются» программы в виде нулей и единиц. PROM – прожигаемая, программируемая после изготовления. 1 раз программируется, не больше. EPROM – стираемая, программируемая. Старая программа стирается с помощью ультрафиолета через прозрачное окно на микросхеме. EEROM – электронно-стираемая программируемая. Используется сейчас для хранение BIOS. 8.Шинная архитектура ЭВМ. Шина – группа проводников и микросхем, соединяющих устройства ЭВМ. Шины по отношению к процессору бывают внутренними и внешними. Внутренние шины выполняют функцию соединения внутренних составляющих процессора. Внешние шины соединяют процессор с памятью и устройствами ввода-вывода. В настоящий момент все компьютерные системы содержат одну специальную шину между процессором и оперативной памятью и одну или несколько шин между процессором и устройствами ввода-вывода. Схема компьютерной системы с несколькими шинами Обмен информацией между внешними устройствами и шинами осуществляется с использованием ASCII-кода. Шинный интерфейс ЭВМ – совокупность средств сопряжения и связи, обеспечивающая эффективное взаимодействие систем и частей компьютерной системы. Сопряжение обеспечивается на двух уровнях – механическом и логическом. В качестве основной системной шины могут использоваться: шины расширений, локальные шины. Одной из основных составляющих шинной архитектуры компьютерной системы являются наборы системных микросхем. Большинство подчинённых устройств связаны с шиной через приёмник шины. Задающее устройство связано с шиной через передатчик шины. Устройства приёмники-задатчики связаны с шиной через приёмо-передатчик. Шины могут состоять из одной или четырёх составляющих. 9.Мультипроцессоры. Мультипроцессоры с общей памятью и одной шиной. Это системы нескольких параллельных процессоров , которые используют общую память. Мультипроцессоры с общей и локальной памятью. Локальная память предназначена для хранения программных данных, которые не требуется разделять между процессами. При обращении к локальной памяти общая шина не используется. Мультикомпьютер – система, состоящая из большого числа ЭВМ, взаимосвязанных и взаимодействующих между собой. Каждый со своей памятью, общей памяти нет. Обмен данными между ЭВМ осуществляется через послание. Топология мультикомпьютера может быть древовидная, кольцевая и звезда. Мультипроцессоры легче программировать, мультикомпьютеры легче конструировать. 10.Архитектура двухъядерных процессоров на примере процессоров AMD. Интегрированные контроллеры памяти и быстрые двухточечные соединения. Интегрированные контроллеры памяти предназначены для контроля и обмена данными процессора с оперативной памятью. Также имеются коммутаторы для обработки запросов от других процессоров. Функциональная схема одноядерного процессора AMD:  Интегрированный контроллер памяти Поскольку интегрированный контроллер памяти работает на одной частоте с ядром процессора, в результате получается соединение с очень низкой латентностью, даже при обращении к памяти на удаленном процессоре. Работа на тактовой частоте процессора также означает, что по мере увеличения скорости процессора будет возрастать и быстродействие памяти. Кроме того, встроенный контроллер памяти устраняет необходимость в шине FSB для доступа к DIMM-модулям памяти. Наконец, благодаря интегрированному контроллеру при каждом добавлении процессора пользователи добавляют и контроллер памяти. Именно поэтому пропускная способность памяти возрастает линейно по мере увеличения числа процессоров. HyperTransport Процессоры АМD Орteron™ используют быстрые соединения HyperTransport для связи с другими процессорами или операций ввода-вывода внутри системы. По сравнению ссовместно используемой шиной такое соединение имеет преимущество, поскольку не создаются перегрузки из-за конфликтов шины и проще поддерживать целостность сигнала. Соединения HyperTransport в настоящее время работают с частотой 1 Гц и обеспечивают пропускную способность между процессорами до 8 Гб/с, что повышает производительность и масштабируемость решений.  Преимущества: Конструкция двухъядерного процессора АМD Орteron™ обеспечивает пользователей возможностью наращивать свои вычислительные мощности, не увеличивая энергопотребление, т.е. обеспечивая лучшее соотношение производительности и затраченной энергии. Приложения с интенсивными вычислениями могут использовать увеличенную пропускную способность памяти и дополнительные вычислительные мощности двухъядерной конструкции для обеспечения более высокой производительности и пропускной способности. При проектировании сверхплотных стоек и блейд-серверов часто приходится сталкиваться с необходимостью поиска компромисса между требованиями к производительности и соответствием нормам энергопотребления. Двухъядерные решения НР и АМD обеспечивают оптимальный баланс между производительностью и плотностью размещения.. |