Основные компоненты микропроцессоров. КР МПС. Контрольная работа по дисциплине Микропроцессорные системы Основные компоненты микропроцессоров Работу

Скачать 139.91 Kb. Скачать 139.91 Kb.

|

|

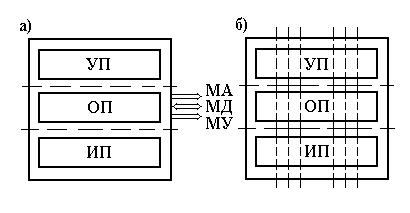

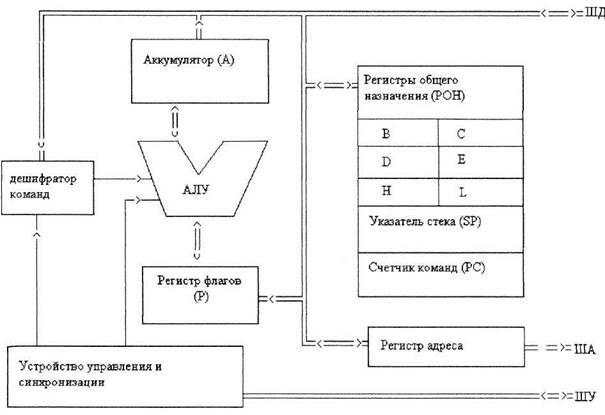

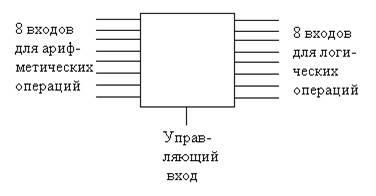

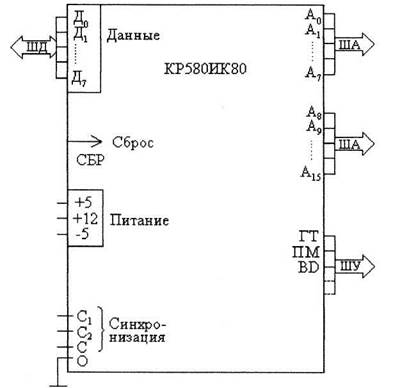

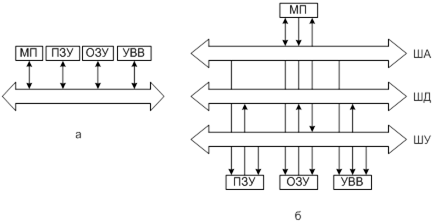

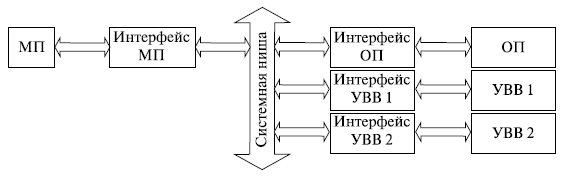

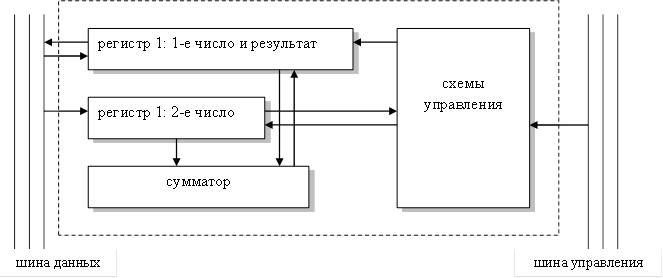

Министерство просвещения Российской Федерации ФГАОУ ВО «Российский государственный профессионально- педагогический университет» Институт инженерно-педагогического образования Кафедра информационных систем и технологий Контрольная работа по дисциплине «Микропроцессорные системы» Основные компоненты микропроцессоров Работу выполнил: ______ группа: ________ Номер зачетной книжки: ___ e-mail: _____ Работу проверил: _________ Екатеринбург РГППУ 2021 СодержаниеСодержание 2 Введение 3 Микропроцессоры: назначение и классификация 4 Характеристики микропроцессоров 8 Структура базового микропроцессора 9 Особенности реализации арифметико-логического устройства компьютера 15 Микропроцессорная память 17 Статусные флаги: 17 Управляющие флаги: 18 Заключение 19 Список использованных источников 20 ВведениеЭВМ начали свою широкую, начиная с 50-х годов. Если ранее это были громоздкие и сложные в обслуживании гиганты, используемые лишь в университетах, у военных или других гос. учреждениях и крупных фирмах. ЭВМ до неузнаваемости изменились с момента разработки устройств под названием микропроцессоры. Микропроцессоры: назначение и классификацияМикропроце́ссор — (устройство, отвечающее за выполнение арифметических, логических операций и операций управления, записанных в машинном коде), реализованный в виде одной микросхемы или комплекта из нескольких специализированных микросхем (в отличие от реализации процессора в виде электрической схемы на элементной базе общего назначения или в виде программной модели). Функции микропроцессора: вычисление адресов команд и операндов; выбор и дешифровка команд из основной памяти; выбор данных из основной памяти, регистров микропроцессорной памяти и регистров адаптеров внешних устройств; прием и обработка запросов и команд от адаптеров на обслуживание внешних устройств; обработка данных и их запись в основную память, регистры микропроцессорной памяти и регистры адаптеров внешних устройств; выработка управляющих сигналов для всех прочих узлов и блоков ПК; переход к следующей команде. По числу больших интегральных схем (БИС) различают микропроцессоры однокристальные, многокристальные и многокристальные-секционные. Процессоры даже самых простых ЭВМ имеют сложную функциональную структуру, содержат большое количество электронных элементов и множество разветвленных связей. Изменять структуру процессора необходимо так, чтобы полная принципиальная схема или ее части имели количество элементов и связей, совместимое с возможностями БИС. При этом микропроцессоры приобретают внутреннюю магистральную архитектуру, т. е. в них к единой внутренней информационной магистрали подключаются все основные функциональные блоки (арифметико-логический, рабочих регистров, стека, прерываний, интерфейса, управления и синхронизации и др.). Для обоснования классификации микропроцессоров по числу БИС надо распределить все аппаратные блоки процессора между основными тремя функциональными частями: операционной, управляющей и интерфейсной. Сложность операционной и управляющей частей процессора определяется их разрядностью, системой команд и требованиями к системе прерываний; сложность интерфейсной части разрядностью и возможностями подключения других устройств ЭВМ (памяти, внешних устройств, датчиков и исполнительных механизмов и др.). Интерфейс процессора содержит несколько десятков информационных шин данных (ШД), адресов (ША) и управления (ШУ). Однокристальные микропроцессоры получаются при реализации всех аппаратных средств процессора в виде одной БИС или СБИС (сверхбольшой интегральной схемы). По мере увеличения степени интеграции элементов в кристалле и числа выводов корпуса параметры однокристальных микропроцессоров улучшаются. Однако возможности однокристальных микропроцессоров ограничены аппаратными ресурсами кристалла и корпуса. Для получения многокристального микропроцессора необходимо провести разбиение его логической структуры на функционально законченные части и реализовать их в виде БИС (СБИС). Функциональная законченность БИС многокристального микропроцессора означает, что его части выполняют заранее определенные функции и могут работать автономно. На рисунке 1 показано функциональное разбиение структуры процессора при создании трехкристального микропроцессора (пунктирные линии), содержащего БИС операционного (ОП), БИС управляющего (УП) и БИС интерфейсного (ИП) процессоров.  Рисунок 1 Функциональная структура процессора (а) и ее разбиение для реализации процессора в виде комплекта секционных БИС Операционный процессор служит для обработки данных, управляющий процессор выполняет функции выборки, декодирования и вычисления адресов операндов и также генерирует последовательности микрокоманд. Автономность работы и большое быстродействие БИС УП позволяет выбирать команды из памяти с большей скоростью, чем скорость их исполнения БИС ОП. При этом в УП образуется очередь еще не исполненных команд, а также заранее подготавливаются те данные, которые потребуются ОП в следующих циклах работы. Такая опережающая выбор команд экономит время ОП на ожидание операндов, необходимых для выполнения команд программ. Интерфейсный процессор позволяет подключить память и периферийные средства к микропроцессору; он, по существу, является сложным контроллером для устройств ввода/вывода информации. БИС ИП выполняет также функции канала прямого доступа к памяти. Многокристальные секционные микропроцессоры получаются в том случае, когда в виде БИС реализуются части (секции) логической структуры процессора при функциональном разбиении ее вертикальными плоскостями Для построения многоразрядных микропроцессоров при параллельном включении секций БИС в них добавляются средства "стыковки". Для создания высокопроизводительных многоразрядных микропроцессоров требуется столь много аппаратных средств, не реализуемых в доступных БИС, что может возникнуть необходимость еще и в функциональном разбиении структуры микропроцессора горизонтальными плоскостями. В результате рассмотренного функционального разделения структуры микропроцессора на функционально и конструктивно законченные части создаются условия реализации каждой из них в виде БИС. Все они образуют комплект секционных БИС МП. По характеру временной организации работы микропроцессоры делят на синхронные и асинхронные. Синхронные микропроцессоры – микропроцессоры, в которых начало и конец выполнения операций задаются устройством управления (время выполнения операций в этом случае не зависит от вида выполняемых команд и величин операндов). Асинхронные микропроцессоры позволяют начало выполнения каждой следующей операции определить по сигналу фактического окончания выполнения предыдущей операции. Для более эффективного использования каждого устройства микропроцессорной системы в состав асинхронно работающих устройств вводят электронные цепи, обеспечивающие автономное функционирование устройств. Закончив работу над какой-либо операцией, устройство вырабатывает сигнал запроса, означающий его готовность к выполнению следующей операции. При этом роль естественного распределителя работ принимает на себя память, которая в соответствии с заранее установленным приоритетом выполняет запросы остальных устройств по обеспечению их командной информацией и данными. Характеристики микропроцессоровМикропроцессор характеризуется: 1) тактовой частотой: указывает, сколько элементарных операций (тактов) микропроцессор выполняет в 1 секунду. Тактовая частота измеряется в Мгц. Следует заметить, что разные модели МП выполняют одни и теже операции (например, сложение и умножение) за разное число тактов. Чем выше модель, тем, как правило, меньше тактов требуется для выполнения одних и тех же операций; 2) разрядностью, т.е. максимальным числом одновременно обрабатываемых двоичных разрядов. Разрядность МП обозначается m/n/k/ и включает: m – разрядность внутренних регистров, определяет принадлежность к тому или иному классу процессоров; n – разрядность шины данных, определяет скорость передачи информации; k – разрядность шины адреса, определяет размер адресного пространства. 3) объемом кэш-памяти, которая имеет три уровня: 4) архитектурой. Понятие архитектуры микропроцессора включает в себя систему команд и способы адресации, возможность совмещения выполнения команд во времени, наличие дополнительных устройств в составе микропроцессора, принципы и режимы его работы. Выделяют понятия микроархитектуры и макроархитектуры. Микроархитектура микропроцессора – это аппаратная организация и логическая структура микропроцессора, регистры, управляющие схемы, АЛУ, запоминающие устройства и связывающие их информационные магистрали. Макроархитектура – это система команд, типы обрабатываемых данных, режимы адресации и принципы работы микропроцессора. Структура базового микропроцессораУстройство и и принцип работы процессора разглядим на случае процессора на подобии КР580ИК80. Это однокристальный восьмиразряд-ный процессор. Он дает собой аналог процессора 8080 компании Intel, до сих властвующей на рынке процессоров. Исполнен на n-МОП структуре. Зодчество сего процессора дает собой зодчество на подобии Нейма-на, которая до сих времен применяется для управляющих процессоров, которые нас более всего заинтересовывают. Почти все функции сего про-цессора сохранены в иных, больше передовых управляющих процессорах. В то же время он несложен, по сопоставлению с передовыми информаци-онно-вычислительными процессорами, и благоприятен для исследования качеств процессора (кстати, на его базе разработаны процессоры передо-вых микропроцессорных контроллеров для управления технологическими процессами, в что количестве на термических электрических станциях и атомных электростанциях Упрощенная структура микропроцессора типа К580ИК80 имеет сле-дующий вид представленный на рисунке 2  Рисунок 2 – структура микропроцессора Важным узлом микропроцессора считается АЛУ – арифметико-логическое прибор. В нем выполняется математическая обработка данных, в него поступающих, которые вслед за тем передаются в иные узлы процессора. Это арифметические и закономерные операции. АЛУ изготавливает арифметические или же закономерные операции над восьмизначными количествами в зависимости от количества (,,1”, ,,0”) поступающего на его управляющий вход пример указан на рисунке 3  Рисунок 3 - поступление управляющих сигналов Арифметические операции (сложение, вычитание, умножение и деле-ние) в АЛУ (арифметико – закономерным устройством –важнейшей частью микропроцессора) выполняется с поддержкой сумматора (см) и регистра сдвига (последовательного регистра-см). Закономерные операции производятся с внедрением закономерных составляющих Итоги арифметических и закономерных операций, производимых в АЛУ, записываются в накопитель (А), производимый на регистрах (см) – ячейках памяти. По итогам выполнения операций АЛУ вводит коды, при-меняемые для контроля хода выполнения текущей программки, в регистр флагов (F). Блок регистров процессора имеет 6 универсальных 8-битных реги-стров, обозначаемых знаками B, C, D, E, H, L. В зависимости от произво-димых команд они имеют все шансы применяться или как отдельные 8-битные регистры, или как 16-битные регистры, состоящие из 8-битных пар (BC, DE, HL). Блок регистров имеет 2 16-битных регистра: указатель стека (SP) и счетчик команд (счетчик программ) (PC). «Стек» (от англ. – трость) работает для сбережения адресов ячеек в ОЗУ, специализированных для воплощения вступления нормальной про-граммки (режим прерывания ведущей программы). Счетчик команд имеет адресок производимой команды, его оглавле-ние механически меняется по окончании отработки текущей команды. В регистре адреса складывается код адреса ячейки памяти, выводя-щийся на шину адреса (ША). Прибор управления и синхронизации работает для управления хо-дом выполнения программы; сигналы от него выводятся на шину управ-ления (ШУ).Электрические выводы микропроцессора КР580ИК80 рисунок 4  Рисунок 4 - выводы микропроцессора КР580ИК80 К микросхеме микропроцессора подключаются следующие шины. · Восьмибитная шина данных, по которой информация (данные) по-ступает в процессор и от него в облике 8-битного двоичного кода, реали-зованного в облике импульсов наибольшего ( ,,1”) или же наименьшего (,,0”) данных значений, надлежащих с высочайшей частотой.· Шестираз-рядная шина адреса, по которой из процессора передаются восьмиразряд-ные коды адресов ячеек памяти и их черта в двоичном коде.· Шина управ-ления; по линиям этой шины идут коды: 1)От «ГТ» на «выбор кристаллов», т.е. на «оживление» с помощью элементов с тремя состояниями тех или иных компонентов микропроцес-сорной системы; 2)От «МП»- управление интерфейсами. 3)От «ВD» - управление УВВ, ОЗУ: принимать информацию (write – писать), передавать информацию (read – читать). 4)От других выводов, обеспечивающих работу МП на прерывание, «захват шин» при работе на внешние устройства и пр. Имеются выводы С1, С2, С, обеспечивающие синхронизацию работы микропроцессорной системы. Электропитание микропроцессора подключено к клеммам +5В, -5В, +12В относительно клеммы «земля», как, впрочем, и остальные выводы. По назначению микроЭВМ разделяются на универсальные и специа-лизированные (проблемно-ориентированные). По организации структуры различают одно- и многомагистральные микроЭВМ пример указан на рисунке 5.  Рисунок 5 - общая структура ЭВМ: а – одномагистральная; б – мно-гомагистральная В однолинейных микрокомпьютерах все прибора имеют один и тот же интерфейс и подключены к единственной информационной трассе, по которой передаются данные, адреса и управляющие сигналы. В многоли-нейных микрокомпьютерах прибора массовым образом включаются к собственной информационной трассе, собственно что разрешает воплотить в жизнь одновременную передачу по нескольким (или всем) трассам и что наиболее увеличивает производительность системы. Главным методикой организации МПС считается магистрально-модульный (рис. 1.3): все прибора, охватывая процессор, представлены в облике модулей, объединенных меж собой совместной трассой. Замен ин-формацией по трассе удовлетворяет притязаниям кое-какого совместного интерфейса, установленного для трассе сего на подобии. Любой модуль объединен с трассой сквозь особые интерфейсные схемы пример указан на рисунке 6.  Рисунок 6 магистрально-модульный принцип построения микропро-цессорной системы Общие сведения о микропроцессорных системах В связи с множеством областей применения МП и микроЭВМ можно классифицировать МПС на системном уровне. Они могут быть представлены: • Встроенными системами контроля и управления; • Локальными системами накопления и обработки информации; • Распределенными системами управления сложными объектами; • Распределенными высокопроизводительными системами па-раллельных вычислений. Исходя из вышесказанного, в наше время определились следующие приоритетные области, в которых применяются МПС: • Техника связи; • Системы управления; • Бытовая и торговая аппаратура; • Контрольно-измерительная аппаратура; • Военная техника; • Вычислительные машины, системы, комплексы и сети; • Транспорт. Процесс внедрения ПДК в области контрольно-измерительной тех-ники дозволил важно увеличить точность и надежность измерений, а еще расширить активные способности устройств и гарантировать выполнение надлежащих функций: калибровка, корректировка и температурная ком-пенсация, контроль и управление измерительным ансамблем, принятие за-ключений и обработка данных, диагностика поломок, индикация, провер-ки и поверка устройств. Внедрение ИПМ в системы связи привело к все наибольшему вытес-нению цифровых способов аналоговыми, собственно что привело к их ши-рокому использованию в преобразователях кодов, мультиплексорах, устройствах контроля промахов, блоках управления приемно-передающей аппаратурой Особенности реализации арифметико-логического устройства компьютераАрифметико-логическое устройство предназначено для выполнения арифметических и логических операций преобразования информации. Функционально АЛУ (Рисунок 7) обычно состоит из двух регистров, сумматора и схем управления (местного устройства управления).  Рисунок 7 Функциональная схема АЛУ Сумматор – вычислительная схема, выполняющая процедуру сложения поступающих на ее вход двоичных кодов; имеет разрядность двойного машинного слова. Регистры – быстродействующие ячейки памяти различной длины: регистр 1 имеет разрядность двойного слова, а регистр 2 – разрядность одного слова; при выполнении операций в регистр 1 помещается первое число, участвующее в операции, а по завершении операции – результат; в регистр 2 – второе число, участвующее в операции (по завершении операции информация в нем не изменяется); регистр 1 может и принимать информацию с кодовых шин данных, и выдавать информацию на них; регистр 2 только получает информацию с этих шин. Схемы управления принимают по кодовым шинам управления управляющие сигналы от устройства управления и преобразуют их в сигналы для управления работой регистров и сумматора АЛУ. Арифметико-логическое устройство выполняет арифметические операции только над двоичной информацией с точкой, фиксированной после последнего разряда, т.е. только над целыми двоичными числами. Выполнение операций над двоичными числами с плавающей точкой и над двоично-десятичными числами осуществляется с привлечением математического сопроцессора или по специально составленным программам. Рассмотрим в качестве примера выполнение команды умножения. Пусть перемножаются числа 1101 и 1011. Множимое находится в регистре 1, имеющем удвоенную по отношению к регистру 2 разрядность; множитель находится в регистре 2. операция умножения требует для своего выполнения нескольких тактов. В каждом такте число из регистра 1 проходит в сумматор (имеющий также удвоенную разрядность) только в том случае, если в младшем разряде регистра 2 находится 1. В данном примере в первом такте число 1101 пройдет в сумматор, и в этом же первом такте число в регистре 1 сдвигается на один разряд влево, а число в регистре 2 на один разряд вправо. В конце татка после сдвигов в регистре 1 будет находиться число 11010, а в регистре 2 – число 101. Во втором такте число из регистра 1 пройдет в сумматор, так как младший разряд в регистре 2 равен 1; в конце такта числа в регистрах опять будут сдвинуты влево и вправо, так что в регистре 1 окажется число 110100, а в регистре 2 – число 10. В третьем такте число из регистра 1 не пройдет в сумматор, так как младший разряд в регистре 2 равен 0; в конце такта числа в регистрах будут сдвинуты влево и вправо, так что в регистре 1 окажется число 1101000, а в регистре 2 – число 1. В четвертом такте число из регистра 1 пройдет в сумматор, так как младший разряд в регистре 2 равен 1; в конце такта числа в регистрах будут сдвинуты влево и вправо, так что в регистре 1 окажется число 11010000, а в регистре 2 – число 0. Так как множитель в регистре 2 стал равным нулю, операция умножения заканчивается. В результате в сумматор последовательно поступят и будут сложены числа: 1101, 11010, 1101000; их сумма 10001111 и будет равна произведению чисел 1101´1011. Микропроцессорная памятьМикропроцессорная память базового микропроцессора включает четырнадцать 2-байтовых запоминающих регистров. Все регистры можно разделить на четыре группы: универсальные регистры: AX, BX, CX, DX; сегментные регистры: CS, DS, SS, ES; регистры смещения: IP, SP, BP, SI, DI; регистр флагов FL. Каждый из универсальных регистров (или регистров общего назначения) может использоваться для временного хранения любых данных, при этом можно работать с каждым регистром целиком, а можно отдельно с каждой его половиной (регистры AH, BH, CH, DH – старшие байты, а регистры AL, BL, CL, DL – младшие байты соответствующих 2-байтовых регистров). Но каждый из универсальных регистров может использоваться и как специальный при выполнении некоторых конкретных команд программы. В частности: Статусные флаги:CF (Carry Flag) – флаг переноса; содержит значение «переносов» (0 или 1) из старшего разряда при арифметических операциях и некоторых операциях сдвига и циклического сдвига; PF (Parity Flag) – флаг четности; проверяет младшие 8 битов результатов операций над данными; нечетное число единичных битов приводит к установке этого флага в 0, а четное – в 1; AF (Auxiliary Carry Flag) – флаг логического переноса при двоично-десятичной арифметике; вспомогательный флаг переноса устанавливается в 1, если арифметическая операция приводит к переносу или заему четвертого справа бита однобайтового операнда; этот флаг используется при арифметических операциях над двоично-десятичными кодами и кодами ASCII; ZF (Zero Flag) – флаг нуля; устанавливается в 1, если результат операции равен нулю; если результат не равен нулю, то флаг обнуляется; SF (Sign Flag) – флаг знака; устанавливается в соответствии со знаком результата после арифметических операций: положительный результат устанавливает флаг в 0, отрицательный – в 1; OF (Overflow Flag) – флаг переполнения; устанавливается в 1 при арифметическом переполнении: если возник перенос в знаковый разряд при выполнении знаковых арифметических операций, если частное от деления слишком велико и переполняет регистр результата и т.д. Управляющие флаги:TF (Trap Flag) – флаг системного прерывания (трассировки); Когда флаг установлен в значение единица, процессор переводиться в режим выполнения программ пошагово. IF (Interrupt Flag) – Когда флаг установлен в значение единица разрешаются прерывания, при обратном случае – запрещаются.; DF (Direction Flag) – флаг направления; его применение состоит в данных состоящих из строк и он задает направление работы с данными; когда флаг установлен в “ноль” команда увеличивает содержимое регистров SI и DI на 1, Что инициализирует работу со строкой «слева направо», при установке в значение “один” – «справа налево». ЗаключениеВ данной работе были изучены устройство микропроцессоров МПС сферы применения данных устройств, описание основных компонентов. Сейчас сложно представить себе современный мир без микропроцессоров. Без данной технологии не было бы много очень привычным нам вещей: смартфонов, ноутбуков, умных часов и т.д. Список использованных источниковОсновы промышленной электроники /Под ред. В.Г. Герасимова.- М.: Высшая школа. Основы теории цепей; Учебник для ВУЗов. /В.П.Бакалов и др. 2-ое изд. перераб. и доп. – М. Прянишников В.А. Электроника. - СПб; Корона принт, 2002. Сборник задач по электротехнике и основам электроники / Под ред. В.Г. Герасимова.- М.: Высшая школа. Хоровиц П., Хилл У.. Искусство схемотехники.- М.:Мир. |