ВЫБОР СХЕМО-ТЕХНОЛОГИИ ПРОЕКТИРУЕМОЙ БИС. Краткий обзор существующих схемотехнологий применяемых в интегральных схемах

Скачать 1.8 Mb. Скачать 1.8 Mb.

|

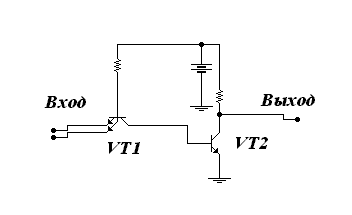

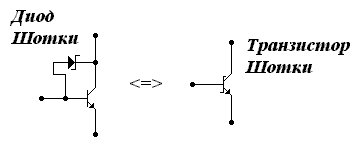

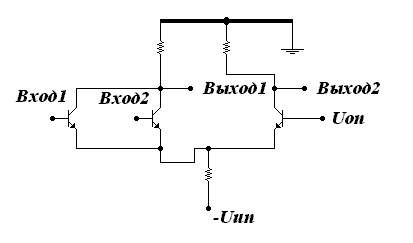

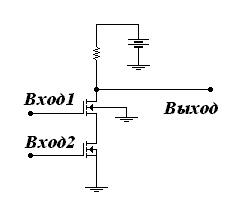

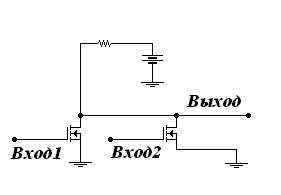

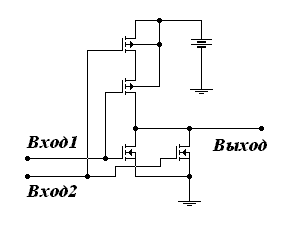

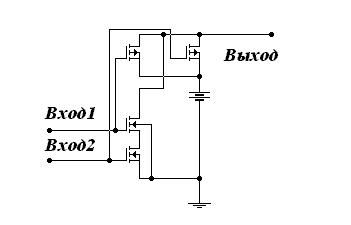

ВЫБОР СХЕМО-ТЕХНОЛОГИИПРОЕКТИРУЕМОЙ БИСКРАТКИЙ ОБЗОР СУЩЕСТВУЮЩИХ СХЕМО-ТЕХНОЛОГИЙ ПРИМЕНЯЕМЫХ В ИНТЕГРАЛЬНЫХ СХЕМАХ Рассмотрим наиболее распространенные схемотехнологии применяемые в интегральных схемах:Транзисторно-транзисторная логика (ТТЛ). Эмиттерно-связанная логика (ЭСЛ). Логика, построенная на основе структуры метал-диэлетрик-полупроводник с п-каналом (пМДП). Логика, построенная на основе структуры метал-диэлетрик-полупроводник с транзисторами разной проводимости (КМДП). ТЕХНОЛОГИЯ ТТЛ. Технология ТТЛ основана на биполярных структурах. Базовый элемент ТТЛ представляет собой схему, содержащую один многоэмиттерный транзистор и один обычный (см. рис. 4.1), это логическая схема И-НЕ (функцию И выполняет транзистор VT1, а функцию инверсии выполняет транзистор VT2).  Рис. 4.1. Базовый элемент ТТЛ. Подобная схема обладает низкой помехоустойчивостью и низким быстродействием, быстродействие можно увеличить, используя сложный инвертор, который позволяет сократить время включения (переход из логического «0» в логическую «1»); но время выключения (переход из логической «1» в логический «0») сократить, не удается. Более высокое быстродействие позволяют получить схемы субсемейства ТТЛШ (транзисторно-транзисторная логика с использованием транзисторов с барьером Шотки; см. рисунок 4.2). В таких схемах барьер Шотки создает нелинейную обратную связь в транзисторе, в результате транзисторы не входят в режим насыщения, хотя и близки к этому режиму. Следовательно, практически исключается время рассасывания, что позволяет существенно увеличить быстродействие. Р  ис. 4.2. Транзистор Шотки. ТЕХНОЛОГИЯ ЭСЛ. Т  ехнология ЭСЛ является так же, как и технология ТТЛ, биполярной, т.е. элементы строятся с использованием биполярных структур. Основой элементов ЭСЛ является так называемый «переключатель тока», на основе которого строится базовый элемент этой технологии - ИЛИ- -НЕ (см. рис. 4.3); по выходу1 данной схемы реализуется логическая функция ИЛИ-НЕ, а по выходу2 - ИЛИ. Рис. 4.3. Базовый элемент ЭСЛ. Из-за низкого входного сопротивления схемы ЭСЛ обладают высоким быстродействием и работают преимущественно в активном режиме, следовательно, помеха попавшая на вход усиливается. Для повышения помехоустойчивости шину коллекторного питания делают очень толстой и соединяют с общей шиной. По сравнению со схемами ТТЛ схемы ЭСЛ обладают более высоким быстродействием, но помехоустойчивость у них гораздо ниже. Схемы ЭСЛ занимают большую площадь на кристалле, потребляют большую мощность в статическом состоянии, так как выходные транзисторы открыты и через них протекает большой ток. Схемы, построенные по данной технологии не совместимы со схемами, построенными по другим технологиям, использующим источники положительного напряжения. ТЕХНОЛОГИЯ пМДП. В отличие от технологий, рассмотренных выше, технология пМДП основана на МДП - структурах, которые обеспечивают следующие преимущества по сравнению с биполярными: Входная цепь (цепь затвора) в статическом режиме практически не потребляет тока (высокое входное сопротивление); Простая технология производства и меньшая занимаемая площадь на кристалле. Основными логическими схемами изготовлеваемыми на основе пМДП являются схема ИЛИ-НЕ и И-НЕ (см. рис. 4.4 и рис. 4.5). Р  ис. 4.4. Схема ИЛИ-НЕ.  Рис. 4.5. Схема И-НЕ. К недостаткам этих схем можно отнести невысокое быстродействие, по сравнению со схемами ТТЛШ и ЭСЛ. Но в настоящее время благодаря применению новых технологий (окисная изоляция, использование поликремневых затворов, технология «кремний на сапфире») создаются быстродействующие МДП структуры. 4.1.4. ТЕХНОЛОГИЯ КМДП. Следующим шагом развития МДП технологии стало использование комплиментарных МДП транзисторов, т.е. транзисторов с разным типом проводимости, причем основными являются транзисторы п-типа; а транзисторы р-типа используются в качестве динамической нагрузки. Использование КМДП-схем по сравнению со схемами пМДП позволяет снизить потребляемую мощность, повысить быстродействие и помехоустойчивость, однако это достигается за счет увеличения площади занимаемой на кристалле и усложнения технологии производства. Б  азовыми элементами КМДП-схем являются, как и для пМДП, логические элементы ИЛИ-НЕ и И-НЕ (см рис. 4.6 и 4.7). Рис. 4.6. Схема ИЛИ-НЕ. |

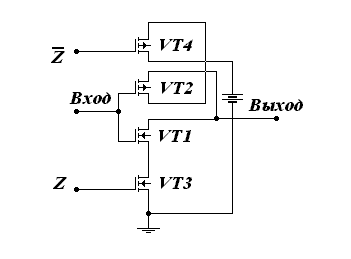

Вход | Z | Z | Выход |

| 0 1 0 1 | 0 0 1 1 | 1 1 0 0 | Отключен Отключен 1 0 |

Таблица 5.1.

ассмотрим принцип работы данной схемы. Управление ей осуществляется двумя входами

ассмотрим принцип работы данной схемы. Управление ей осуществляется двумя входами