Лекции по электронике1. Курс лекций угату 2008 удк ббк ш21 Шаньгин Е. С

Скачать 6.22 Mb. Скачать 6.22 Mb.

|

Рис. 15.8. Логические элементыЛогический элемент может быть реализован в виде отдельной интегральной схемы. Часто интегральная схема содержит несколько логических элементов. Логические элементы используются в устройствах цифровой электроники (логических устройствах) для выполнения простого преобразования логических сигналов. Классификация логических элементов. Выделяются следующие классы логических элементов (так называемые логики):

В настоящее время наиболее широко используются следующие логики: ТТЛ, ТТЛШ, КМОП, ЭСЛ. Логические элементы и другие цифровые электронные устройства выпускаются в составе серий микросхем: ТТЛ – К155, КМ155, К133, КМ133; ТТЛШ – 530, КР531, КМ531, КР1531, 533, К555, Км555, 1533, КР1533; ЭСЛ – 100, К500, К1500; КМОП – 564, К561, 1564, КР1554; GaAs – К6500. Наиболее важные параметры логических элементов:

Используются и другие параметры. Особенности логических элементов различных логик. Для конкретной серии микросхем характерно использование типового электронного узла – базового логического элемента. Этот элемент является основой построения самых разнообразных цифровых электронных устройств.

Рис. 15.9. Базовый элемент ТТЛ Если на один или оба входа одновременно подан низкий уровень напряжения, то многоэмитттерный транзистор находится в состоянии насыщения и транзистор Т2 закрыт, а следовательно, закрыт и транзистор Т4, т. е. на выходе будет высокий уровень напряжения. Если на обоих входах одновременно действует высокий уровень напряжения, то транзистор Т2 открывается и входит в режим насыщения, что приводит к открытию и насыщению транзистора Т4 и запиранию транзистора Т3, т.е. реализуется функция И-НЕ. Для увеличения быстродействия элементов ТТЛ используются транзисторы с диодами или транзисторами Шоттки.

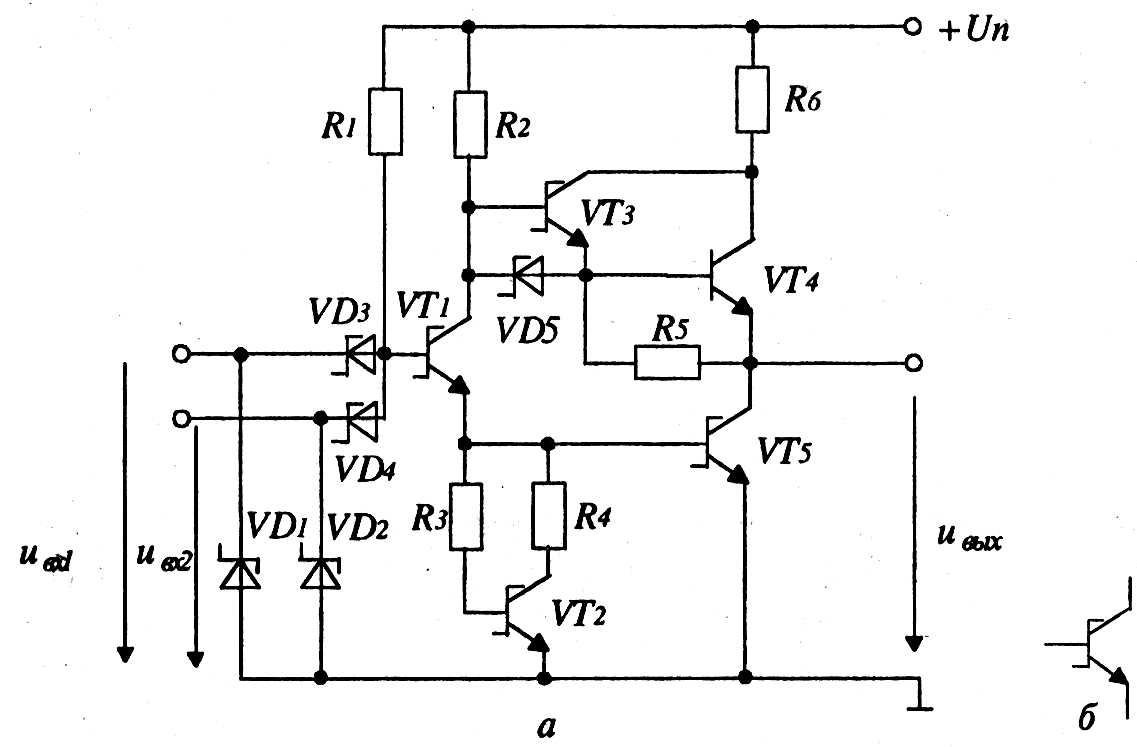

И-НЕ (рис. 15.10,а), а на рис. 15.10,б показано графическое изображение транзистора Шоттки.  Рис. 15.10. Логический элемент ТТЛШ Транзистор VT4 – обычный биполярный транзистор. Если оба входных напряжения uвх1 и uвх2имеют высокий уровень, то диоды VD3 и VD4 закрыты, транзисторы VT1, VT5 открыты и на выходе имеет место напряжение низкого уровня. Если хотя бы на одном входе имеется напряжение низкого уровня, то транзисторы VT1 и VT5 закрыты, а транзисторы VT3 и VT4 открыты, и на входе имеет место напряжение низкого уровня. Микросхемы ТТЛШ серии К555 характеризуются следующими параметрами:

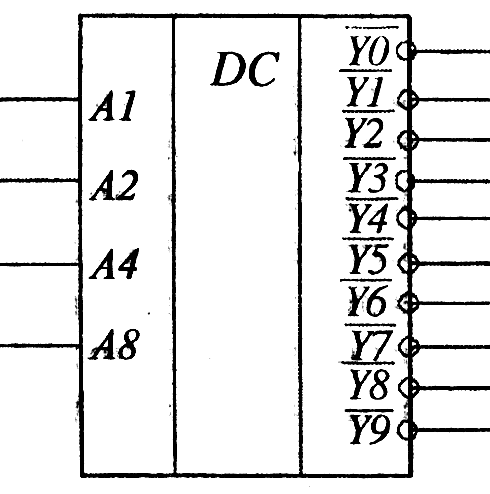

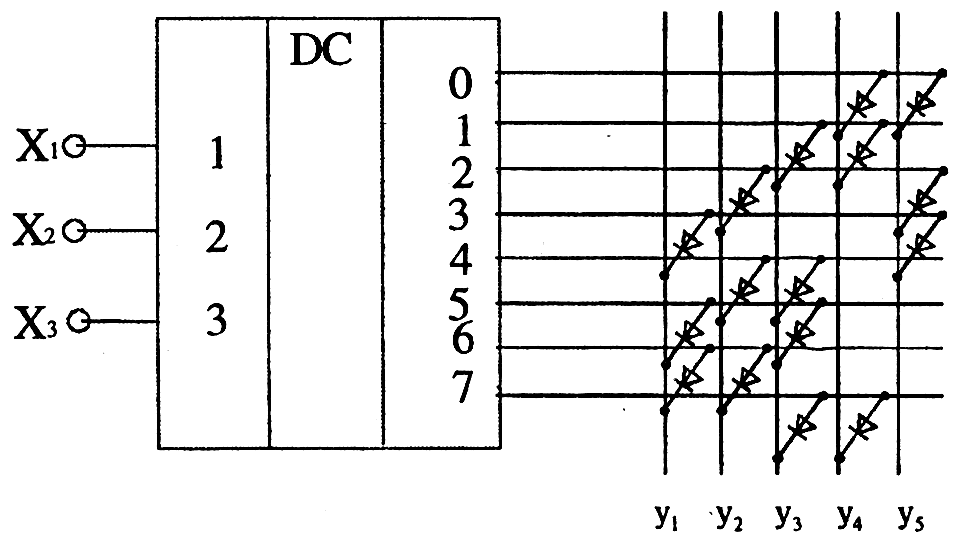

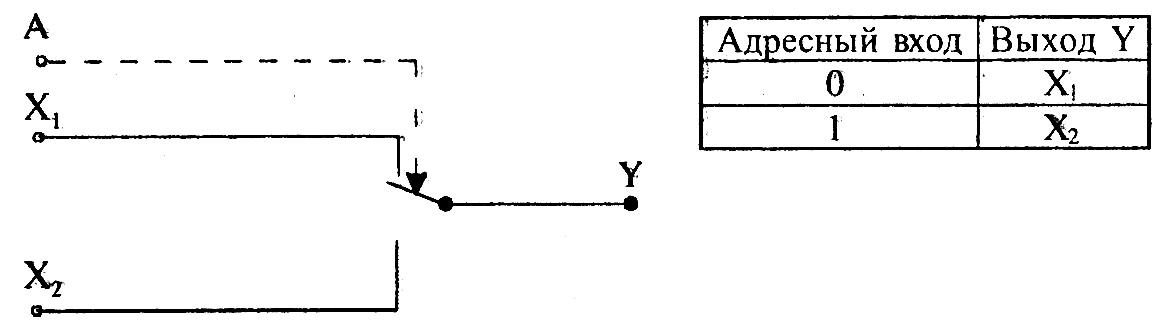

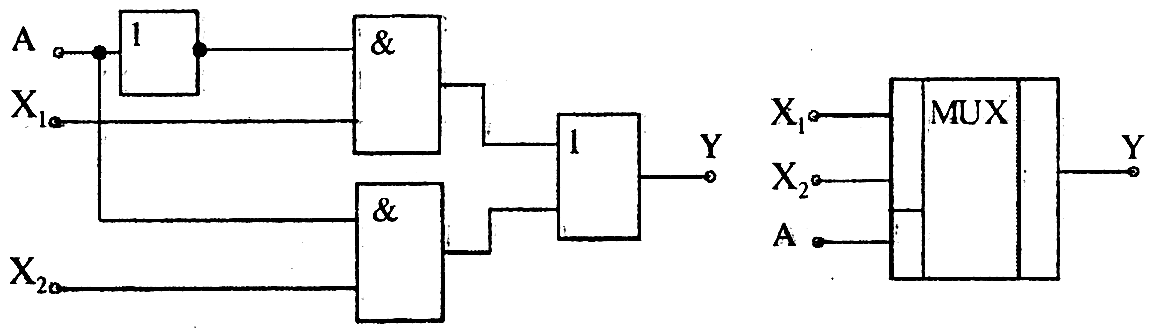

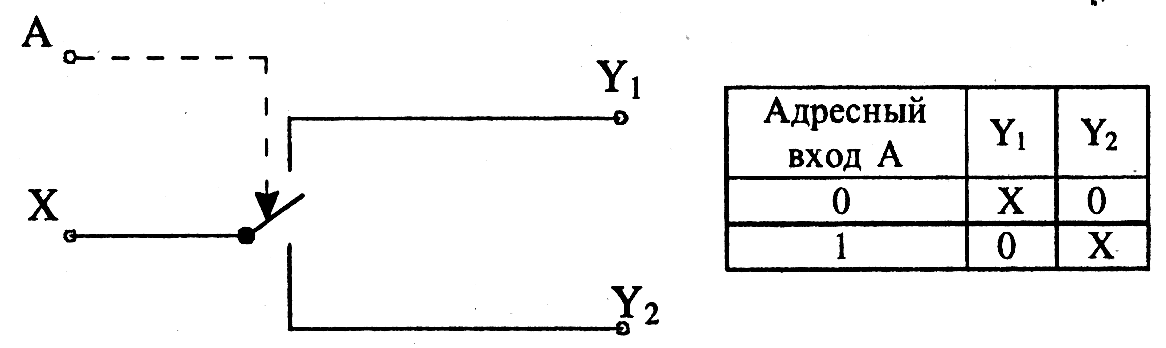

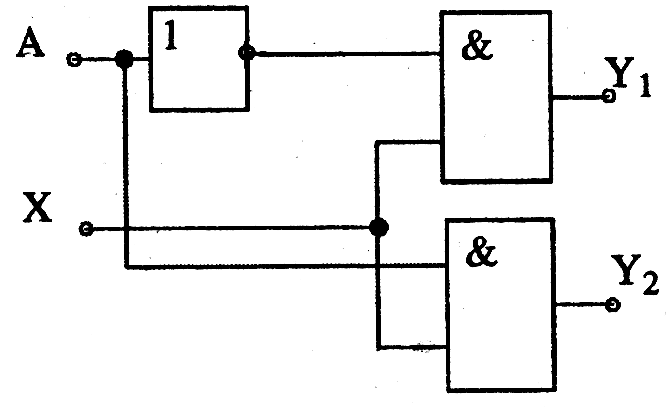

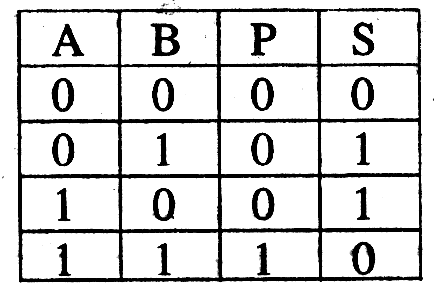

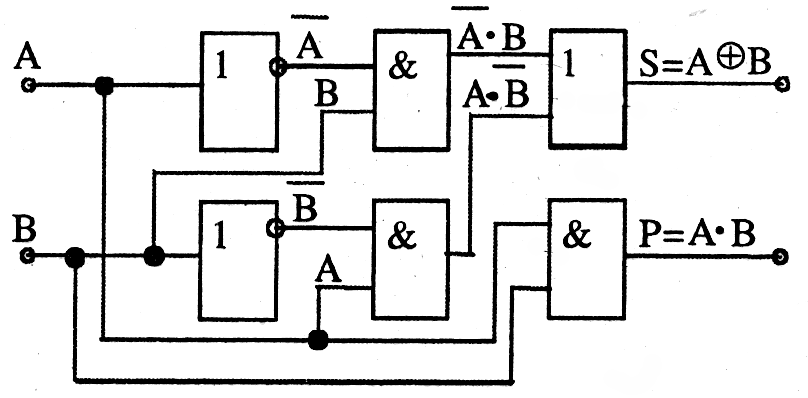

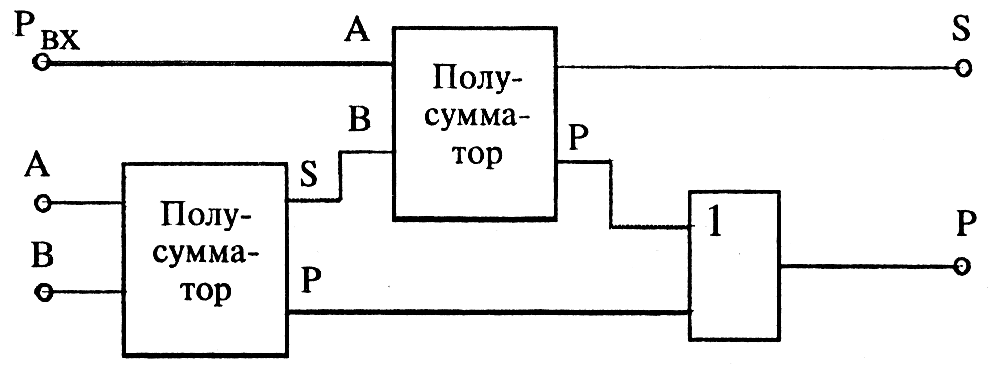

Особенности других логик. Основой базового логического элемента ЭСЛ является токовый ключ, схема которого подобна схеме дифференциального усилителя. Микросхема ЭСЛ питается отрицательным напряжением (–4 В для серии К1500). Транзисторы этой микросхемы не входят в режим насыщения, что является одной из причин высокого быстродействия элементов ЭСЛ. В микросхемах n-МОП и p-МОП используются ключи соответственно на МОП-транзисторах с n-каналами и динамической нагрузкой и на МОП-транзисторах с p-каналом. Для исключения потребления мощности логическим элементом в статическом состоянии используются комплементарные МДП-логические элементы (КМДП или КМОП-логика). Логика на основе полупроводника из арсенида галлия GaAs характеризуется наиболее высоким быстродействием, что является следствием высокой подвижности электронов (в 3…6 раз больше по сравнению с кремнием). Микросхемы на основе GaAs могут работать на частотах порядка 10 ГГц. 16. Комбинационные цифровые устройства Логические устройства разделяют на два класса: комбинационные и последовательностные. Устройство называют комбинационным, если его выходные сигналы в некоторый момент времени однозначно определяются входными сигналами, имеющими место в этот момент времени. Иначе устройство называют последовательностным или конечным автоматом (цифровым автоматом, автоматом с памятью). В последовательностных устройствах обязательно имеются элементы памяти. Выходные сигналы последовательностных устройств определяются не только сигналами, имеющимися на входах в данный момент времени, но и состоянием элементов памяти. Таким образом, реакция последовательностного устройства на определенные входные сигналы зависит от предыстории его работы. Шифратор – это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определенному двоичному коду. Число входов и выходов в полном шифраторе связано соотношением n=2m, где n – число входов, m – число выходов. Шифратор для преобразования десятиразрядного единичного кода (десятичных чисел от 0 до 9) в двоичный код. Условное изображение такого шифратора и таблица соответствия кода приведены на рис. 11.1. Используя данную таблицу соответствия, запишем логические выражения, включая в логическую сумму те входные переменные, которые соответствуют единице некоторой выходной переменной. Так, на выходе y1 будет логическая «1» тогда, когда логическая «1» будет или на входе Х1, или Х2, или Х5, или Х7, или Х9, т.е. у1=Х1+Х3+Х5+Х7+Х9.  Рис. 16.1. Схема шифратора и таблица соответствия кода Представим на рис. 16.2 схему такого шифратора, используя элементы ИЛИ.  Рис. 16.2. Шифратор на логических элементах ИЛИ Если на всех входах – логическая единица, то на всех выводах также логическая единица, что соответствует числу 0 в так называемом инверсном коде (1111). Если хотя бы на одном входе имеется логический ноль, то состояние выходных сигналов определяется наибольшим номером входа, на котором имеется логический ноль, и не зависит от сигналов на входах, имеющих меньший номер. Основное назначение шифратора – преобразование номера источника сигнала в код (например, номера нажатой кнопки некоторой клавиатуры). Дешифратором называется комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному колу. Число входов и выходов в так называемом полном дешифраторе связано соотношением m=2n, где n– число входов, а m – число выходов. Если в работе дешифратора используется неполное число выходов, то такой дешифратор называется неполным. Так, например, дешифратор, имеющий 4 входа и 16 выходов, будет неполным, а если бы выходов было только 10, то он являлся бы полным. Обратимся для примера к дешифратору К555ИД6 серии К555 (рис. 16.3).  Рис. 16.3. Схема дешифратора Дешифратор имеет 4 прямых входа, обозначенных через А1, …, А8. Аббревиатура А обозначает «адрес». Указанные входы называют адресным. Цифры определяют значения активного уровня (единицы) в соответствующем разряде двоичного числа. Дешифратор имеет 10 инверсных выходов Дешифратор – одно из широко используемых логических устройств. Его применяют для построения различных комбинационных устройств. Шифраторы и дешифраторы являются примерами простейших преобразователей кодов. Преобразователями кодов называют устройства, предназначенные для преобразования одного кода в другой, при этом часто они выполняют нестандартные преобразования кодов. Преобразователи кодов обозначают через X/Y. Рассмотрим особенности реализации преобразователя на примере преобразователя трехэлементного кода в пятиэлементный по таблице соответствия кодов, приведенной на рис. 16.4.  Рис. 16.4. Таблица соответствия кодов для преобразователя кодов Здесь через N обозначено десятичное число, соответствующее входному двоичному коду. Преобразователи кодов создают по схеме дешифратор – шифратор. Дешифратор преобразует входной код в некоторое десятичное число, а затем шифратор формирует выходной код. Схема преобразователя, созданного по такому принципу, приведена на рис. 16.5.  Рис. 16.5. Схема преобразователя кодов Мультиплексором называют комбинационное устройство, обеспечивающее передачу в желаемом порядке цифровой информации, поступающей по нескольким входам на один выход. Мультиплексоры обозначают через MUX, а также через MS. Функционально мультиплексор можно изобразить в виде коммутатора, обеспечивающего подключение одного из нескольких входов (их называют информационными) к одному выходу устройства. Кроме информационных входов в мультиплексоре имеются адресные входы и разрешающие (стробирующие). Сигналы на адресных входах определяют, какой конкретно информационный канал подключен к выходу. Если между числом информационных входов n и числом адресных входов mдействует соотношение n=2m, то такой мультиплексор называют полным. Если n<2m, то мультиплексор называют неполным. Рассмотрим функционирование двухвходового мультиплексора (2→1), который условно изображен в виде коммутатора, а состояние его входов Х1, Х2 и выхода Y приведено в таблице (рис. 16.6).  Рис. 16.6. Двухвходовый мультиплексор Исходя из таблицы, можно записать следующее уравнение: На рис. 16.7 показаны реализация такого устройства и его условное графическое обозначение. Основой данной схемы является являются две схемы совпадения на элементах И, которые при логическом уровне «1» на одном из своих входов повторяют на выходе то, что есть на другом входе.  Рис. 16.7. Реализация двухвходового мультиплексора на логических элементах И Мультиплексоры являются универсальными логическими устройствами, на основе которых создают различные комбинационные и последовательностные схемы. Мультиплексоры могут использовать в делителях частоты, триггерных устройствах, сдвигающих устройствах, для преобразования параллельного двоичного кода в последовательный и др. Демультиплексором называют устройство, в котором сигналы с одного информационного входа поступают в желаемой последовательности по нескольким выходам в зависимости от кода на адресных шинах. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. Демультиплексоры обозначают через DMX или DMS.  Рис. 16.8. Функциональная схема демультиплексора с двумя выходами Если соотношение между числом выходов n и числом адресных входов m определяется равенством n=2m, то такой демультипликатор называют полным, при n<2m демультиплексор является неполным. Рассмотрим функционирование демультипликатора с двумя выходами, который условно изображен в виде коммутатора, а состояние его входов приведено в таблице (рис. 16.8). Из этой таблицы следует:  Рис. 16.9. Реализация демультиплексора с двумя выходами на логических элементах И Функции демультиплексоров сходны с функциями дешифраторов. Дешифратор можно рассматривать как демультиплексор, у которого информационный вход поддерживает напряжение выходов в активном состоянии, а адресные входы выполняют роль входов дешифратора. Поэтому в обозначении как дешифраторов, так и демультиплексоров используются одинаковые буквы – ИД. Выпускают дешифраторы (демультиплексоры) К155ИД3, К531ИД7 и др. Сумматоры – это комбинационные устройства для сложения чисел. Рассмотрим сложение двух одноразрядных двоичных чисел, для чего составим таблицу сложения (таблицу истинности), в которой отразим значения входных чисел А и В, значение результата суммирования S и значение переноса в старший разряд P (рис. 16.10). Работа устройства, реализующего таблицу истинности, описывается следующими уравнениями: Очевидно, что по отношению к столбцу S реализуется логическая функция «исключающее ИЛИ», т.е. S=A  Рис. 16.10. Таблица истинности Устройство, реализующее таблицу (рис. 16.10), называют полусумматором, и оно имеет логическую структуру, изображенную на рис. 16.11. Поскольку полусумматор имеет только два входа, он может использоваться для суммирования лишь в младшем разряде.  Рис. 16.11. Схема полусумматора При суммировании двух многоразрядных чисел для каждого разряда (кроме младшего) необходимо использовать устройство, имеющее дополнительный вход переноса.  Рис. 16.12. Схема полного сумматора Такое устройство (рис. 16.12) называют полным сумматором и его можно представить как объединение двух полусумматоров (Рвх – дополнительный вход переноса). Сумматор обозначают через SM. Последовательностные цифровые устройства Триггер – простейшее последовательностное устройство, которое может находиться в одном из двух возможных состояний и переходить из одного состояния в другое под воздействием входных сигналов. Триггер является базовым элементом последовательностных логических устройств. Триггеры классифицируют по следующим признакам:

Различают асинхронные и синхронные триггеры. Асинхронный триггер изменяет свое состояние непосредственно в момент появления соответствующего информационного сигнала. Синхронные триггеры реагируют на информационные сигналы только при наличии соответствующего сигнала на входе синхронизации С (строб). По функциональным возможностям триггеры разделяются на следующие классы:

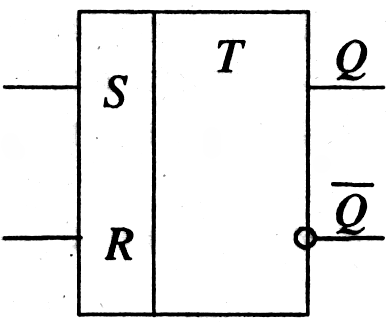

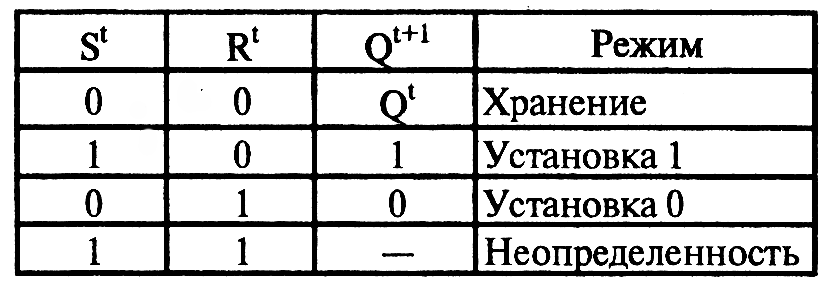

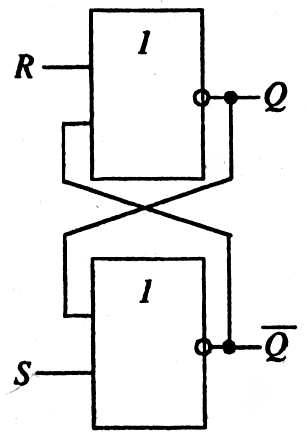

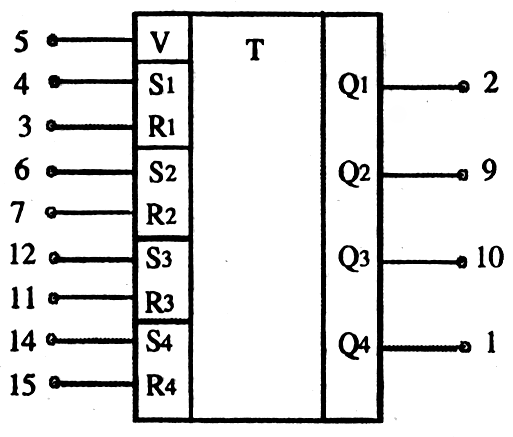

Входы триггеров обычно обозначают следующим образом: S – вход для установки состояния «1»; R – вход для установки состояния «0»; J – вход для установки в состояние «1» в универсальном триггере; К – вход для установки в состояние «0» в универсальном триггере; Т – счетный (общий) вход; D – вход для установки в состояние «1» или в состояние «0»; V – дополнительный управляющий вход для разрешения приема информации (иногда используют букву Е вместо V). Рассмотрим асинхронный RS-триггер, имеющий условное графическое обозначение, приведенное на рис. 16.13. Триггер имеет два информационных входа: S и R. Закон функционирования триггеров удобно описывать таблицей переходов (таблицей истинности) (рис. 16.14). Через St, Rt, Qt обозначены соответствующие логические сигналы, имеющие место в некоторый момент времени t, а через Qt+1 – выходной сигнал в следующий момент времени t+1.   Рис. 16.13. RS-триггер Рис. 16.14. Таблица истинности Комбинацию входных сигналов St=1, Rt=1 часто называют запрещенной, так как после нее триггер оказывается в состоянии (1 или 0), предсказать которое заранее невозможно. Подобных ситуаций следует избегать. Рассмотренный триггер может быть реализован на двух элементах ИЛИ-НЕ (рис. 16.15). Микросхема К564ТР2 содержит 4 асинхронных RS-триггера и один управляющий вход (рис. 16.16). При подаче на вход V низкого уровня выходы триггеров отключаются от выводов микросхем и переходят в третье, так называемое высокоимпедансное, состояние. При подаче на вход V логического сигнала «1» триггеры работают в соответствии с таблицей истинности (рис. 16.14).   Рис. 16.15. Триггер Рис. 16.16. Микросхема К564ТР2 на элементах ИЛИ-НЕ Счетчики импульсов – это последовательностное цифровое устройство, обеспечивающее хранение слова информации и выполнение над ним микрооперации счета, заключающейся в изменении значения числа в счетчике на 1. По существу счетчик представляет собой совокупность соединенных определенным образом триггеров. Основной параметр счетчика – модуль счета. Это максимальное число единичных сигналов, которое может быть сосчитано счетчиком. Счетчики обозначаются через СТ. Счетчики классифицируют: по модулю счета:

по направлению счета:

по способу формирования внутренних связей:

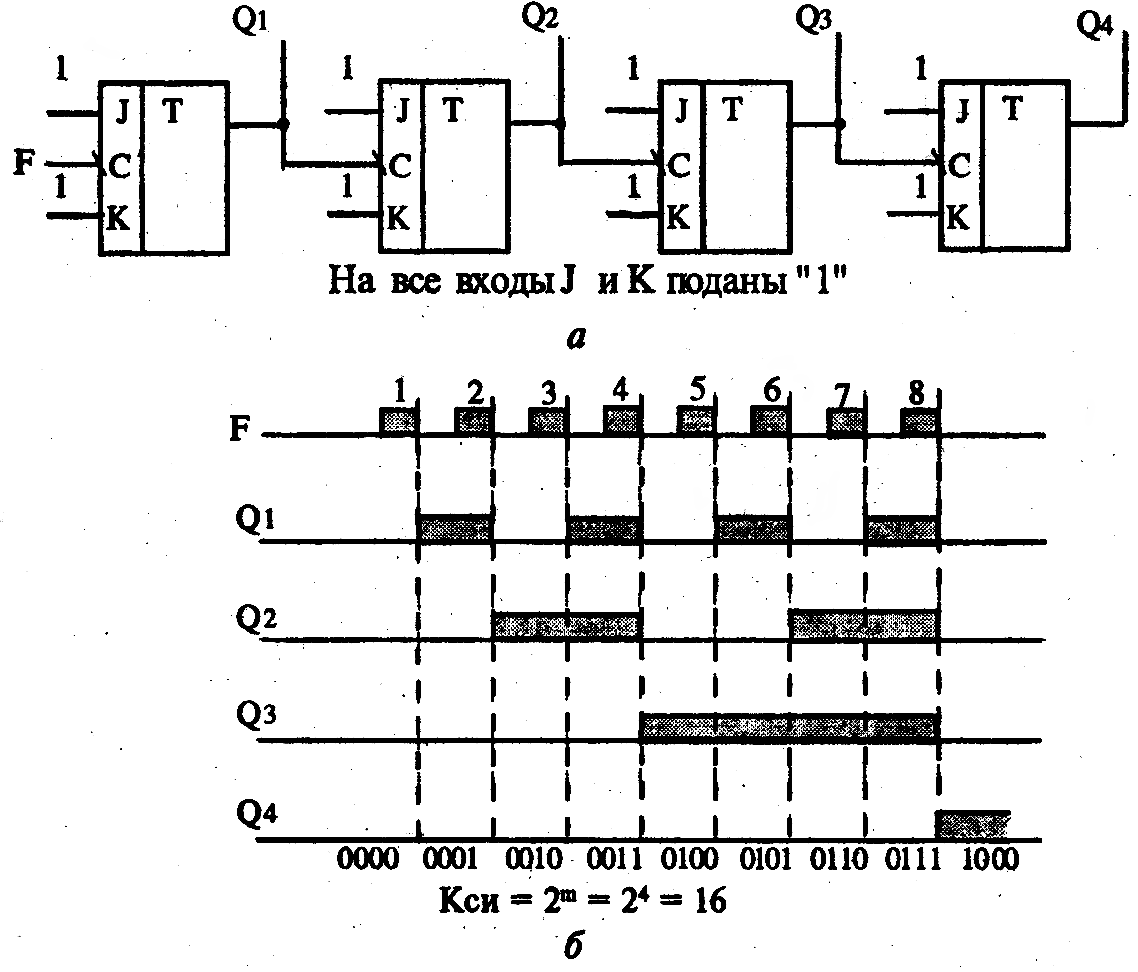

Рис. 16.17. Суммирующий счетчик на JK –триггерах Рассмотрим суммирующий счетчик (рис. 16.17,а). Такой счетчик построен на четырех JK-триггерах, которые при наличии на обоих входах логического сигнала «1» переключаются в моменты появления на входах синхронизации отрицательных перепадов напряжения. Временные диаграммы, иллюстрирующие работу счетчика, приведены на рис. 16.17,б. Через Ксн обозначен модуль счета (коэффициент счета импульсов). Состояние левого триггера соответствует младшему разряду двоичного числа, а правого – старшему разряду. В исходном состоянии на всех триггерах установлены логические нули. Каждый триггер меняет свое состояние лишь в тот момент, когда на него действует отрицательный перепад напряжения. Таким образом, данный счетчик реализует суммирование входных импульсов. Из временных диаграмм (рис. 16.17,б) видно, что частота каждого последующего импульса в два раза меньше, чем предыдущая, т.е. каждый триггер делит частоту входного сигнала на два, что и используется в делителях частоты. Регистр – это последовательностное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними. Регистр представляет собой упорядоченную последовательность триггеров, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами. Типичными является следующие операции:

Фактически любое цифровое устройство можно представить в виде совокупности регистров, соединенных друг с другом при помощи комбинационных цифровых устройств. Регистры классифицируются по следующим видам:

В свою очередь сдвигающие регистры делятся:

– параллельные; – последовательные;

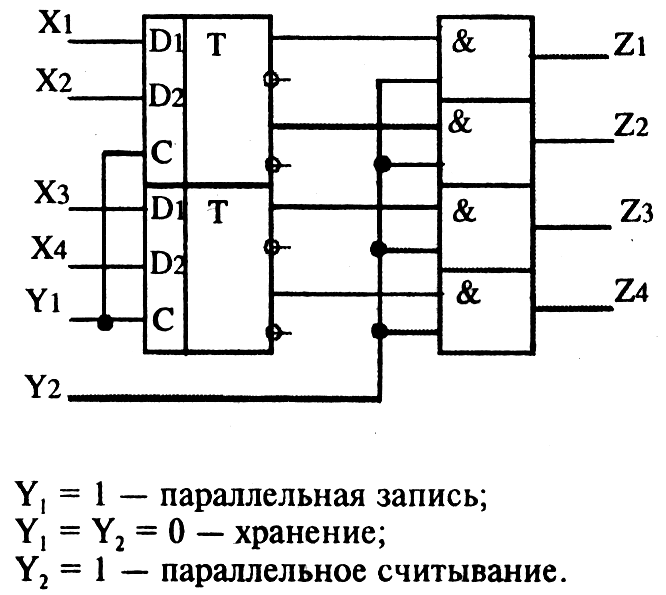

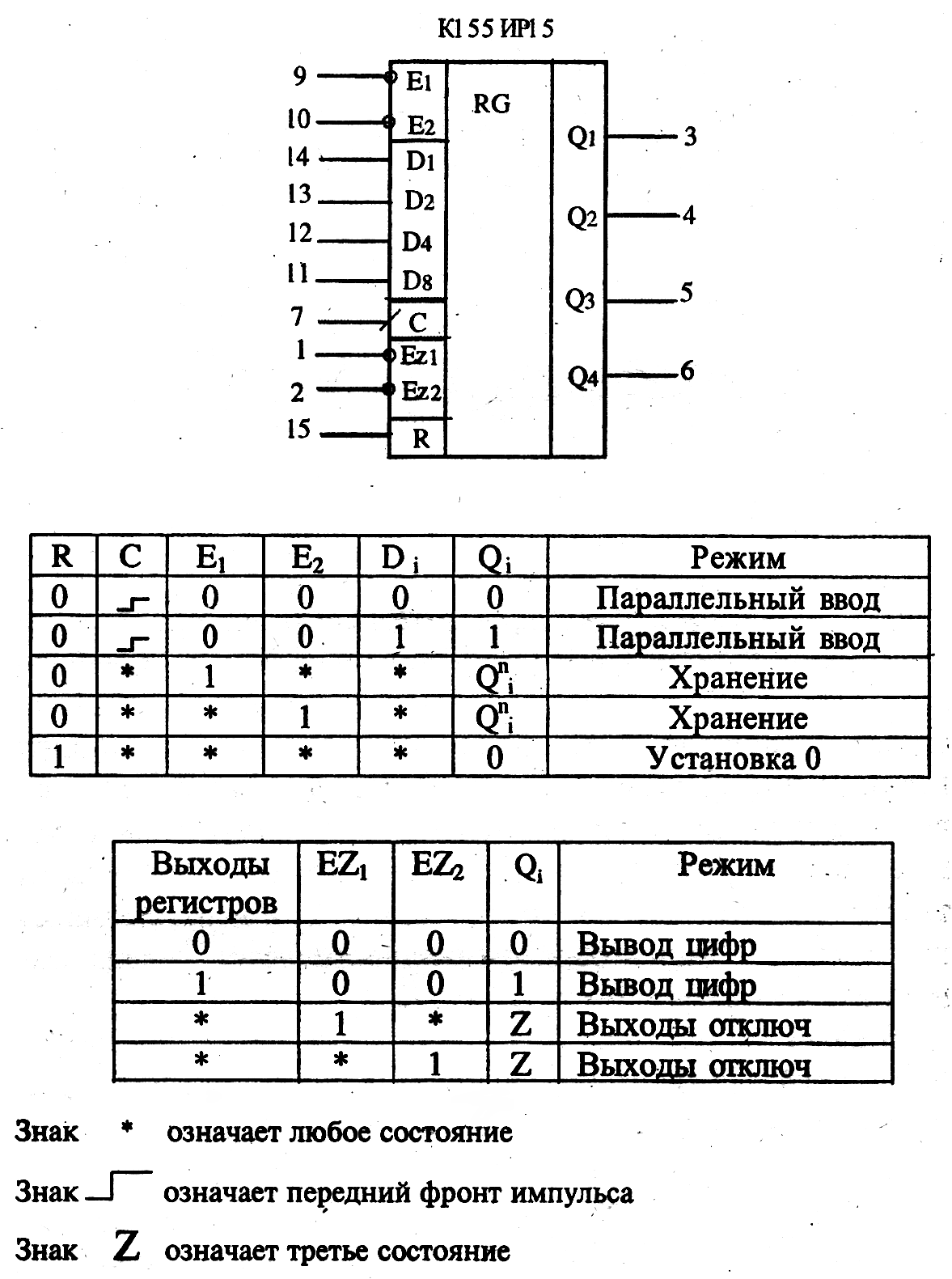

– однонаправленные; – реверсивные. Рассмотрим накопительный регистр с параллельными вводом и выводом информации (рис. 16.18). Основой регистра являются D-триггеры, которые на своих выходах повторяют значения сигналов на входах Х1 – Х4 (информационные входы) при логическом сигнале 1 на входе синхронизации (т.е. осуществляется параллельный ввод входной информации в регистр).  Рис. 16.18. Накопительный регистр с параллельными вводом и выводом информации На четырех двухвходовых элементах «И» реализованы схемы совпадения, входные сигналы которых совпадают с выходными сигналами триггеров в том случае, когда на вход Y2 подана логическая единица. Таким образом осуществляется параллельный вывод информации. В качестве примера рассмотрим микросхему регистра К155ИР15. Приведем условное обозначение и таблицы внутренних и выходных состояний (рис. 16.19).  |