Лабораторная работа Исследование работы однофазных неуправляемых выпрямителей

Скачать 1.91 Mb. Скачать 1.91 Mb.

|

|

Содержание отчёта Отчёт по работе должен содержать: цель работы, исходные данные, схему инвертирующего усилителя, расчёт, результаты моделирования работы усилителя в среде Multisim, осциллограммы входного и выходного сигналов, выводы по работе. Лабораторная работа № 3. Исследование работы логических элементов и триггеров Цель работы: Изучение принципа функционирования и характеристик логических элементов и триггеров. Общие сведения В ЭВМ, импульсных и других цифровых устройствах широко применяются логические элементы. Каждый логический элемент выполняет вполне определенную логическую операцию. Основными логическими операциями являются: логическое отрицание НЕ (инверсия), логическое сложение ИЛИ (дизъюнкция), логическое умножение И (конъюнкция) (см. таблицу 3.1). К базовым логическим элементам относятся элементы Пирса и Шеффера (см. таблицу 3.2). На основе этих простых операций могут строиться и более сложные. Для описания логических операций используется алгебра логики. Алгебра логики широко применяется в теории цифровой техники, в которой используются устройства, имеющие два устойчивых состояния равновесия. При этом одно из состояний, соответствующие, например, высокому уровню напряжения, обозначается единицей, а соответствующее низкому уровню напряжения - нулем. Уровень выходного напряжения логического элемента зависит от уровня входного (или нескольких входных) напряжений. Эта связь отображается таблицей состояний (таблицей истинности). Таблица 3.1 – Формы отображения основных логических функций

Таблица 3.2 – Формы отображения базовых логических функций

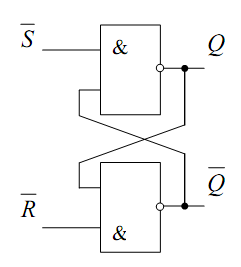

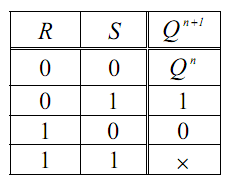

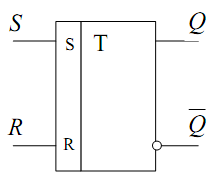

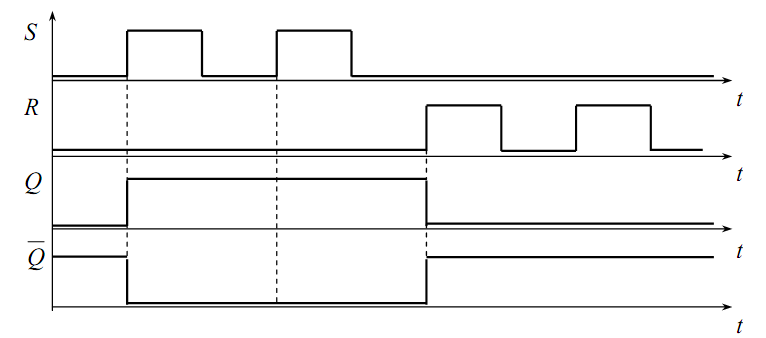

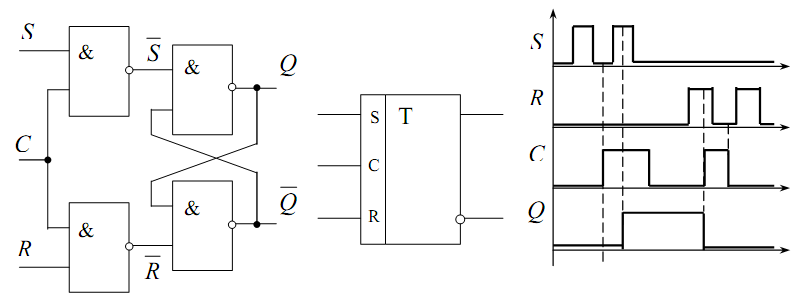

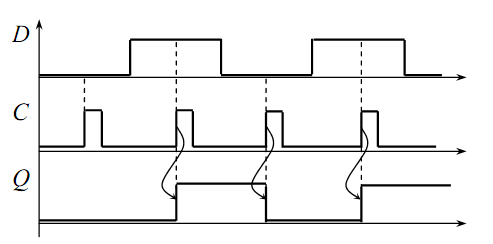

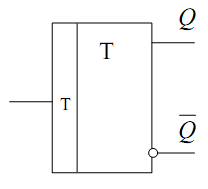

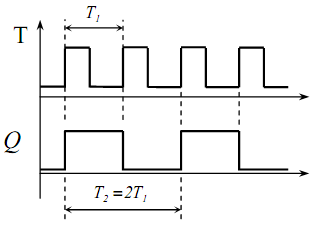

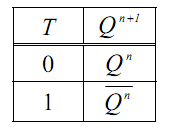

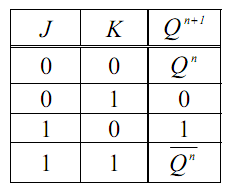

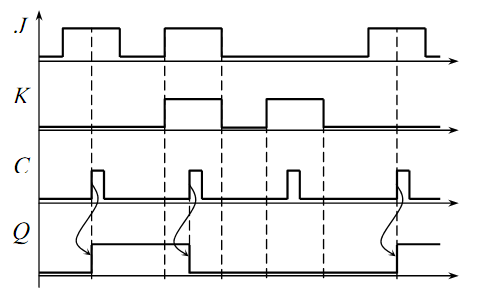

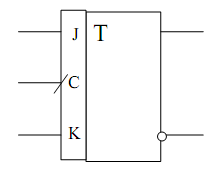

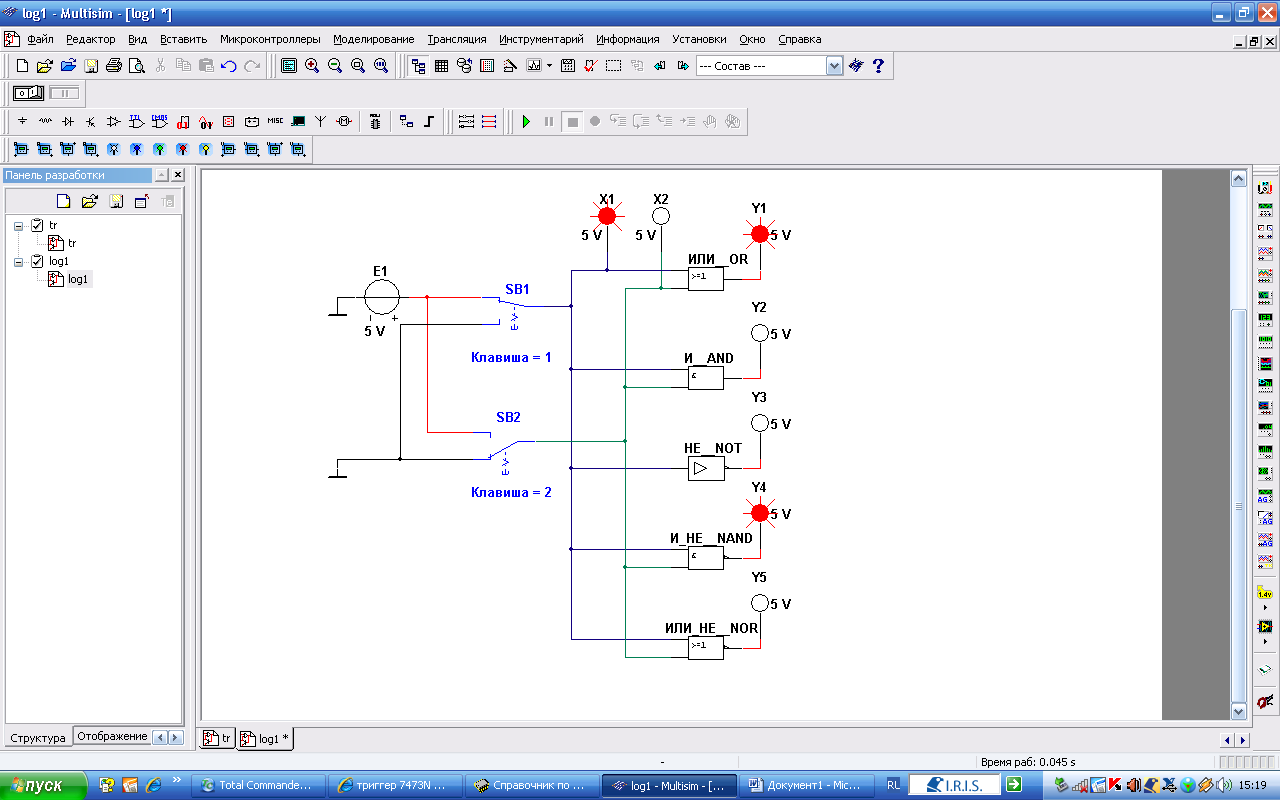

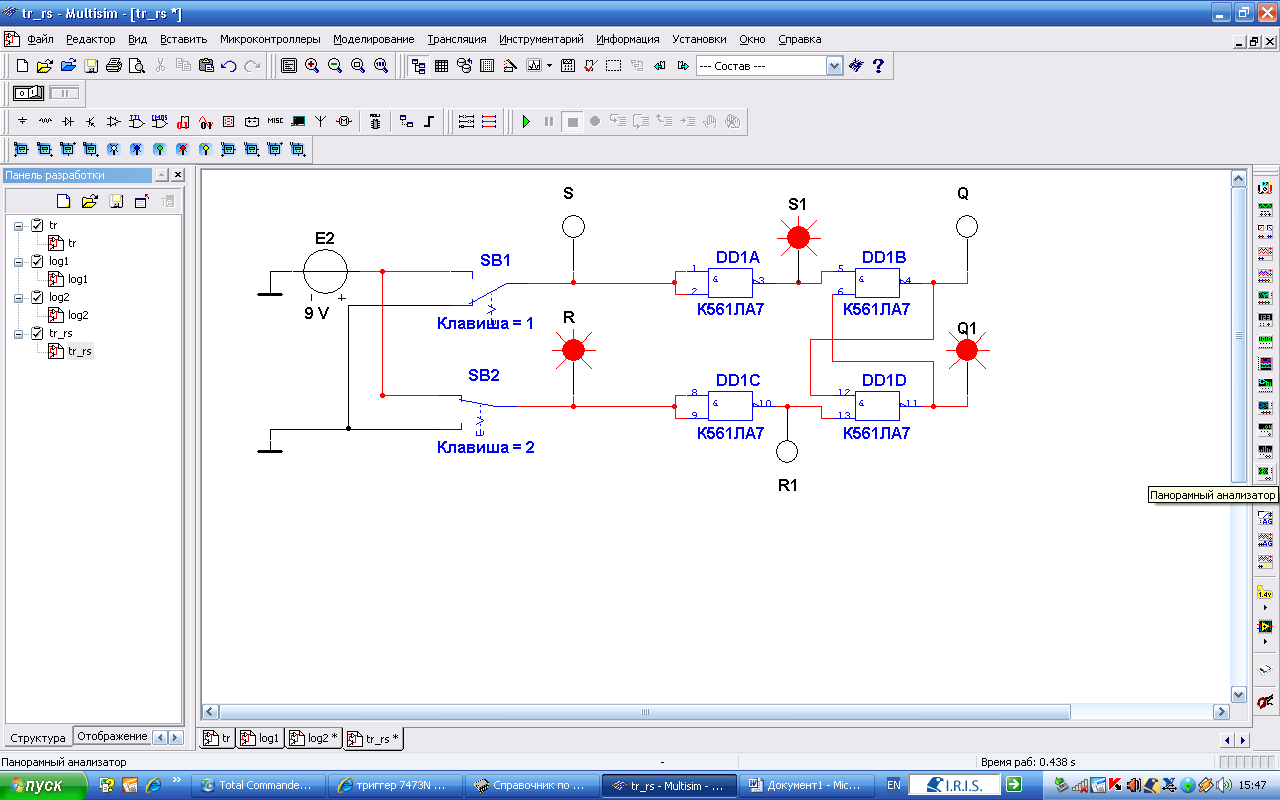

Триггер – это устройство последовательностного типа с двумя устойчивыми состояниями равновесия, предназначенное для записи и хранения информации. Под действием входных сигналов триггер может переключаться из одного устойчивого состояния в другое. При этом напряжение на его выходе скачкообразно изменяется с низкого уровня на высокий или наоборот. По способу записи информации триггеры делят на асинхронные, которые переключаются в момент подачи входного сигнала, и синхронные (тактируемые), которые переключаются только при подаче синхронизирующих импульсов, а момент переключения связан с определённым уровнем синхросигнала (статические триггеры) или с моментом перепада напряжения на тактируемом входе (динамические триггеры). Как правило, триггер имеет два выхода: прямой Q и инверсный Н  аибольшее распространение в цифровых устройствах получили триггеры RS(рисунок 3.1, 3.2), D(рисунок 3.3),JK(рисунок 3.4) и T(рисунок 3.5).    а) б) в)  г) Рисунок 3.1 – Асинхронный RS-триггер: а – условное графическое изображение; б – схема реализации RS-триггера на базовых элементах И-НЕ; в – таблица истинности; г – временная диаграмма, иллюстрирующая работу триггера а) б) в)  Рисунок 3.2 – Синхронный RS-триггер: а –схема реализации RS-триггера на базовых элементах И-НЕ; б – условно-графическое обозначение; в – временная диаграмма, иллюстрирующая работу триггера RS–триггер имеет два управляющих входа S (set) и R (reset), с помощью которых выполняются установки триггера в то или иное состояние: Q = 1 при S=1 и R=0 ( установка триггера); Q = 0 при S=0 и R=1 (сброс триггера); Q n+1=Qn при S=R=0 (режим хранения предыдущего состояния); S=R=1 – запрещенная комбинация управляющих сигналов, которая может привести к неопределенному состоянию триггера. Рассматриваемый триггер является асинхронным, т.к. изменение его состояния происходит непосредственно с поступлением управляющих сигналов. Принцип работы асинхронного RS-триггера поясняется временными диаграммами, показанными на рисунке 3.1, г. Схемотехнически RS-триггер может быть реализован на элементах 2ИЛИ-НЕ (рисунок 3.1, б) и 2И-НЕ с использованием перекрестных положительных обратных связей. В триггере на элементах 2И-НЕ изменение состояния происходит при низких уровнях сигналов S и R. В синхронных RS-триггерах могут быть использованы различные способы синхронизации. На рисунке 3.2, а и б показаны схемотехническая реализация и условное обозначение RS-триггера с синхронизацией по уровню (высокому). На рисунке 3.2, в приведены диаграммы работы такого триггера. Изменение состояний происходит только при высоких уровнях сигнала синхронизации С. В RS-триггере с синхронизацией по фронту изменение состояния происходит в момент изменения уровня сигнала С. При этом возможна синхронизация как по переднему, так и по заднему фронту (срезу). Такие триггеры строятся по двухступенчатой схеме и в них процессы приема и записи данных разделены во времени. Отличительной особенностью D-триггера (триггера задержки) является то, что он сохраняет информацию, поступившую на D-вход в предыдущем такте работы до прихода синхроимпульса, т.е. его состояние может изменяться с задержкой на один такт. Синхронизация работы производится по переднему или заднему фронту. Условное обозначение D-триггера с синхронизацией по переднему фронту и диаграммы его работы показаны на рисунке 3.3. а) б) в)    Рисунок 3.3 – D-триггер: а – условное графическое изображение; б – схема реализации D-триггера на базовых элементах И-НЕ; в –временная диаграмма, иллюстрирующая работу триггера Т-триггеры иначе называются счетными и применяются для построения счетчиков и делителей частоты. Такой триггер имеет один тактовый вход и его состояние меняется каждый раз при подаче счетного импульса Т=1 и остается неизменным при Т=0. Таблица состояния триггера приведена, его обозначение и диаграммы работы приведены на рисунке 3.4. Как видно из диаграмм, Т-триггер делит частоту входных импульсов в 2 раза. Для получения больших значений коэффициента деления частоты применяется каскадное соединение Т-триггеров. Как самостоятельное изделие Т-триггер в виде интегральной микросхемы не выпускается и при необходимости реализуется на базе других типов триггеров.   а) б) в) а) б) в) Рисунок 3.4 – Т-триггер: а – таблица истинности; б – условное графическое изображение; в –временная диаграмма, иллюстрирующая работу триггера JK-триггер имеет два управляющих входа J (jump) и K (keep) и функционирует подобно RS-триггеру, но при этом не имеет запрещенных комбинаций управляющих сигналов. J - вход подобен S – входу, а K-вход подобен R-входу. При всех комбинациях сигналов на входе, кроме J=K=1, он действует подобно RS-триггеру. При J=K=1 в каждом такте происходит «опрокидывание» триггера и его состояние меняется на противоположное (рисунок 3.5, а). На рисунке 3.5, б, в показаны условное обозначение JK-триггера c синхронизацией по переднему фронту и его временные диаграммы работы. JK-триггеры относятся к универсальным устройствам в отношении их применения как для построения других типов триггеров (рисунок 3.5, г), так и более сложных устройств последовательного принципа действия. Во всех сериях цифровых интегральных микросхем выпускаются JK-триггеры с различными функциональными возможностями.   а) б) в) а) б) в) г)    Рисунок 3.5 – JK-триггер: а – таблица истинности; б – условное графическое изображение; в –временная диаграмма, иллюстрирующая работу триггера; б – реализация D-, T- иRS- триггеров на основе JK-триггера. Порядок выполнения работы 1 В программе Multisim собрать схему для испытания основных и базовых логических элементов (см. рисунок 3.6) ОR (ИЛИ), AND (И), NOT (НЕ), NAND (И-НЕ) и XOR (ИЛИ-НЕ), расположенных в библиотеке Misc Digital/TIL с уровнем высокого напряжения 5 В. В схему включены ключи SB1 и SB2, пробники Х1, Х2 и Y1..Y5 с пороговыми напряжениями 5 В. Если входной или выходной сигнал элемента равен логической единице, то включенный на выходе этого элемента пробник светится. Результаты моделирования занести в таблицу 3.3  Рисунок 3.6 – Схема для исследования основных и базовых логических элементов Таблица 3.3 – Результаты моделирования

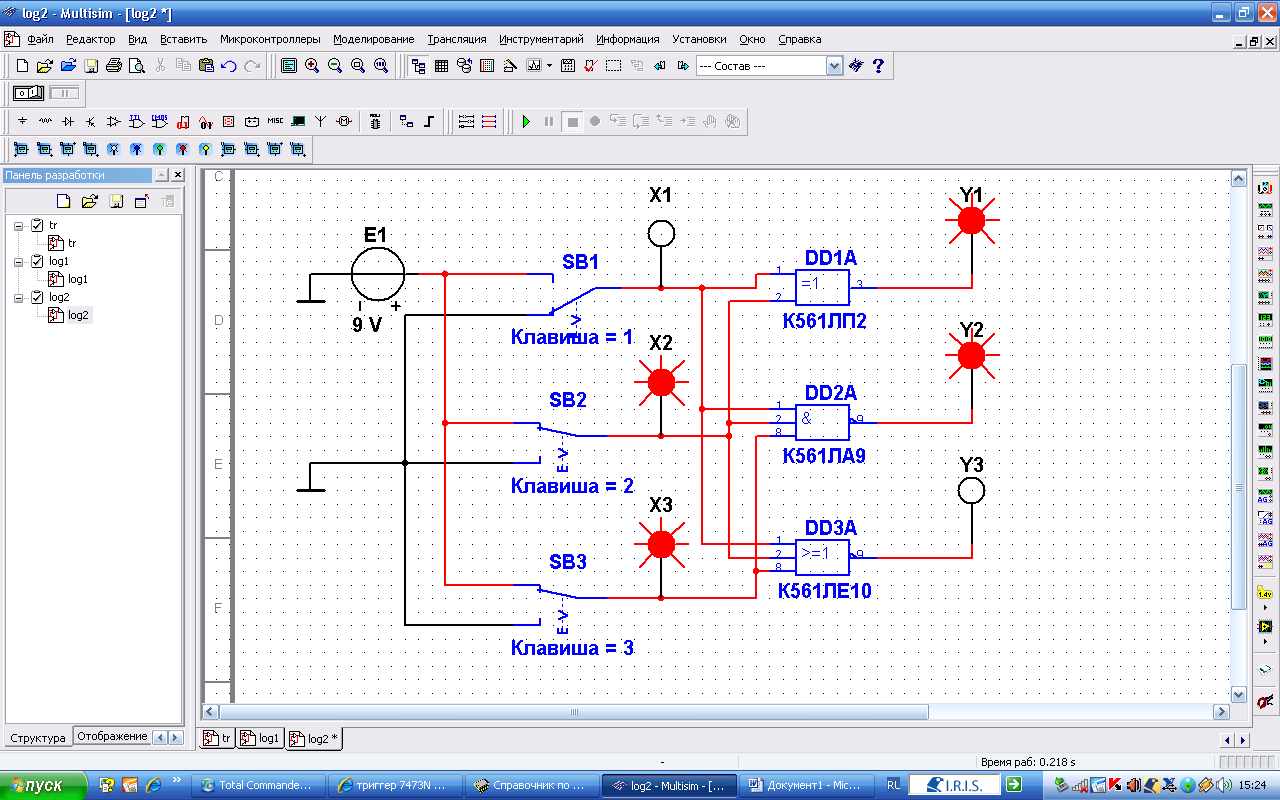

2 По заданию преподавателя (таблица 3.4) исследовать работу 3-х логических элементов одной из серий интегральных микросхем (рисунок 3.7), предварительно выписав из справочника их параметры и условное обозначение. Составить таблицу истинности для данных элементов.  Рисунок 3.7 – Схема для исследования логических элементов серии К561 Таблица 3.4 – Исходные данные

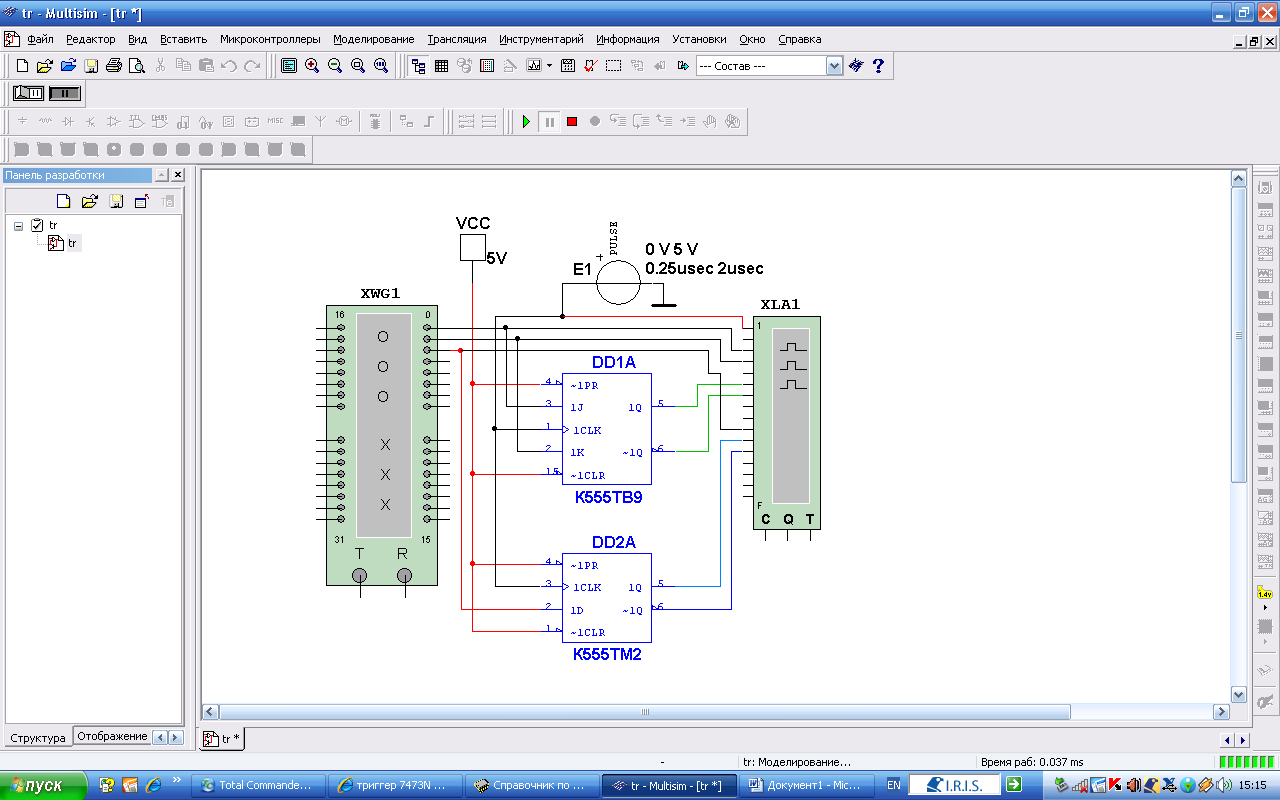

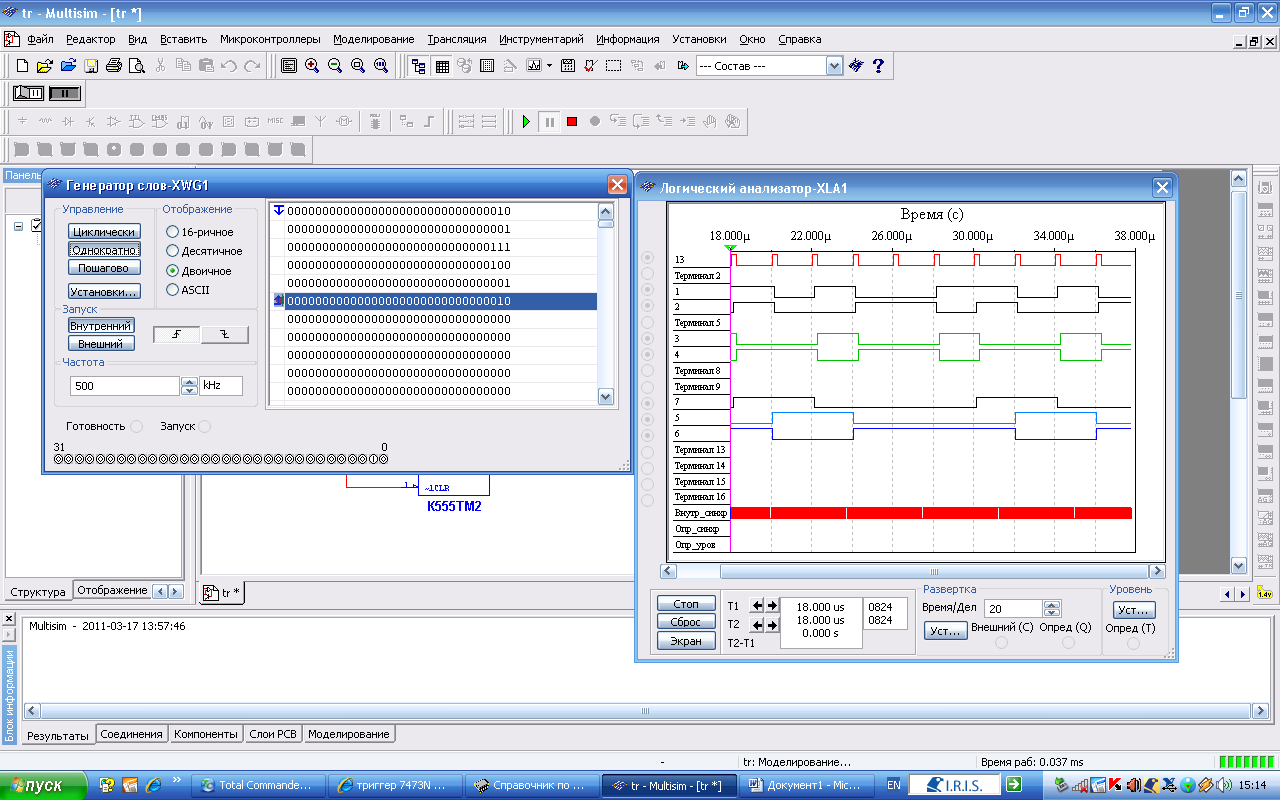

3 В программе Multisim собрать схему исследования RS-триггера на логических элементах И-НЕ, заданной преподавателем серии (таблица 3.4 рисунок 3.8).  Рисунок 3.8 – Схема RS-триггера на логических элементах серии К561 Воспользовавшись порядком засвечивания пробников и задавая коды (00, 01, 10) состояния ключей SB1 и SB2 (входных сигналов), составить таблицу истинности RS-триггера. 4 В программе Multisim собрать схему испытания триггеров JK и D(рисунок 3.9) по заданию преподавателя. В схему включены: генератор XWG1 (частота fг = 500 кГц); логический анализатор XLA1.  Рисунок 3.9 – Схема для исследования JK- и D-триггеров На С выходов 1 и 2 генератора XWG1 сигналы подаются на управляющие входы 1J и 1К JK-триггера, с выхода 3 на вход 1DD-триггера. В качестве примера введём в первые шесть ячеек памяти генератора трёхразрядные кодовые комбинации (см. рисунок 3.10): 010, 100, 111, 001, 100, 010.  Рисунок 3.10 – Цифровые комбинации и временные диаграммы триггеров Провести моделирование работы триггеров, по временным диаграммам составить и заполнить для них таблицы истинности. 5 Сделать выводы по результатам работы. | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||