Лабораторная работа 2 по дисциплине Схемотехника Мультиплексоры и дешифраторы студент группы вм91б Обухов А. С

Скачать 0.72 Mb. Скачать 0.72 Mb.

|

|

МИНОБРНАУКИ РОССИИ Федеральное государственное бюджетное образовательное учреждение высшего образования «Юго-Западный государственный университет» Кафедра вычислительной техники Лабораторная работа № 2 по дисциплине «Схемотехника»: «Мультиплексоры и дешифраторы» Выполнил: студент группы ВМ-91б Обухов А.С. Проверил: преподаватель кафедры ВТ Коломиец Е.А. Курск 2021 Цель работы: Изучение принципов организации типовых функциональных узлов комбинационного типа: мультиплексоров и дешифраторов. Изучение методов реализации логических функций на мультиплексорах и дешифраторах. Приобретение навыков в сборке, наладке и исследовании схем. Вариант 12: Десятичные номера наборов  для исследования логического устройства на базе мультиплексора: 1, 5, 9, 12, 13, 14, 15. для исследования логического устройства на базе мультиплексора: 1, 5, 9, 12, 13, 14, 15. Десятичные номера наборов  для исследования логического устройства на базе дешифратора: 0, 1, 2, 3, 12, 13, 14, 15. для исследования логического устройства на базе дешифратора: 0, 1, 2, 3, 12, 13, 14, 15. Ход работы: Построим карту Карно для определения выходного значения (Y) и переменных, поступающих на информационные входы (D0…D7).

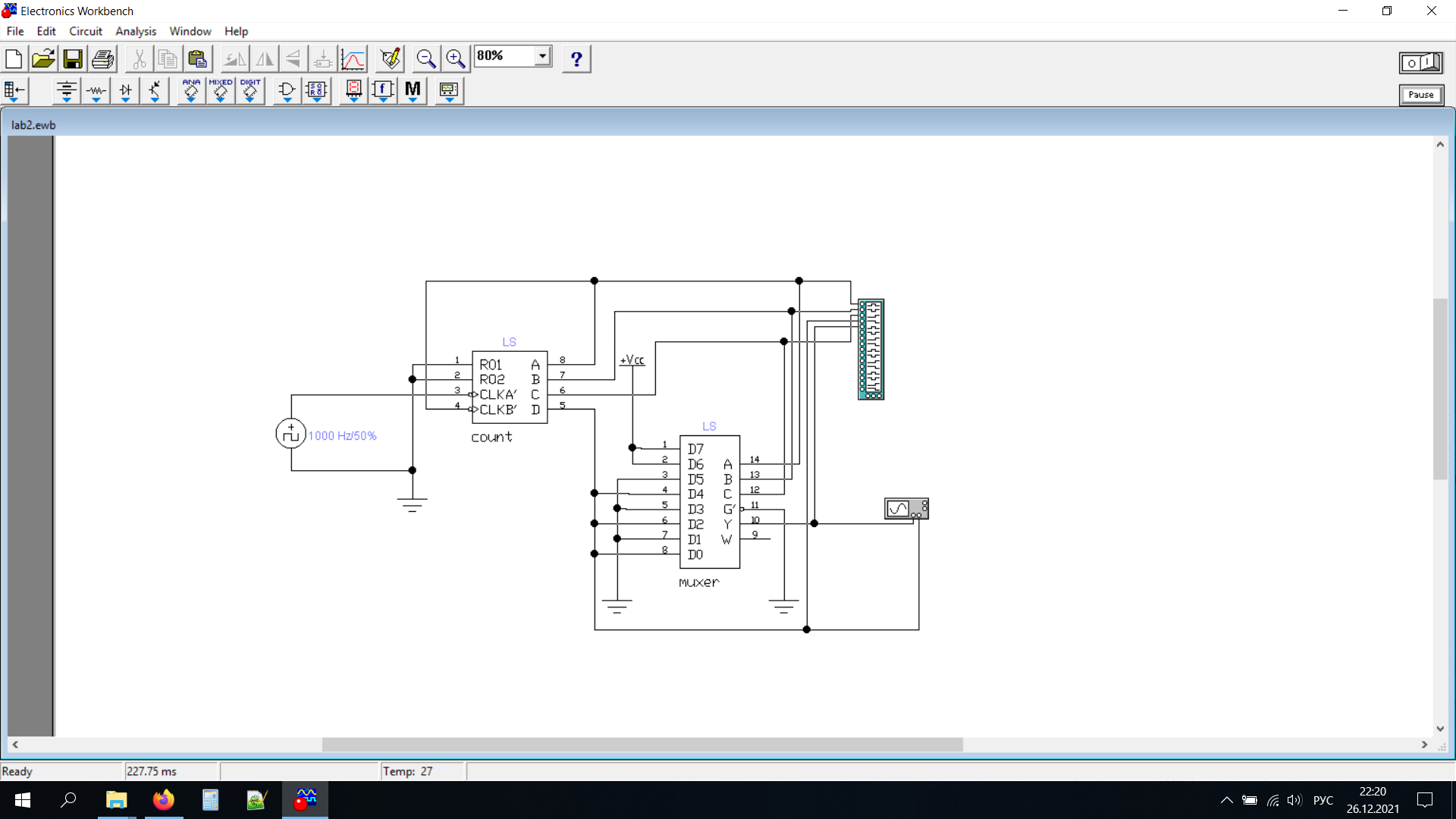

D0=d D1=0 D2=d D3=0 D4=d D5=0 D6=1 D7=1 На базе полученных данных соберём схему, приведённую на рисунке 1.  Рис. 1. Схема установки для исследования логического устройства на базе мультиплексора По карте Карно определим функцию Y (так как d не является адресным входом, то при написании функции его не учитываем) для проверки результата.

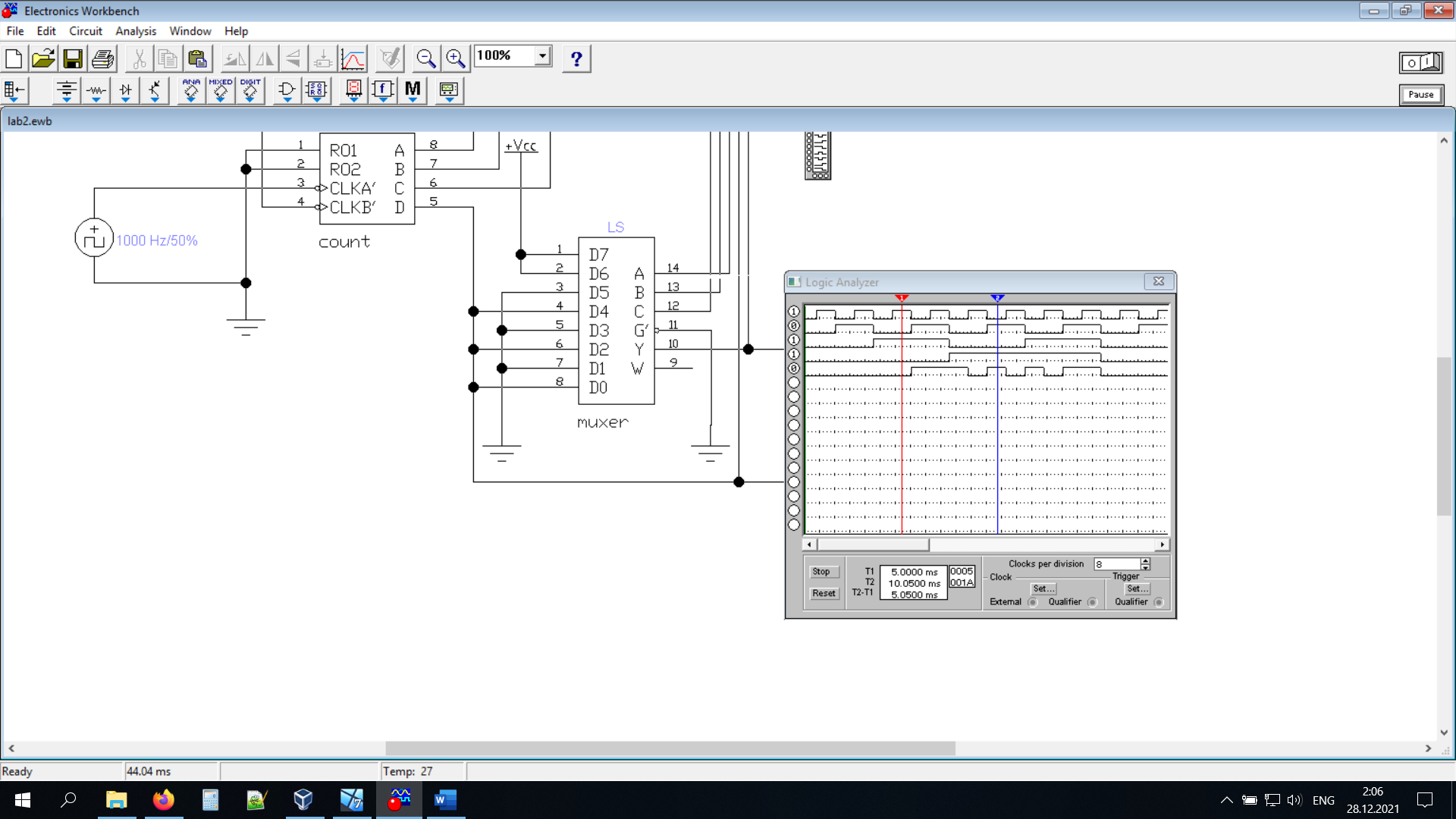

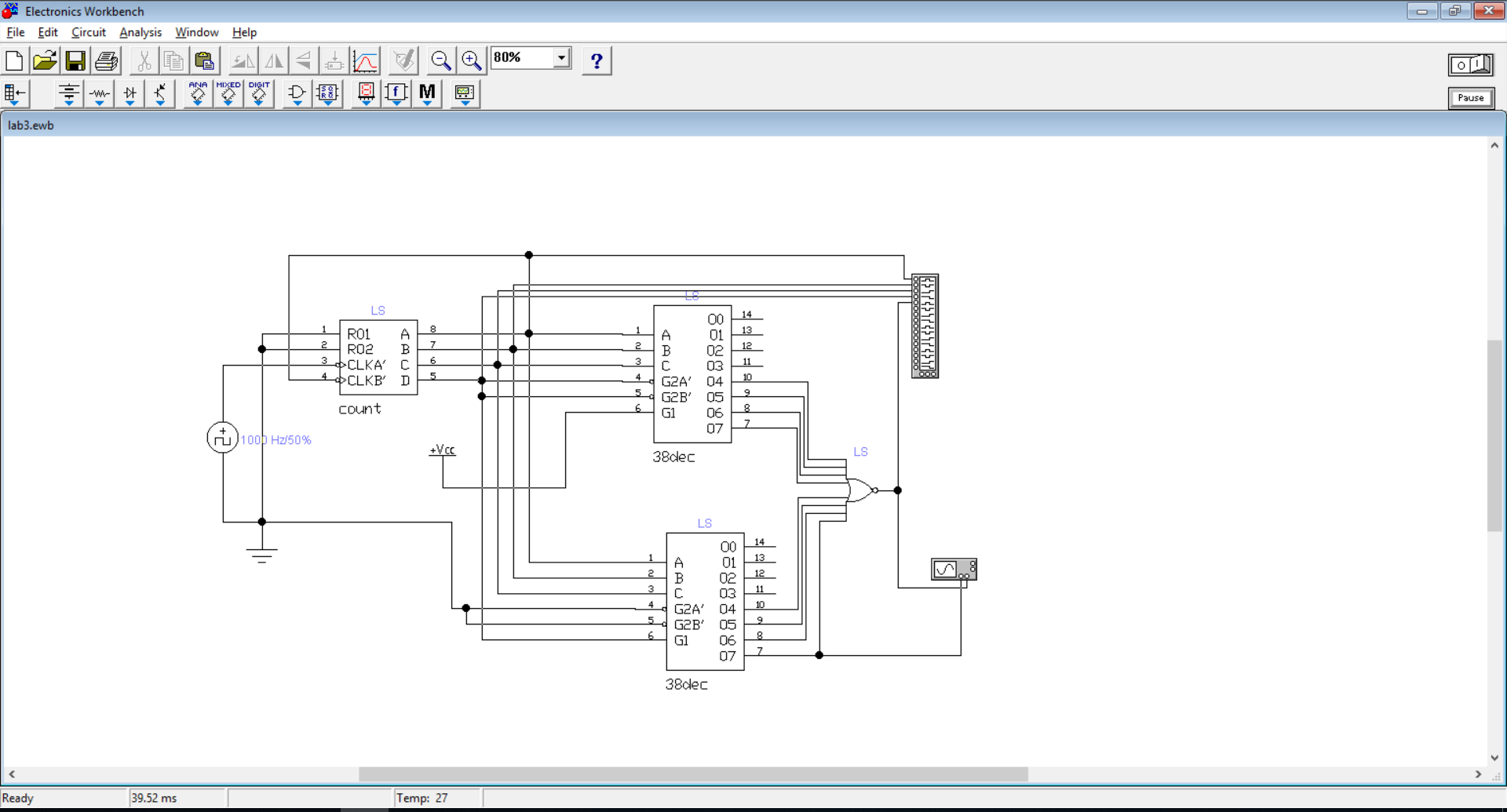

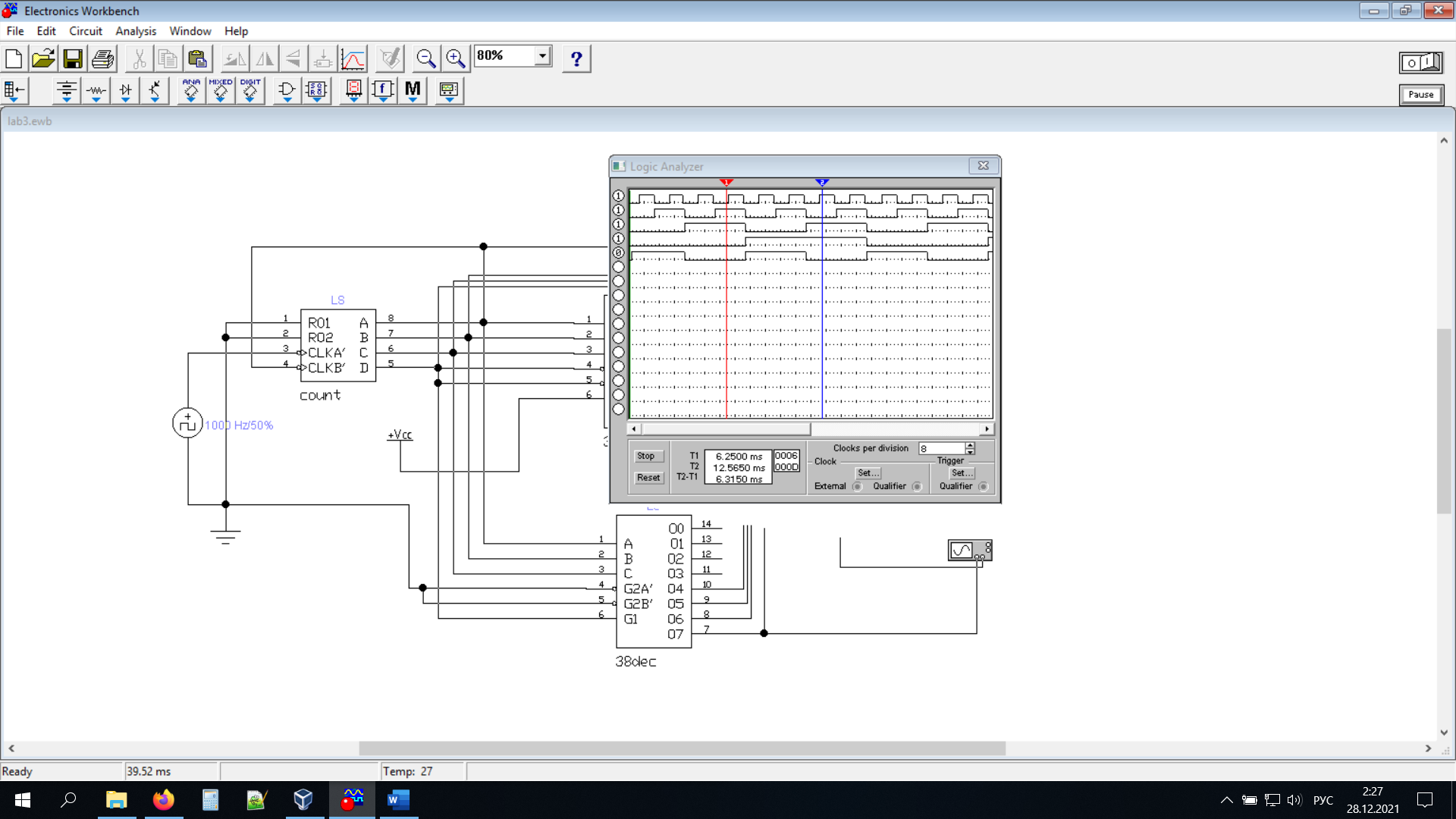

Рис. 2. Временные диаграммы входных и выходных сигналов На основе исходных данных соберём схему на основе дешифраторов “3×8”, приведённую на рисунке 3.  Рис. 3. Схема установки для исследования логического устройства на базе дешифраторов   Рисунок 4 – Временные диаграммы входных и выходных сигналов Выполним проверку

|

cd

cd