это капец. Лабораторная работа 3 Многоразрядное арифметикологическое устройство Студент 2 курса гр. 23

Скачать 321.91 Kb. Скачать 321.91 Kb.

|

|

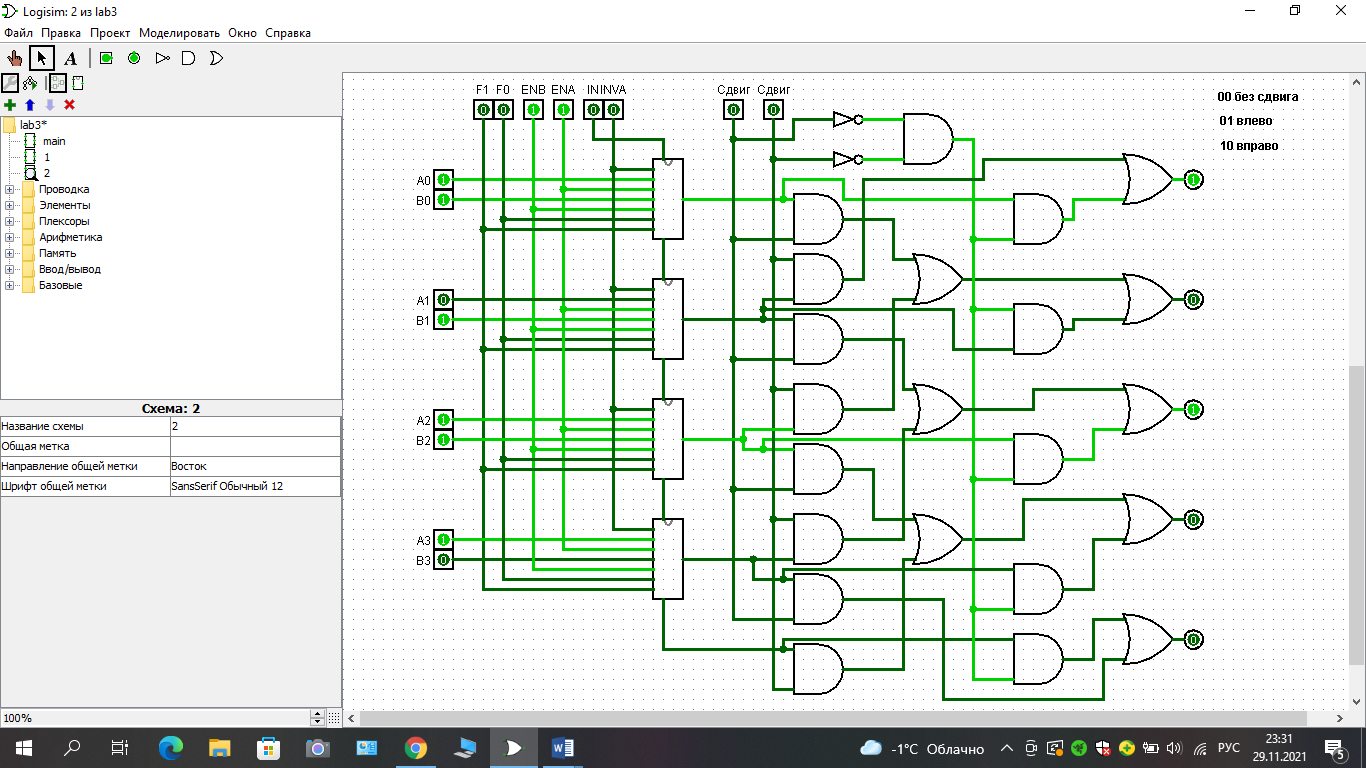

Министерство образования и науки Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования «Башкирский Государственный Университет» Лабораторная работа №3 Многоразрядное арифметико-логическое устройство Выполнила: Студент 2 курса гр. 23 Мухамадиева Лилия. Проверил: Доцент кафедры ПиЭИ Валеев Н.Ф. УФА 2021 Задача: Построить схему многоразрядного арифметико-логического устройства. Арифметико-логическое устройство (АЛУ). Это устройство может вычислять одну из четырёх следующих функций: А И В, А ИЛИ В, НЕ В, А + В. Последняя операция учитывает так же вход carry in. Выбор функции зависит от того, какие сигналы поступают на линии F1 и F0: 00, 01, 10 или 11. Построить одноразрядное АЛУ (секция). Затем из этих секций построить 8 (или 4 -х)-разрядное АЛУ, соединив их между собой. Соединить выход АЛУ с схемой сдвига*. Схема с тремя режимами: без сдвига, сдвиг вправо, сдвиг влево. Доп. упражнения: Многоразрядный компаратор* Схема для умножения (4-разрядных) чисел*. Схема для индикации чисел*. Решение: Задание№1. Арифметико-логическое устройство — это комбинационная схема, (т.е. она не содержит внутри элементов памяти), выполняющая следующие функции: принимающая на два входа два операнда (например, содержимое двух регистров); формирующая на выходе результат операции. В левом нижнем углу схемы находится двухразрядный декодер, который генерирует сигналы включения для четырёх операций. Выбор операции определяется сигналами управления F0 и F1. В зависимости от значений F0 и F1 выбирается одна из четырёх линий разрешения, и тогда выходной сигнал выбранной функции проходит через последний вентиль ИЛИ. Декодер – схема, которая получает на входе n-разрядное число и использует его для того чтобы выбрать (то есть установить в значение 1) одну из 2n выходных линий. В верхнем левом углу схемы находится логическое устройство для вычисления функций А И В, А ИЛИ В, НЕ В, но только один из этих результатов проходит через последний вентиль ИЛИ в зависимости от того, какую из линий разрешения выбрал декодер. Так как ровно один из выходных сигналов декодера может быть равен 1, то и запускаться будет ровно один из четырёх вентилей И. Остальные три вентиля будут выдавать 0 независимо от значений А и В. АЛУ имеет следующие входы для вычисления: входы для сигналов аргументов А И В и вход carry in – при вычислении суммы. Кроме этого подаётся INVA, так же имеются ENA и ENB. АЛУ может выполнять не только логические и арифметические операции над переменными А и В, но и делать их равными нулю, отрицая ENA (сигнал разрешения А) или ENB (сигнал разрешения В). Можно также получить НЕ А, установив сигнал INVA (инверсия А). Обычно сигналы ENA и ENB равны единице, чтобы разрешить поступление обоих входных сигналов, а сигнал INVA равен 0. В этом случае А и В просто поступают в логическое устройство без изменений. В нижнем правом углу находится полный сумматор для подсчёта суммы А и В. Он также имеет вход переноса с предыдущего разряда. Полный сумматор состоит из двух полусумматоров.  Задание№2. Для создания 4-х разрядного АЛУ возьмём 4 одноразрядных устройства и объединим в одну схему. На входы каждого из них будут подаваться соответствующие разряды чисел A и B от нулевого до третьего. На вход IN АЛУ будет подаваться константа ноль. На IN последующих подаётся сигнал из Carry Out предыдущих. Сигналы ENA, ENB, F0 и F1 будут подаваться по управляющим линиям. Сигнал INVA представит собой инвертированный вентилем НЕ сигнал A. На выходе мы получим 5-ти разрядное число - 4 выхода результатов АЛУ и выход Carry Out последнего из них.  Задание№3. Полученное 4 –х-разрядное АЛУ соединим со схемой сдвига. Схема с тремя режимами: без сдвига, сдвиг вправо, сдвиг влево. Для вызова определённого режима используются входные данные Сдвиг: 00 – без сдвига, 01 – сдвиг влево, 10 – сдвиг вправо. Выходные данные, которые представляют собой входные данные, сдвинутые на 1 бит, поступают на линии управления. Чтобы понять, как работает такая схема, рассмотрим пары вентилей И (кроме крайних вентилей). Если Сдвиг =10, правый член каждой пары включается, пропуская через себя соответствующий бит. Так как правый вентиль И соединен с входом вентиля ИЛИ, который расположен справа от этого вентиля И, происходит сдвиг вправо. Если Сдвиг =01, включается левый вентиль И из пары, и тогда происходит сдвиг влево. Для того чтобы добавить режим без сдвига вспомним что,  , когда A и B равны нулю. Добавим эту операцию в нашу схему. Полученные значения со схемы сдвига влево(вправо) и схемы без сдвига применим операцию ИЛИ, тем самым будет выводится нужное значение. , когда A и B равны нулю. Добавим эту операцию в нашу схему. Полученные значения со схемы сдвига влево(вправо) и схемы без сдвига применим операцию ИЛИ, тем самым будет выводится нужное значение. |