модель эвм. ЭВМ.лаба4. Лабораторная работа 4 Модель учебной эвм студент группы (Ф. И. О. студента) Проверил преподаватель

Скачать 4.22 Mb. Скачать 4.22 Mb.

|

|

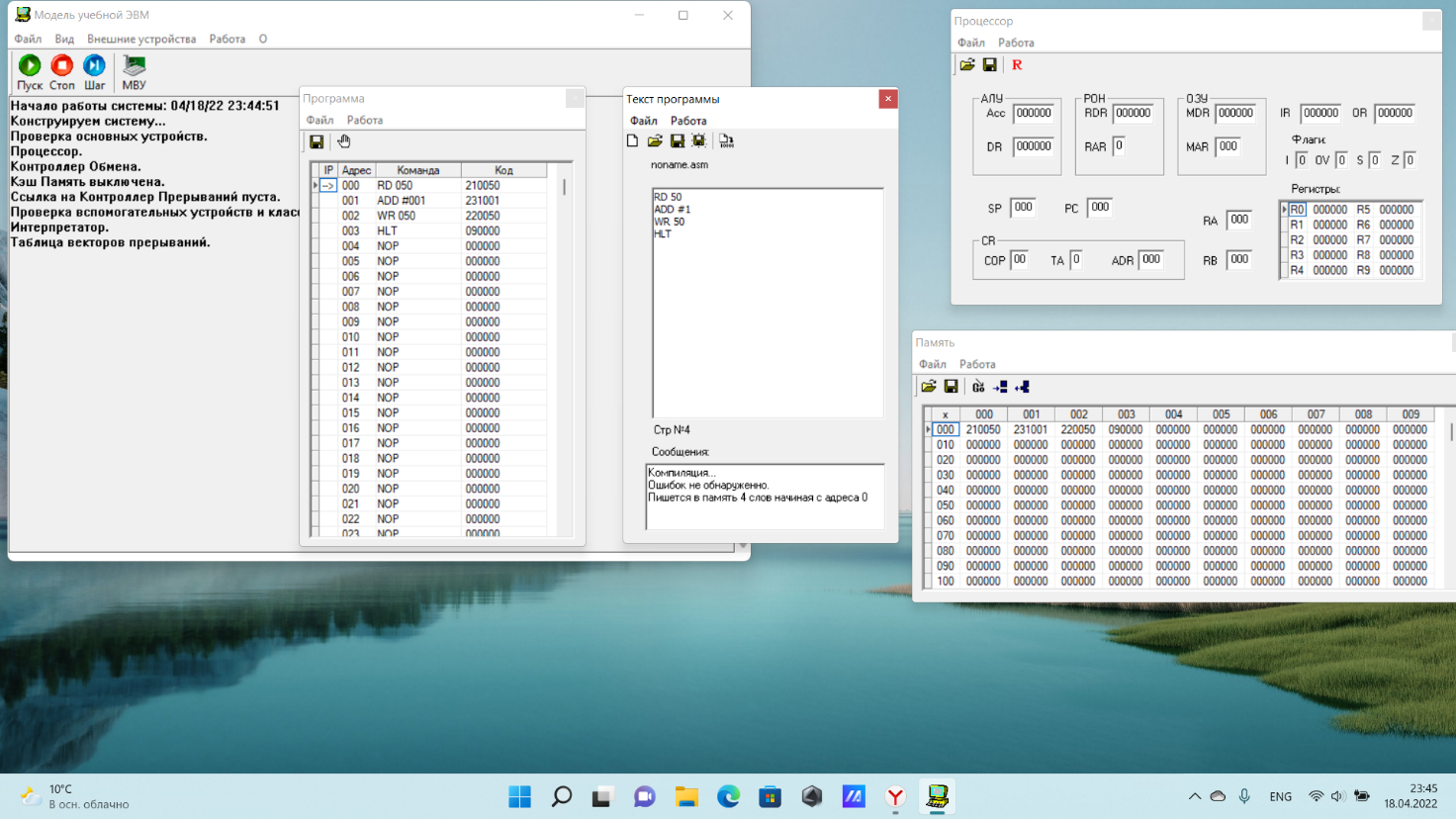

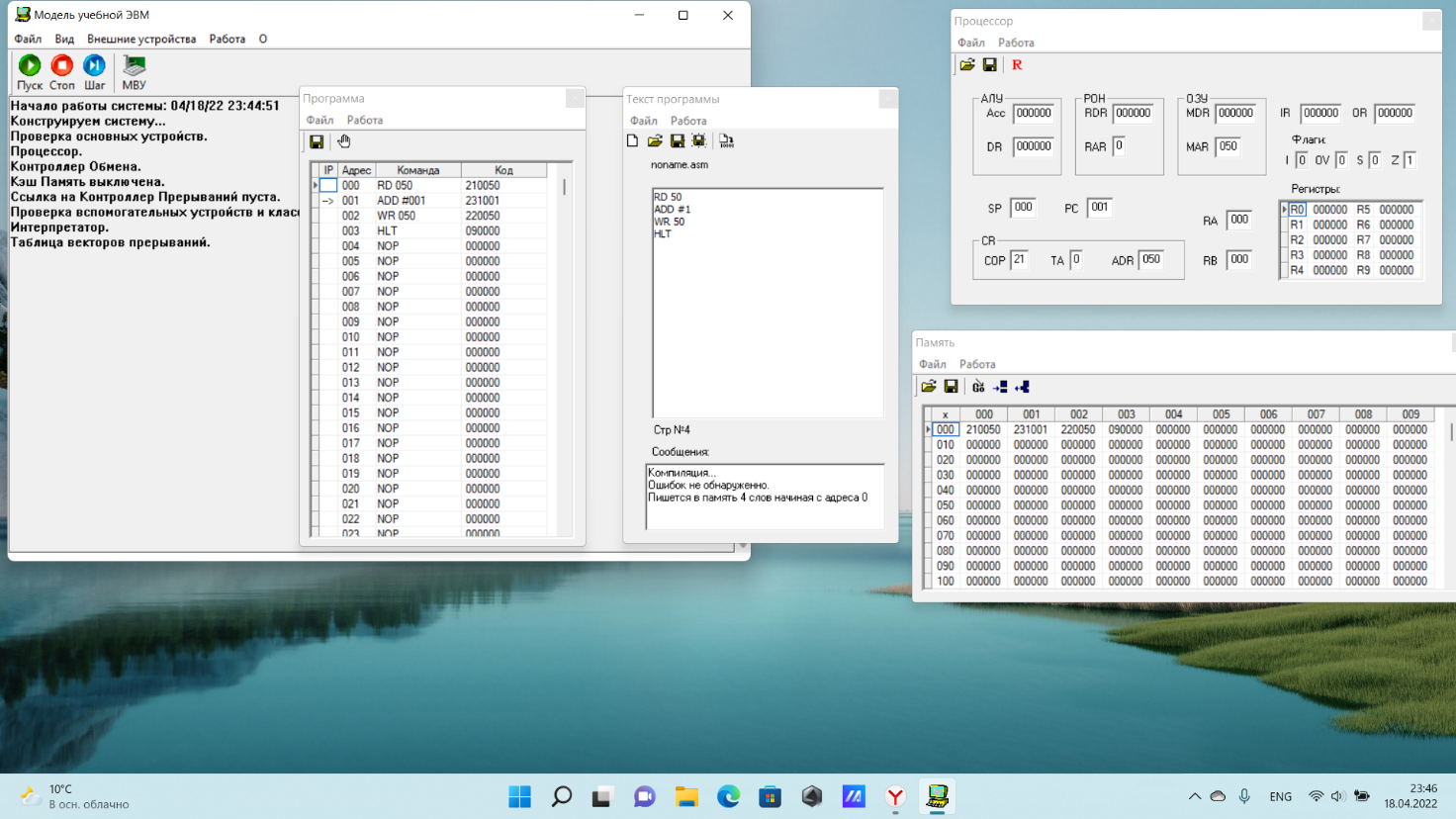

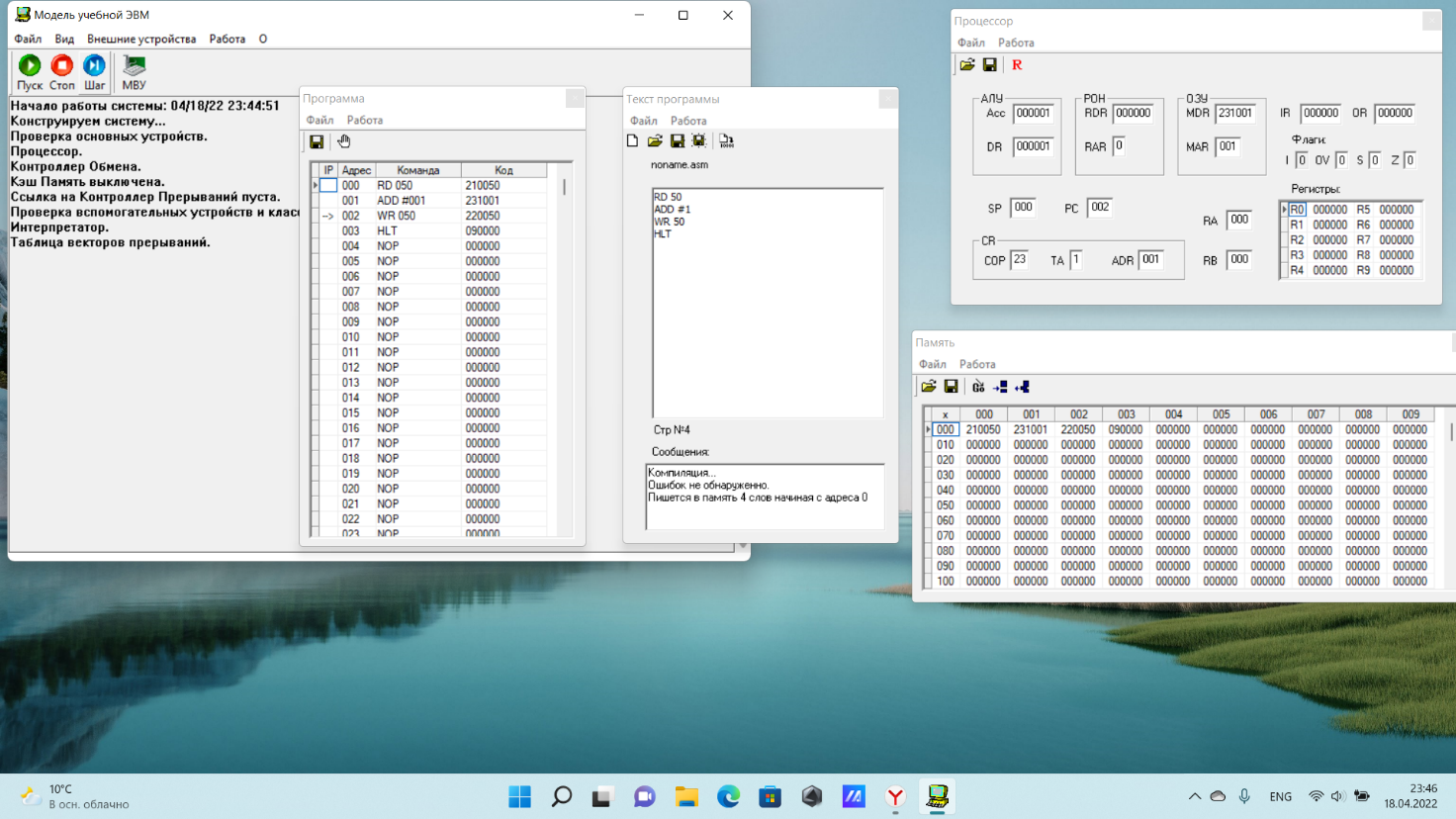

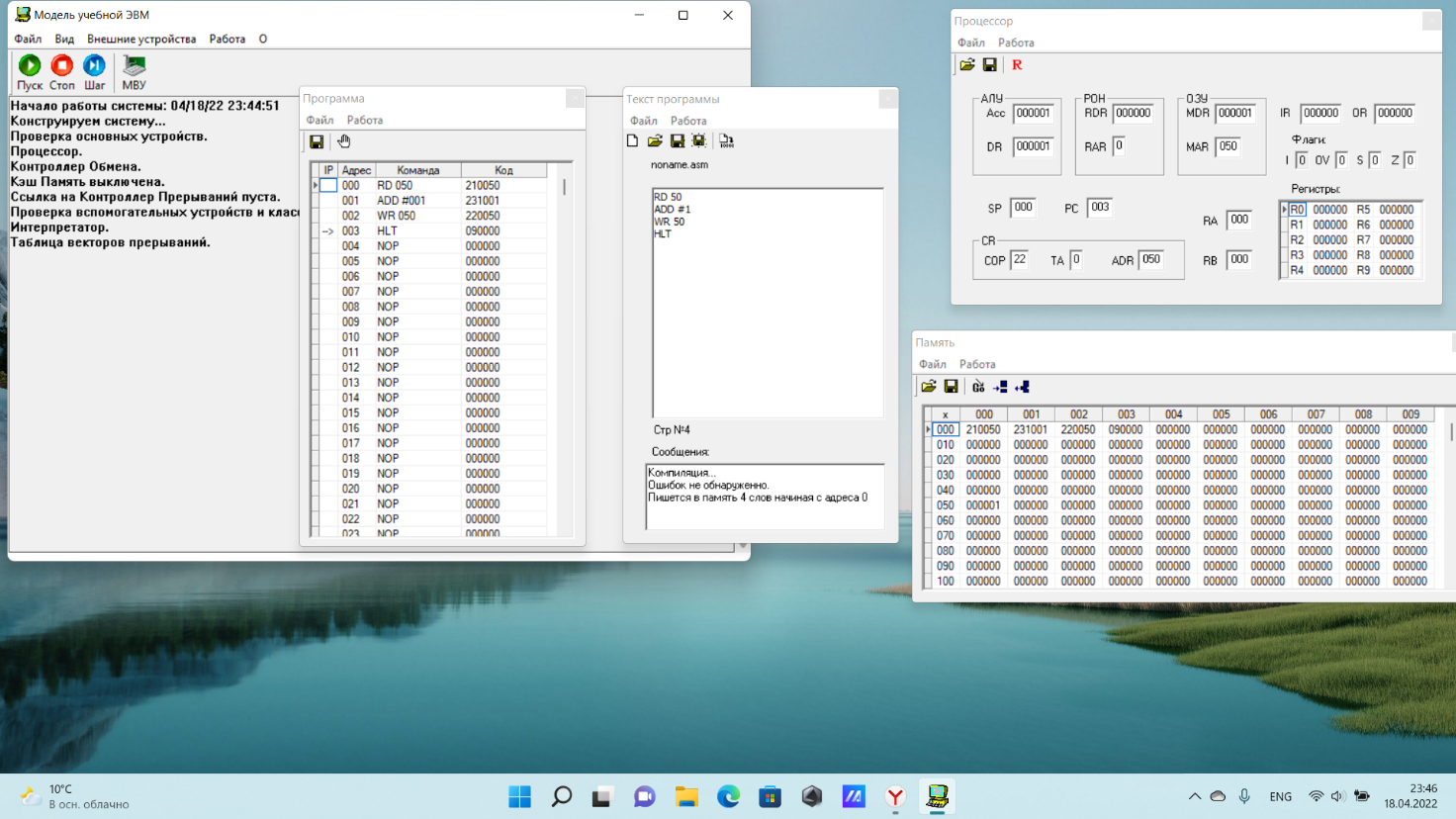

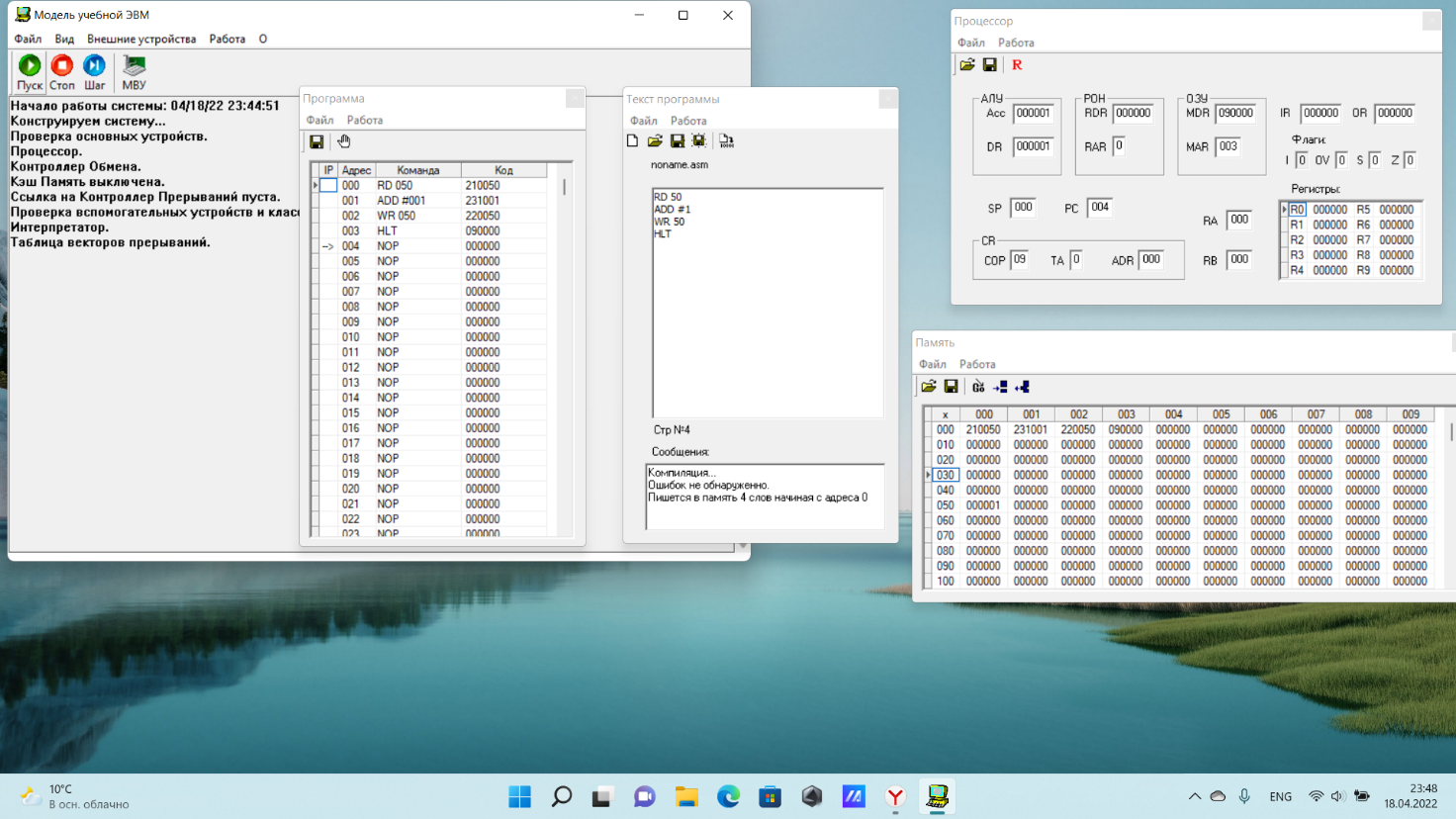

Министерство науки и высшего образования Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования «Уфимский государственный нефтяной технический университет» Кафедра «Вычислительная техника и инженерная кибернетика» ЭВМ и периферийные устройства Лабораторная работа №4 Модель учебной ЭВМ Выполнил: студент группы (Ф.И.О. студента) Проверил: преподаватель (Ф.И.О. преподавателя) Уфа, 2022 г. Конспект описания модели учебной ЭВМ; Современные процессоры и операционные системы — не слишком благоприятная среда для начального этапа изучения архитектуры ЭВМ. Одним из решений этой проблемы может быть создание программных моделей учебных ЭВМ, которые, с одной стороны, достаточно просты, чтобы обучаемый мог освоить базовые понятия архитектуры (система команд, командный цикл, способы адресации, уровни памяти, способы взаимодействия процессора с памятью и внешними устройствами), с другой стороны — архитектурные особенности модели должны соответствовать тенденциям развития современных ЭВМ. Программная модель позволяет реализовать доступ к различным элементам ЭВМ, обеспечивая удобство и наглядность. С другой стороны, модель позволяет игнорировать те особенности работы реальной ЭВМ, которые на данном уровне рассмотрения не являются существенными. Далее приводится описание программной модели учебной ЭВМ, предназначенной для начальных этапов изучения архитектуры (в т. ч. на младших курсах вуза и даже в школе). Именно этим объясняется использование в модели десятичной системы счисления для кодирования команд и представления данных. Структура ЭВМ Моделируемая ЭВМ включает процессор, оперативную (ОЗУ) и сверхоперативную память, устройство ввода (УВв) и устройство вывода (УВыв). Процессор, в свою очередь, состоит из центрального устройства управления (УУ), арифметического устройства (АУ) и системных регистров (CR, PC, SPи др.). Структурная схема ЭВМ показана на рис. 8.1. В ячейках ОЗУ хранятся команды и данные. Емкость ОЗУ составляет 1000 ячеек. По сигналу MWr выполняется запись содержимого регистра данных (MDR) в ячейку памяти с адресом, указанным в регистре адреса (MAR). По сигналу MRd происходит считывание — содержимое ячейки памяти с адресом, содержащимся в MAR, передается в MDR. Сверхоперативная память с прямой адресацией содержит десять регистров общего назначения R0—R9. Доступ к ним осуществляется (аналогично доступу к ОЗУ) через регистры RAR и RDR. АУ осуществляет выполнение одной из арифметических операций, определяемой кодом операции (СОР), над содержимым аккумулятора (Асс) и регистра операнда (DR). Результат операции всегда помещается в Асс. При завершении выполнения операции АУ вырабатывает сигналы признаков результата: Z (равен 1, если результат равен нулю); S (равен 1, если результат отрицателен); OV (равен 1, если при выполнении операции произошло переполнение разрядной сетки). В случаях, когда эти условия не выполняются, соответствующие сигналы имеют нулевое значение. В модели ЭВМ предусмотрены внешние устройства двух типов. Во-первых, это регистры IR и OR, которые могут обмениваться с аккумулятором с помощью безадресных команд in(Асе := IR) и out(OR := Асс). Во-вторых, это набор моделей внешних устройств, которые могут подключаться к системе и взаимодействовать с ней в соответствии с заложенными в моделях алгоритмами. Каждое внешнее устройство имеет ряд программно-доступных регистров, может иметь собственный обозреватель (окно видимых элементов). Подробнее эти внешние устройства описаны в разд. 8.6. УУ осуществляет выборку команд из ОЗУ в последовательности, определяемой естественным порядком выполнения команд (т. е. в порядке возрастания адресов команд в ОЗУ) или командами передачи управления; выборку из ОЗУ операндов, задаваемых адресами команды; инициирование выполнения операции, предписанной командой; останов или переход к выполнению следующей команды. В качестве сверхоперативной памяти в модель включены регистры общего назначения (РОН), и может подключаться модель кэш-памяти. В состав УУ ЭВМ входят: PC — счетчик адреса команды, содержащий адрес текущей команды; CR — регистр команды, содержащий код команды; RB — регистр базового адреса, содержащий базовый адрес; SP — указатель стека, содержащий адрес верхушки стека; RA— регистр адреса, содержащий исполнительный адрес при косвенной адресации. Регистры Асс, DR, IR, OR, CR и все ячейки ОЗУ и РОН имеют длину 6 десятичных разрядов, регистры PC, SP, RA и RB — 3 разряда. Программно-доступные регистры и флаги: • Асc — аккумулятор; • PC — счетчик адреса команды, содержащий адрес текущей команды; • SP — указатель стека, содержащий адрес верхушки стека; • RB — регистр базового адреса, содержащий базовый адрес; • RA — регистр адреса, содержащий исполнительный адрес при косвенной адресации; • IR — входной регистр; • OR — выходной регистр; • I — флаг разрешения прерываний. Системные регистры и флаги: • DR — регистр данных АЛУ, содержащий второй операнд; • MDR — регистр данных ОЗУ; • MAR — регистр адреса ОЗУ; • RDR — регистр данных блока РОН; • RAR — регистр адреса блока РОН; • CR — регистр команд, содержащий поля: COP — код операции; TА — тип адресации; ADR — адрес или непосредственный операнд; • Z — флаг нулевого значения Асc; • S — флаг отрицательного значения Асc; • OV — флаг переполнения. Регистры Асc, DR, IR, OR, CR и все ячейки ОЗУ и РОН имеют длину 6 десятичных разрядов, регистры PC, SP, RA и RB — 3 разряда. В окне Процессор отражаются текущие значения регистров и флагов, причем в состоянии Останов все регистры, включая регистры блока РОН, и флаги (кроме флага I) доступны для непосредственного редактирования. Результат выполнения работы Результат команды RD 50  Результат команды ADD #1  Результат команды WR 50 Результат команды WR 50 Результат команды HLT  Общий результат работы после Пуска  Вывод: Ознакомились с Учебной моделью ЭВМ и изучили ее интерфейс, научились работать в этой программе. Изучили общее описание модели и ее документацию. Запустили программу в разных режимах, увидели результат ее выполнения, отследить работу процессора в процессе выполнения программы. |