ЛР№5. Лабораторная работа 5 Построение и исследование схем дискретной логики, используемых при создании помехоустойчивых кодеков

Скачать 0.67 Mb. Скачать 0.67 Mb.

|

|

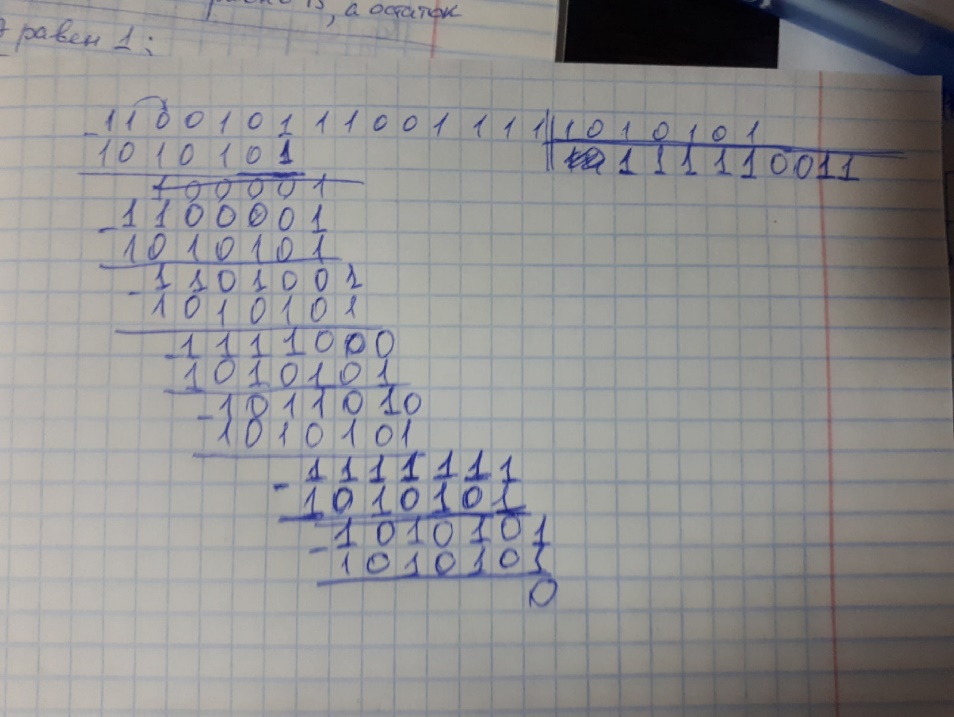

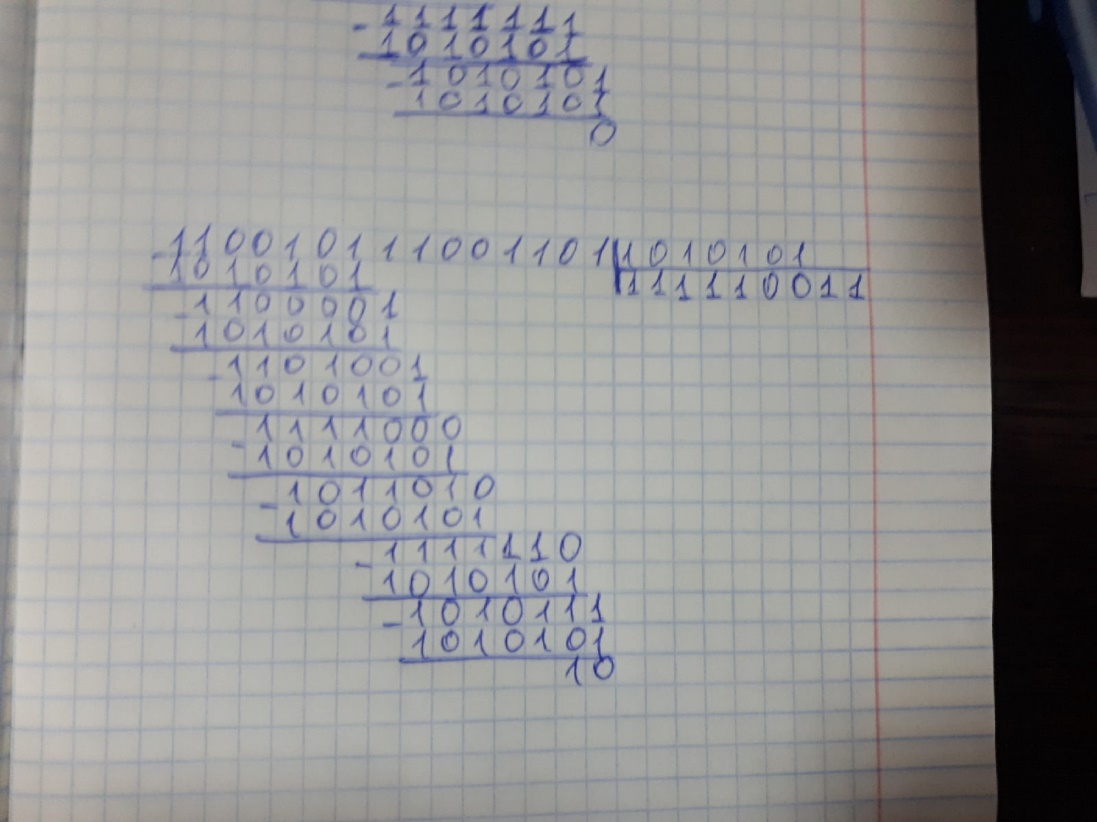

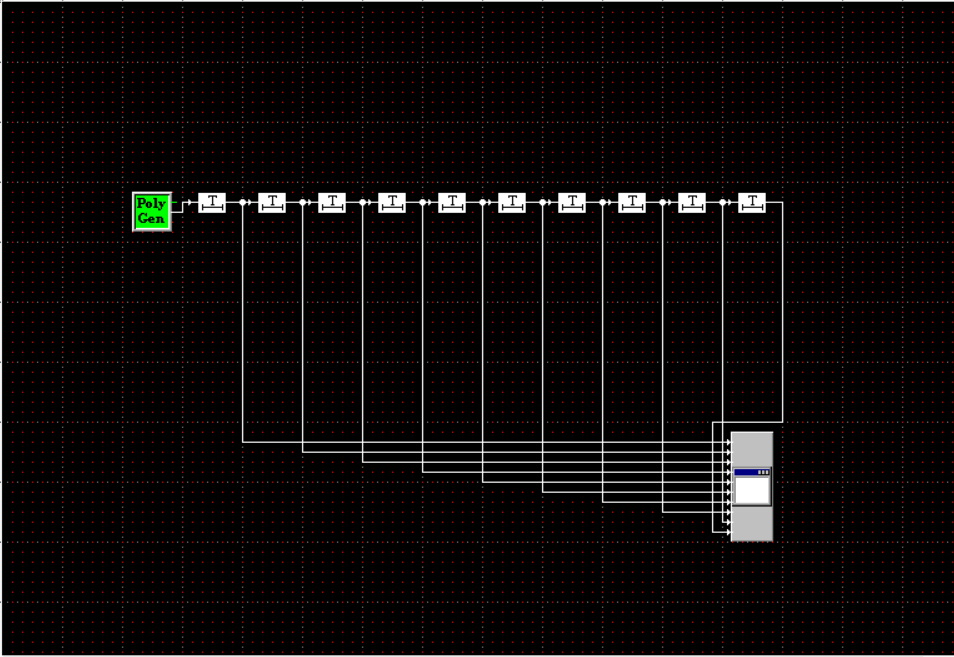

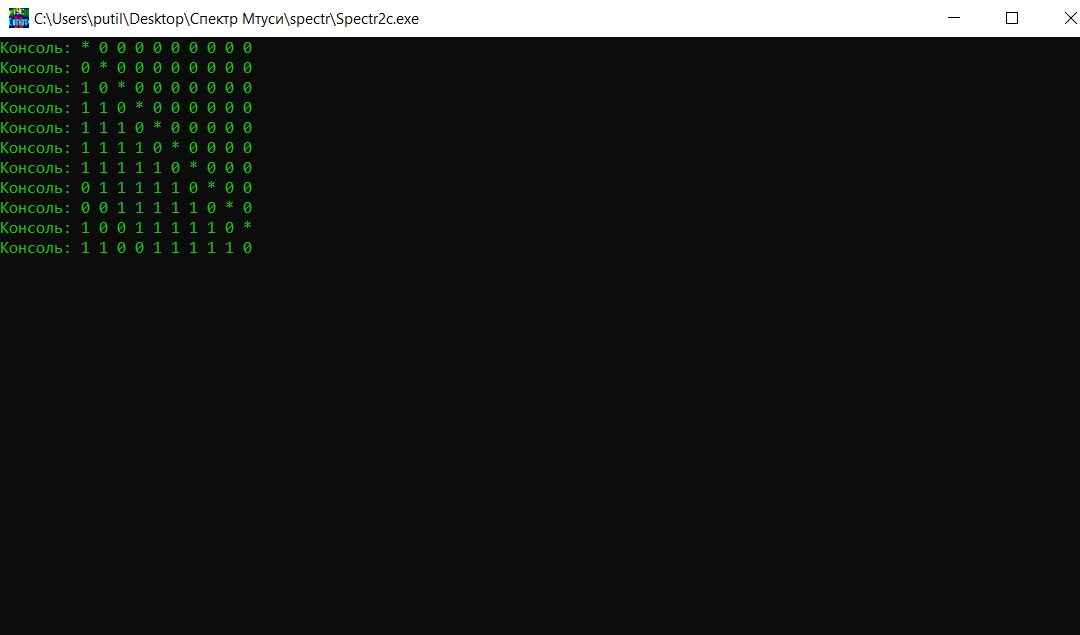

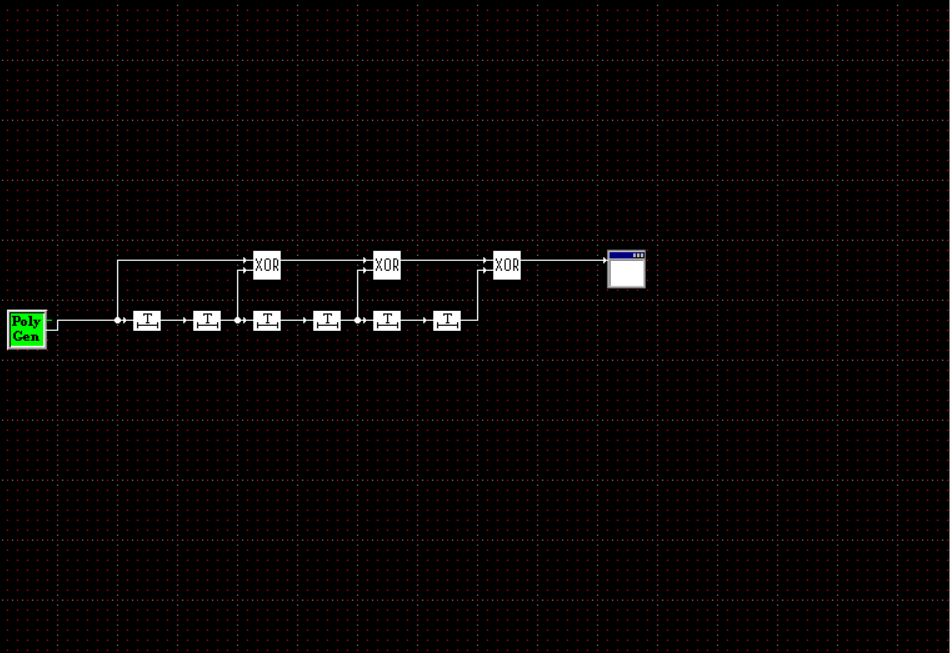

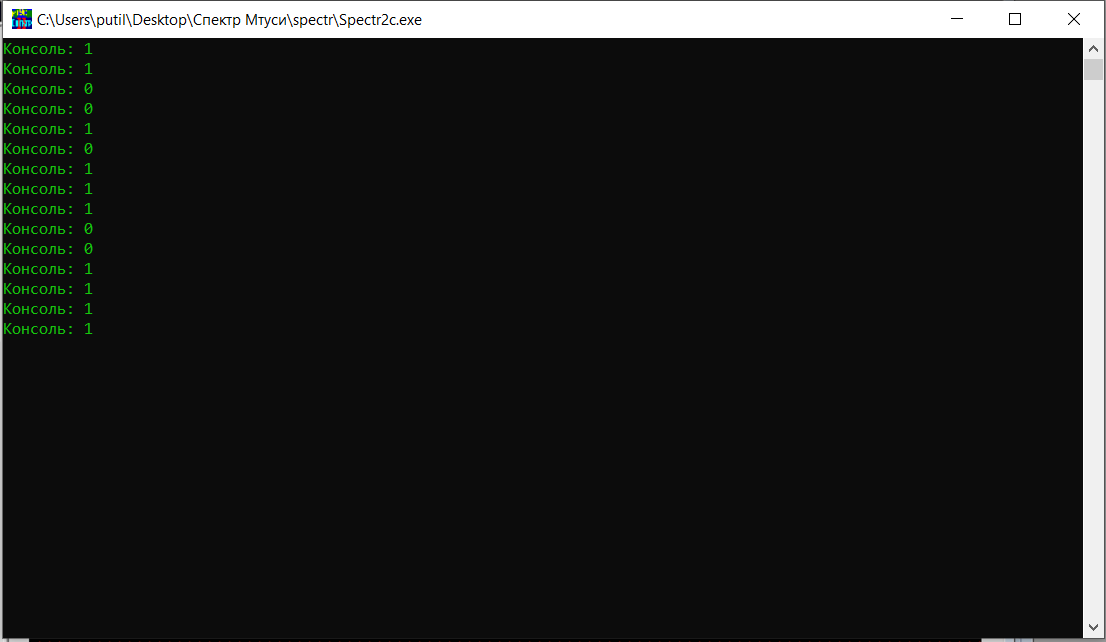

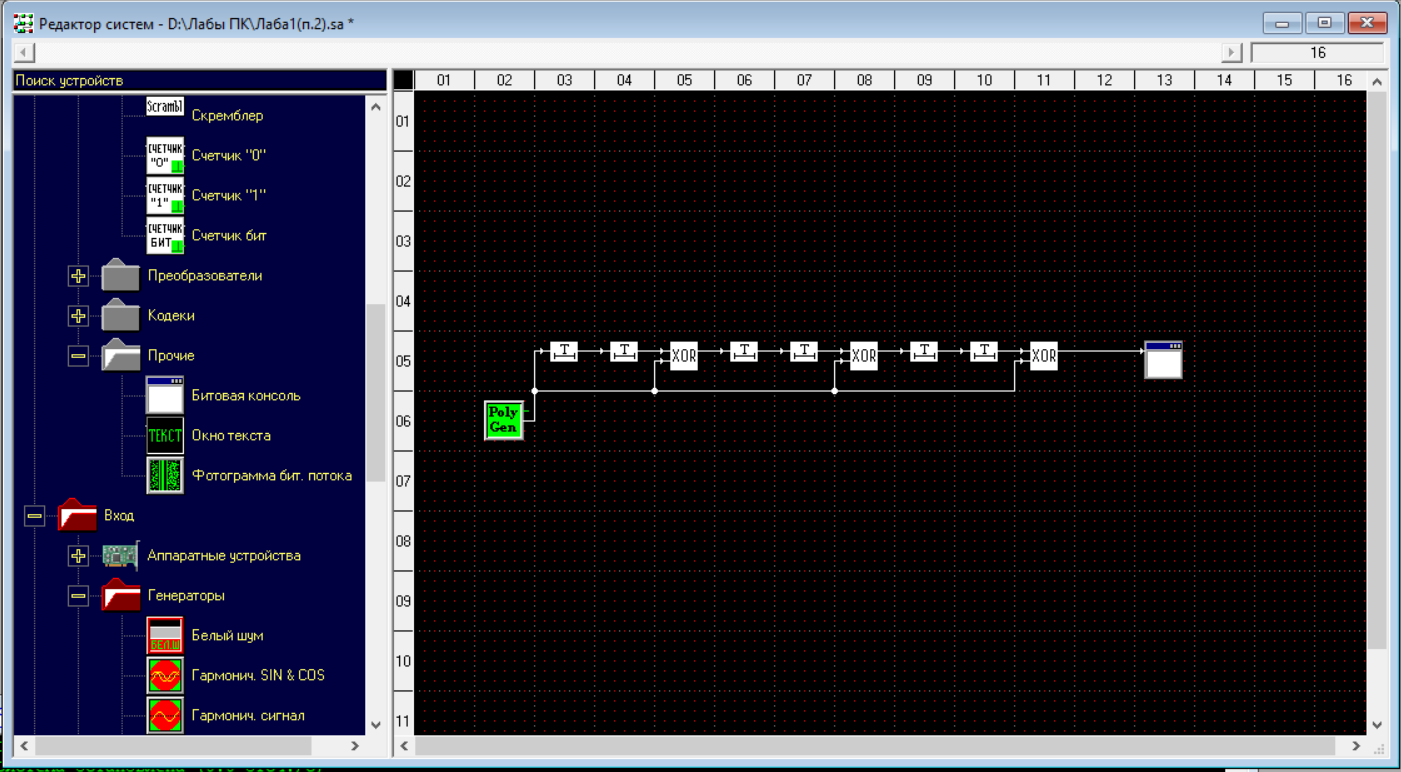

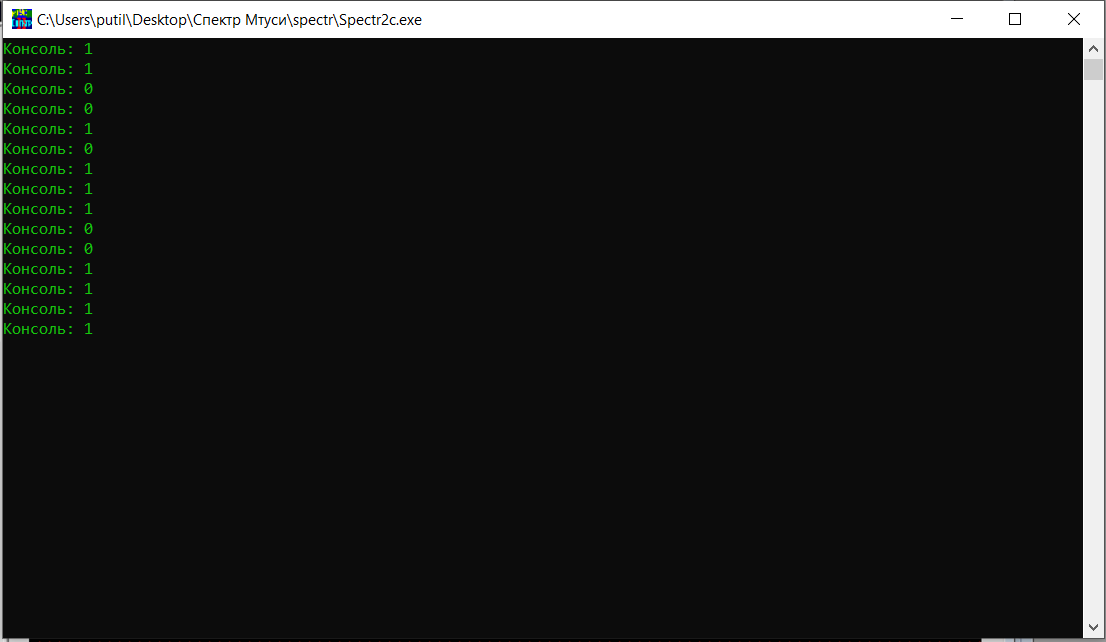

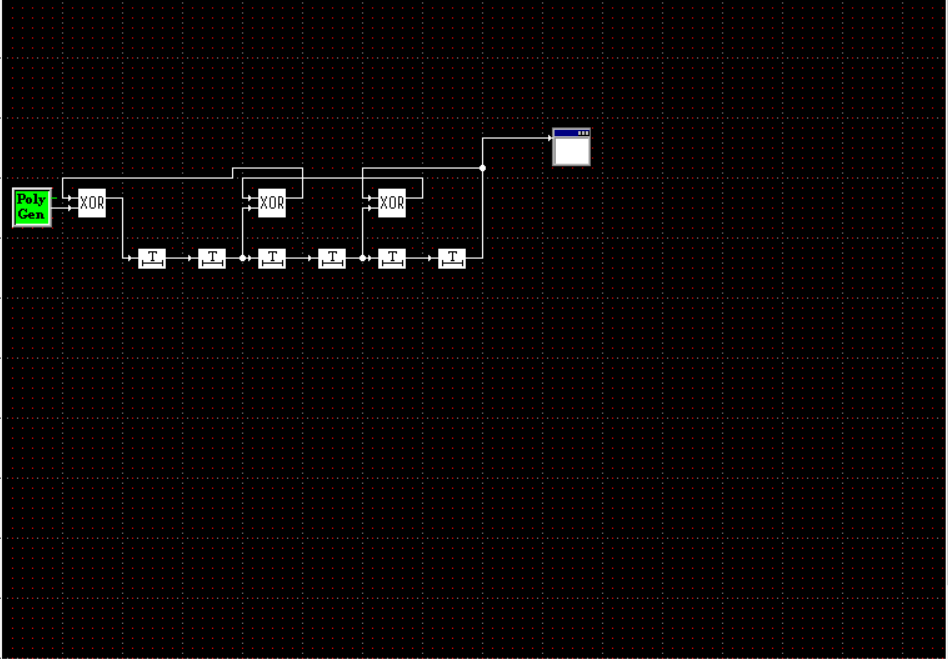

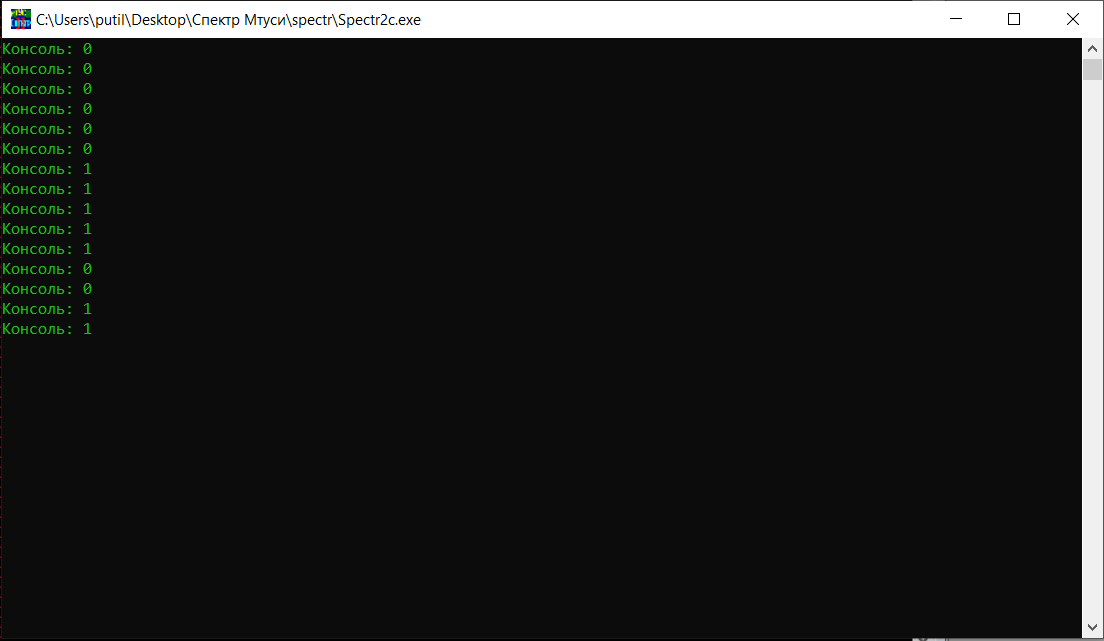

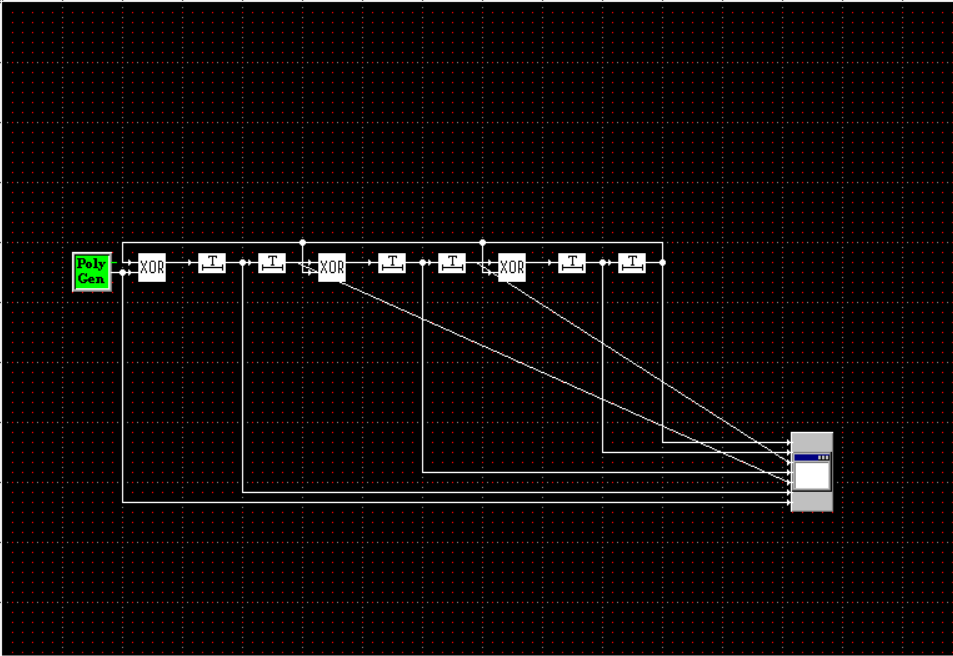

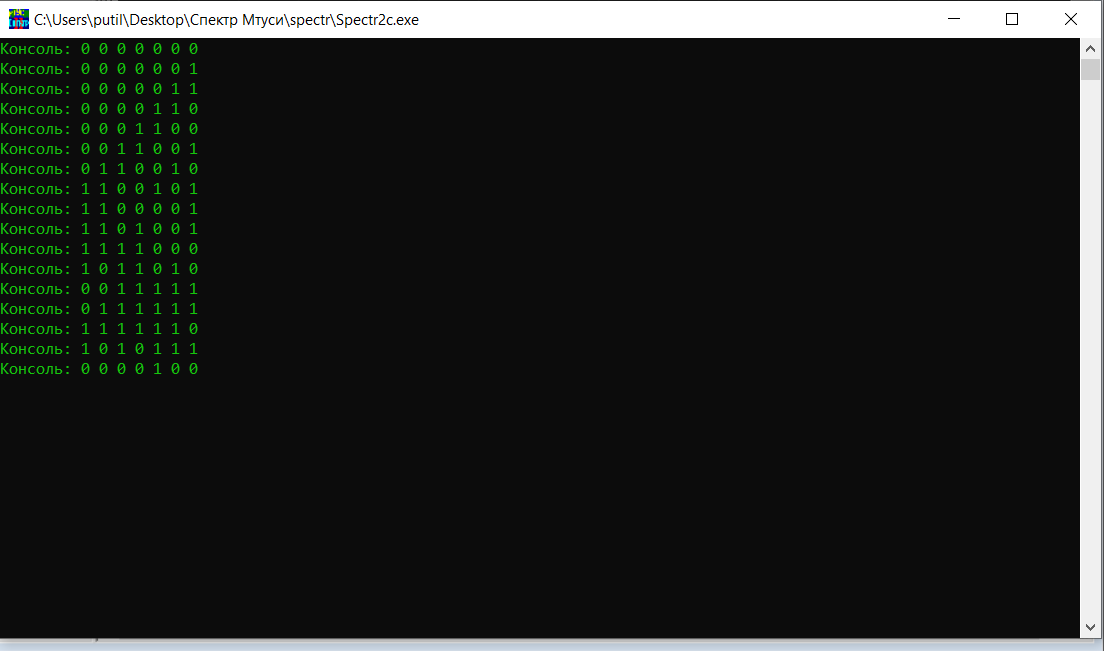

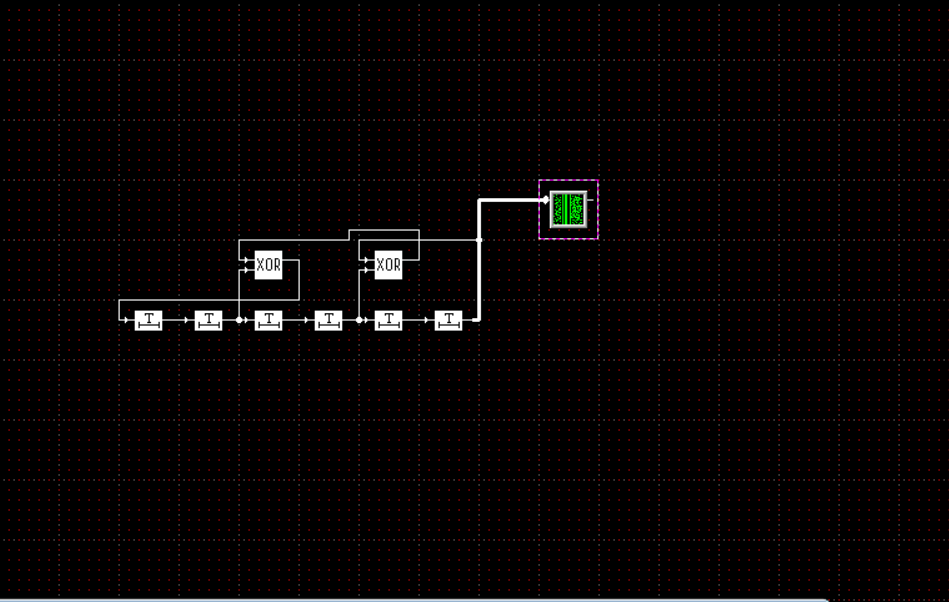

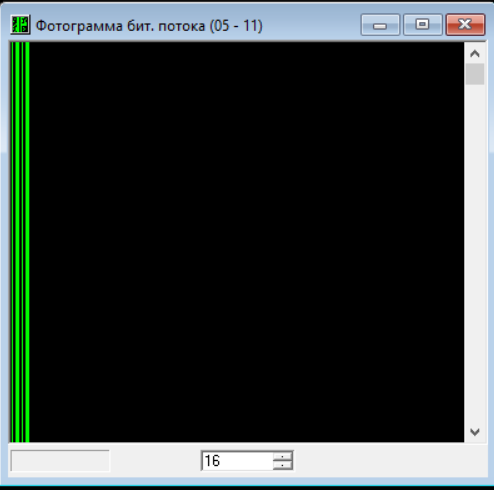

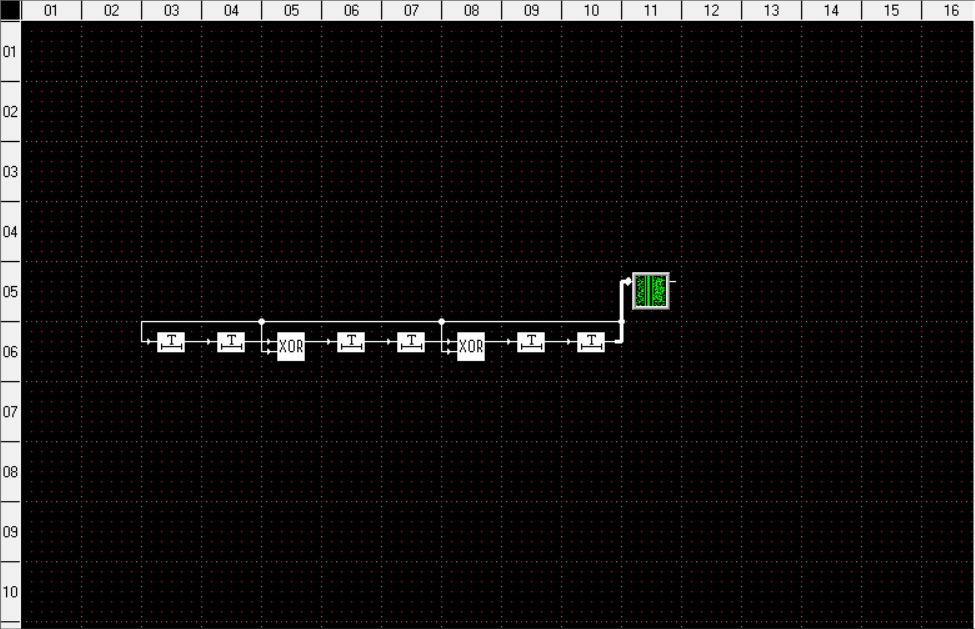

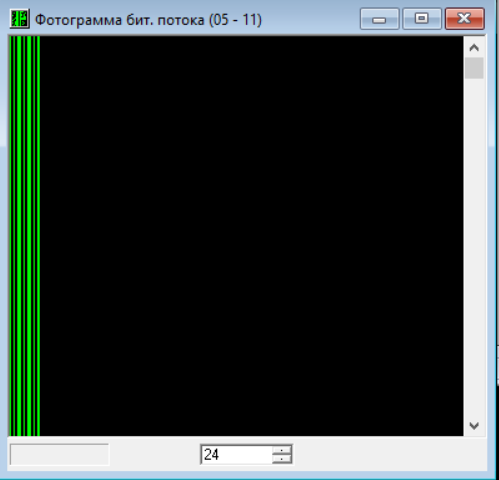

Московский Технический Университет Связи и Информатики Кафедра радиотехнических систем ПОМЕХОУСТОЙЧИВОЕ КОДИРОВАНИЕ Лабораторная работа №5 Построение и исследование схем дискретной логики, используемых при создании помехоустойчивых кодеков. Выполнил: Путилин Р.А. Гр БРР 1901 Преподаватель: Шубина М.В. Москва 2022 Цель работы: изучение принципа построения и работы схем дискретной логики, используемых при создании помехоустойчивых кодеков. Исходные данные по варианту №10 Закодируем две буквы моей фамилии Путилин согласно таблице №1 методических указаний а=0111110011 a(x)= x8+x7+x6+x5+x4+x+1 Образующий полином из таблицы №2 g(x)=1258=10101012=x6+x4+x2+1 Предварительный расчёт: Умножим исходный полином на образующий c(x)=a(x)*g(x)= (x8+x7+x6+x5+x4+x+1)*( x6+x4+x2+1)=x14+x13+x10+x8+x7+x6+x3+x2+x+1 111110011 x 1010101 -------------------------- 111110011 111110011 111110011 111110011 -------------------------- 110010111001111 Произведём деление с(x)/g(x)  Полученное частное равно (111110011)= a(x). Остаток равен нулю Произведём деление [с(x)+x]/g(x)  Полученное частное равно (111110011)= a(x). Остаток равен (10) Ход работы: Построение регистра сдвига битовых последовательностей.  Рис.1 Регистр сдвига битовых порследовательностей Генератор полинома выдаёт исходную битовую последовательность а затем нули 111110011 00000000000000000, которую можно наблюдать на выходах сдвиговых регистров с помощью битовой консоли. Данные битовой консоли приведены на рис.2  Рис.2 Данные битовой консоли для регистра сдвига Сохранённые бинарные данные представлены ниже, в них тоже видна периодически повторяющаяся входная последовательность за исключенеим того, что она выходит младшими битами вперёд. Построение схемы перемножения полиномов-битовых последовательностей. 2а) Перемножитель полиномов по схеме Фибоначчи примет вид, изображенный на рис.3. Отводы от регистров на элементы сложения по модулю 2 соответствуют умножению входной последовательности на полином g(x) =10101012=x6+x4+x2+1  Рис.3 Перемножитель полиномов-битовых последовательностей по схеме Фибоначчи. Выходная последовательность, представленная на рис.4, соответствует предварительно рассчитанному произведению c=a*g= 110010111001111  Рис.4 Данные битовой консоли при работе схемы Фибоначчи для умножения полиномов 2б) Схема Галуа для перемножения полиномов примет вид, изображенный на рис.  Рисунок схемы. Выходная последовательность, представленная на рис., соответствует предварительно рассчитанному произведению c=a*g=110010111001111 Рисунок данных консоли  Построение схем для деления полиномов. 3а) Схема Фибоначчи для деления полиномов.  Получим схему деления полиномов, вычисляющую частное (последовательность бит на выходе регистра) и остаток от деления c(x) на g(x) (состояние ячеек регистра делителя к моменту завершения операции деления), Как результат работы делителя на рис. представлены данные битовой консоли. (на консоль вывести выход источника, выходы ячеек регистра )  3б) Схема Галуа для деления полиномов. Изменим исходные данные, заменив с(x)на C`(x)=c(x)+x, что соответствует делению с остатком. Прибавление x – это инверсия предпоследнего разряда делимого. Найдём остаток от деления с(x)+x на g(x). Он должен быть ненулевым.  Рис.5 Схема деления полиномов, делитель – полином g(x) Получим схему деления полиномов, вычисляющую частное (последовательность бит на выходе регистра) и остаток от деления c(x)+x на g(x) Битовая консоль выдаёт остаток вида 10. Как результат работы делителя на рис. представлены данные битовой консоли. (на консоль вывести выход источника, выходы ячеек регистра )  Рисунок Отображение результатов работы делителя на битовой консоли. Первые 6 цифр консоли в последней строке показывают остаток деления: 10. Остаток появляется на выходах ячеек регистра на следующий такт после выхода последнего разряда частного ( оно в первом столбце 111110011) и поступления с генератора последнего разряда входного сигнала ( он в последнем столбце 110010111001101). 4а) Построение схемы генератора псевдослучайной последовательности по схеме Фибоначчи.  Рисунок Генератор псевдослучайной последовательности. Схема Фибоначчи.  Рисунок Фотограмма ПСП Период генерируемой ПСП равен 8. 4б) Построение схемы генератора псевдослучайной последовательности по схеме Галуа.  Рис.8 Схема генератора ПСП Определим период генерируемой последовательности, добившись того, чтобы фотограмма (рис.9) этой ПСП представляла собой вертикальные прямые линии.  Рис.9 Фотограмма ПСП Период генерируемой ПСП равен 8. Выводы: Изучен принцип работы умножителя многочленов на элементах дискретной логики по схемам Галуа и Фибоначчи. Результаты, полученные с помощью лабораторного стенда совпали с данными предварительного расчёта. Изучен принцип работы делителя многочленов на элементах дискретной логики по схемам Галуа и Фибоначчи. Результаты, полученные с помощью лабораторного стенда совпали с данными предварительного расчёта На базе схем деления полиномов построены схемы генераторов псевдослучайных последовательностей. |