мпс. Лабораторная работа №2 Пластинин И. С.. Лабораторная работа 7 изучение функционирования микропроцессоров с фиксированной системой команд на примере микропроцессора kp580

Скачать 48.28 Kb. Скачать 48.28 Kb.

|

|

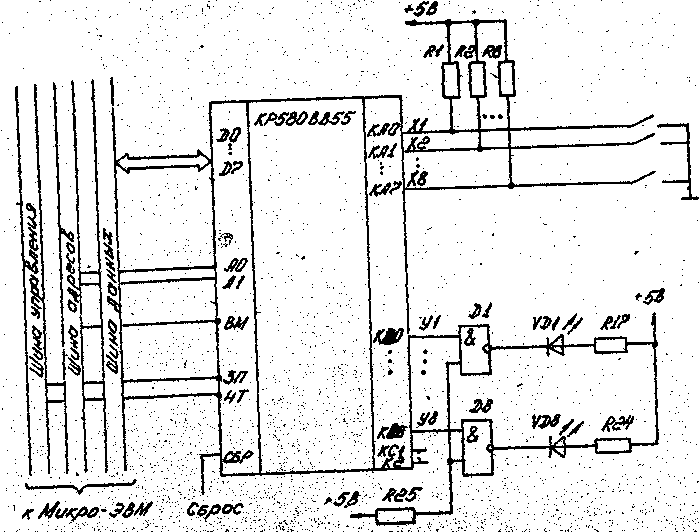

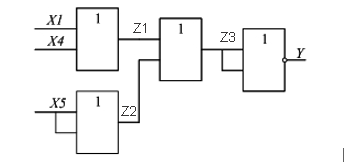

МИНОБРНАУКИ РОССИИ ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ «НИЖЕГОРОДСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ им. Р.Е. АЛЕКСЕЕВА» (НГТУ) Кафедра «Электрооборудование, электропривод и автоматика» Дисциплина «Микропроцессорные системы» Лабораторная работа №7 «ИЗУЧЕНИЕ ФУНКЦИОНИРОВАНИЯ МИКРОПРОЦЕССОРОВ С ФИКСИРОВАННОЙ СИСТЕМОЙ КОМАНД НА ПРИМЕРЕ МИКРОПРОЦЕССОРА KP580» Выполнил: студент группы 18-ЭПА Пластинин И. С. Проверила: Слядзевская К.П. Нижний Новгород 2021 г. Теоретическая часть В качестве указанных портов используются порты А и В программируемой периферийной БИС КР580ВВ55 - программируемый периферийный адаптер (ППА), расположенный в приставке к плате микро-ЭВМ, ППА содержит три программируемых 8-разрядных каналов ввода-вывода КА, KB и КС, соответствующие трем портам А, В и С (рис.1), а также порт регистра управляющего слова (РУС), куда для задания режимов работы каналов по команде вывода предварительно заносится управляющее слово. Возможны три режима (О, 1 и 2) работы каналов ППА. Ниже используется только режим 0. В этой режиме ППА имеет следующую конфигурацию: 8-разрядная шина (порты А и В) и две 4-разрядные шины (порт С). Каждая из них может работать как в режиме ввода, так и в режиме вывода, что определяется управляющим словом, программирующим режим. Для настройки каналов А и В на ввод, а С на вывод в режиме 0 необходимо в порт РУС заслать константу 92 Н. Порты А, В, С и РУС имеют соответственно номера 80 H, 81 Н, 82 Н и 83 Н. Входные переменные X1, X2 ...X8 подаются на линии КА0, KAI.. ..КА7 канал А с помощью переключателей K1, K2, ..., К8 соответственно. Значения выходных переменных Y1, Y2 ...Y8 выводятся соответственно на линии КB0, ..., КB7. 6 конкретном значении переменной Yi можно судить по состоянию светодиода Vi (если Yi равно 1, то Vi горит, в противном случае Vi погашен) (см. рис.1).  Рис. 1 Практическая часть Логическая функция  Таблица истинности

Программа реализации логической функции.

Вывод В ходе выполнения данной лабораторной работы изучено функционирование вычислительной системы на базе микропроцессорного комплекта KP580, взаимодействие отдельных компонентов системы, систем команд и способов программирования. Правильность таблицы истинности была проверена на лабораторной установке. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||