Лекции по схемотехнике ЭВМ. Лекция Базовые понятия цифровой электроники версия для печати и pda в лекции рассказывается о базовых терминах цифровой электроники, о цифровых сигналах, об уровнях представления цифровых устройств, об их электрических и временных параметрах

Скачать 5.63 Mb. Скачать 5.63 Mb.

|

|

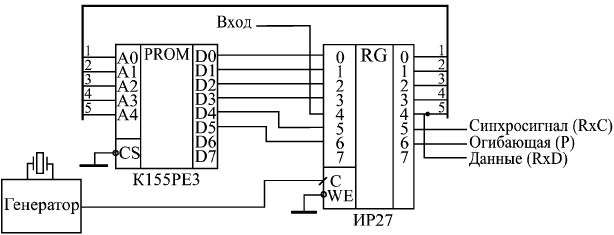

Рис. 11.20. Декодирование кода Манчестер-II Таким образом, алгоритм декодирования довольно сложен. Его можно, конечно, выполнить с помощью одновибраторов и триггеров. Но можно воспользоваться и микропрограммным автоматом, который, в отличие от одновибратора, не требует настройки, не чувствителен к помехам и тактируется сигналом кварцевого генератора. Схема такого микропрограммного автомата (рис. 11.21) очень проста, она включает в себя ПЗУ типа РЕ3, регистр ИР27 и тактовый генератор с частотой, в 8 раз превышающей частоту прихода битов в коде Манчестер-II. Например, при длительности битового интервала 1 мкс (скорость передачи информации 1 Мбит/с) частота генератора должна быть равной 8 МГц. Схема практически не отличается от схемы, рассмотренной в предыдущем примере, хотя выполняемая ею функция гораздо сложнее. Помимо синхросигнала (его обычно обозначают RxC или С), микропрограммный автомат выдает также сигнал огибающей информационного пакета (Р), то есть сигнал, активный при наличии передачи информации в коде Манчестер-II и пассивный при отсутствии передачи информации (см. рис. 11.20). Сигнал С (RxC) стробирует запись сигнала данных RxD, представляющего собой просто входной сигнал в коде Манчестер-II, пропущенный через регистр.  Рис. 11.21. Микропрограммный автомат для декодирования кода Манчестер-II Мы не будем подробно рассматривать составление микропрограммы для декодирования кода Манчестер-II, так как это заняло бы слишком много места. Достаточно только внимательно изучить табл. 11.10, содержащую микропрограмму с комментариями, чтобы понять, что в ней присутствуют и отключение реакции на входной сигнал, и выдержка временных интервалов (задержка), и переходы в заданные адреса, и остановки для ожидания положительного и отрицательного фронтов входного сигнала.

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 12. Лекция: Оперативная память: версия для печати и PDA В лекции рассказывается о микросхемах оперативной памяти, алгоритмах их работы, параметрах, типовых схемах включения, а также о способах реализации на их основе некоторых часто встречающихся функций. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

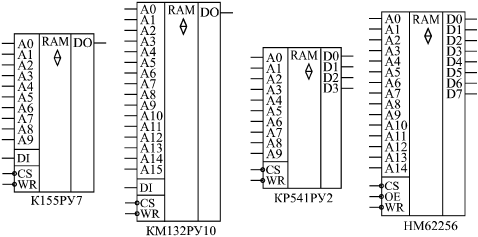

| Основное отличие оперативной памяти (RAM) от постоянной (ROM) состоит в возможности оперативного изменения содержимого всех ячеек памяти с помощью дополнительного управляющего сигнала записи WR. Каждая ячейка оперативной (статической) памяти представляет собой, по сути, регистр из триггерных ячеек, в который может быть записана информация и из которого можно информацию читать. Выбор того или иного регистра (той или иной ячейки памяти) производится с помощью кода адреса памяти. Поэтому при выключении питания вся информация из оперативной памяти пропадает (стирается), а при включении питания информация в оперативной памяти может быть произвольной. Отметим, что существует также еще одна разновидность оперативной памяти, так называемая динамическая (в отличие от статической), в которой информация хранится не в регистрах (не в триггерных ячейках), а в виде заряда на конденсаторах. Эта память отличается более низкой стоимостью, меньшим быстродействием и необходимостью регулярной регенерации ("Refresh" - "освежение") информации в ней (так как конденсаторы со временем разряжаются). Область применения динамической памяти гораздо уже, чем статической, в основном она используется в качестве системной оперативной памяти компьютеров, где соображения стоимости выходят на первый план. Поэтому здесь мы о ней говорить не будем, хотя многие особенности использования статической памяти относятся и к динамической памяти. Во всех рассмотренных в предыдущем разделе схемах постоянная память в принципе может быть заменена оперативной, только карту прошивки в данном случае придется записывать в память каждый раз заново после включения питания. Аналогично, многое из сказанного в данном разделе про оперативную память справедливо и для постоянной памяти, но только информацию в постоянной памяти менять невозможно. Однако существуют также и специфические области применения оперативной памяти, которым и будет уделено здесь особое внимание.  Рис. 12.1. Примеры микросхем статических ОЗУ Как уже отмечалось, оперативная память бывает двух основных видов: с раздельными шинами входных и выходных данных (в основном это одноразрядная память) и с двунаправленной (совмещенной) шиной входных и выходных данных (многоразрядная память). Некоторые простейшие примеры микросхем памяти обоих этих видов приведены на рис. 12.1. Выходы данных микросхем памяти имеют тип ОК (довольно редко) или 3С. Управляющие сигналы - это сигнал выбора микросхемы CS (иногда их несколько), сигнал записи WR (обычно отрицательный) и иногда сигнал разрешения выхода OE. Микросхема оперативной памяти К155РУ7 (аналог - F9342APC) имеет организацию 1Кх1 и раздельные входной и выходной сигналы данных. Выход микросхемы - типа 3С. Управление работой микросхемы производится двумя управляющими сигналами CS и WR. Режимы работы микросхемы приведены в табл. 12.1.

Микросхема КМ132РУ10 отличается от К155РУ7 в основном большим объемом (организация 64К х 1) и несколько меньшим быстродействием. Назначение управляющих сигналов и таблица режимов работы у этих микросхем совпадают.

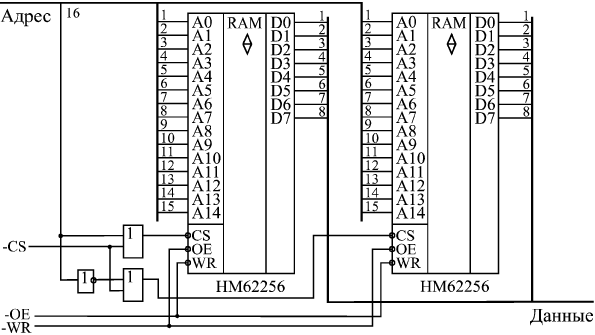

Микросхема КР541РУ2 (аналог - IM7147L-3) относится к другой разновидности микросхем памяти. У нее четыре двунаправленных вывода данных типа 3С. Управляющие сигналы те же самые: –CS и –WR. Таблица режимов работы (табл. 12.2) также похожа на таблицу для одноразрядных микросхем. Главное отличие состоит в том, что в режиме записи на входах/выходах данных присутствует записываемая информация. Микросхема HM62256 фирмы Hitachi отличается от КР541РУ2 прежде всего организацией (32К х 8) и управляющими сигналами (добавлен сигнал разрешения выхода –OE). Когда этот сигнал пассивен (равен единице), входы/выходы данных микросхемы находятся в состоянии 3С независимо от режима работы. Введение дополнительного сигнала позволяет более гибко управлять работой микросхемы. К тому же обычно в подобных микросхемах при пассивном сигнале –CS (равном единице) значительно уменьшается потребляемая мощность. В настоящее время имеется огромный выбор микросхем памяти с разным объемом (от нескольких байт до нескольких мегабайт), с разным количеством разрядов (обычно 1, 4, 8, 16 разрядов), с разными методами управления, с разным потреблением и быстродействием. В каждом конкретном случае надо подбирать оптимальную память, в наибольшей степени удовлетворяющую требованиям решаемой задачи. Таблицы режимов работы (таблицы истинности) микросхем памяти не дают достаточно информации для их практического использования. Для микросхем памяти очень важны временные параметры (задержки сигналов относительно друг друга) и порядок выставления и снятия сигналов адреса, данных и управления. Всю эту информацию дают временные диаграммы циклов записи в память и чтения (считывания) из памяти, приводимые в справочниках. Самые главные временные параметры оперативной памяти следующие:

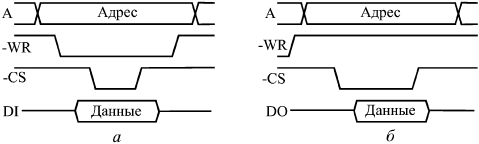

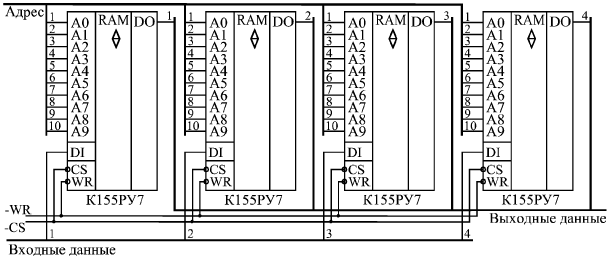

Всего же количество временных параметров может достигать двух-трех десятков, но мы не будем подробно останавливаться на этом, так как вся подобная информация имеется в многочисленных справочниках. Характерные величины всех временных параметров памяти составляет от единиц и даже долей наносекунд до десятков наносекунд. Типичные временные диаграммы циклов записи и чтения приведены на рис. 12.2. Конкретные временные диаграммы для каждого типа памяти необходимо смотреть в справочниках.  Рис. 12.2. Типичные временные диаграммы записи в память (а) и чтения из памяти (б) Для записи информации в память надо выставить код адреса на адресных входах, выставить код записываемых в этот адрес данных на входах данных, подать сигнал записи –WR и подать сигнал выбора микросхемы –CS. Порядок выставления сигналов бывает различным, он может быть существенным или несущественным (например, можно выставлять или снимать –CS раньше или позже выставления или снятия –WR). Собственно запись обычно производится сигналом -WR или –CS, причем данные должны удерживаться в течение всего сигнала –WR (или –CS) и заданное время после его окончания. Сигнал –CS у некоторых микросхем памяти допускается держать активным (нулевым) для всех записываемых адресов и при этом подавать импульсы –WR для каждого адреса. Точно так же у некоторых микросхем допускается держать активным (нулевым) сигнал записи -WR, но при этом подавать импульсы –CS. В случае микросхем памяти с двунаправленной шиной данных необходимо использовать источник записываемых данных с выходом 3С или ОК, чтобы избежать конфликта данных, записываемых в память, с данными, выдаваемыми из памяти в режиме чтения. Для чтения информации из памяти надо выставить код адреса читаемой ячейки и подать сигналы –CS и –OE (если он имеется). Сигнал -WR в процессе чтения должен оставаться пассивным (равным единице). В некоторых микросхемах памяти (называемых нетактируемыми, например, К155РУ7, КР541РУ2, HM62256) можно держать активным (нулевым) сигнал –CS для всех читаемых адресов. В других микросхемах (называемых тактируемыми, например, КМ132РУ10, К537РУ8) необходимо подавать свой импульс –CS для каждого читаемого адреса. Понятно, что нетактируемые микросхемы гораздо удобнее в применении, чем тактируемые.  Рис. 12.3. Объединение микросхем памяти для увеличения разрядности шины данных Микросхемы оперативной памяти довольно часто объединяются для увеличения разрядности данных или разрядности адреса. На рис. 12.3 показано объединение четырех микросхем К155РУ7 для получения памяти с организацией 1Кх4. Точно так же могут быть объединены и микросхемы с двунаправленной шиной данных. К примеру, из четырех микросхем памяти с организацией 1Кх4 можно получить память с организацией 1Кх112. Для увеличения количества адресных разрядов используются те же методы, что и в случае ПЗУ (см. рис. 12.3). Если объединяются всего две микросхемы памяти, то можно обойтись без применения дешифраторов, выбирающих одну из объединяемых микросхем.  Рис. 12.4. Объединение микросхем памяти для увеличения разрядности шины адреса На рис. 12.4 показан вариант схемы объединения двух микросхем HM62256 для получения памяти с организацией 64Кх8. Дополнительный старший адресный разряд управляет прохождением сигнала –CS на одну из микросхем (при нулевом уровне на дополнительном адресном разряде сигнал –CS проходит на левую по рисунку микросхему, при единичном уровне - на правую по рисунку микросхему). Интересной особенностью микросхем оперативной памяти является возможность произвольного изменения порядка сигналов адресных разрядов без всяких последствий для функционирования памяти. Например, сигнал, поступающий на разряд А0, можно с тем же успехом подавать на А7, сигнал, приходящий на А7, подавать на А3, сигнал, приходящий на А3, подавать на А10 и т.д. Дело в том, что информация в оперативную память записывается по тем же самым адресам, по которым потом и читается, и перестановка адресных разрядов изменяет только номер ячейки, в которую записывается информация и из которой затем читается эта же информация. Такая взаимозаменяемость адресных входов оперативной памяти бывает полезной при проектировании разводки печатных плат. В случае ПЗУ это правило не работает, так как там информация записана раз и навсегда, и читать ее надо по тем же адресам, по которым ее ранее записали. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||