Микроконтроллеры группы PIC16F8X. 1-самостоятельная работа. Микроконтроллеры группы pic16F8X реферат

Скачать 122.47 Kb. Скачать 122.47 Kb.

|

|

Самостоятельная работа По предмету: Встраемые системы Тема: Микроконтроллеры группы PIC16F8X реферат Содержание 1. Основные характеристики 2. Особенности архитектуры 3. Организация памяти программ и стека 4. Организация памяти данных 5. Порты ввода/вывода 6. Память данных в РПЗУ (EEPROM) 7. Организация прерываний Заключение Использованные литературы 1. Основные характеристикиМикроконтроллеры подгруппы PIC16F8X относятся к семейству 8-разрядных КМОП микроконтроллеров группы PIC16CXXX, для которых характерны низкая стоимость, полностью статическая КМОП-технология и высокая производительность. В состав подгруппы входят МК PIC16F83, PIC16CR83, PIC16F84 и PIC16CR84. Основные характеристики МК подгруппы PIC16F8X приведены в табл. 1. Все микроконтроллеры подгруппы PIC16F8X используют гарвардскую архитектуру с RISC-процессором, обладающую следующими основными особенностями: · используются только 35 простых команд; · все команды выполняются за один цикл (400 нс при частоте 10 МГц), кроме команд перехода, которые требуют 2 цикла; · рабочая частота 0 Гц ... 10 МГц; · раздельные шины данных (8 бит) и команд (14 бит); · 512 х 14 или 1024 х 14 память программ, выполненная на ПЗУ или электрически перепрограммируемой Flash- памяти; · 15 восьмиразрядных регистров специальных функций (SFR); · восьмиуровневый аппаратный стек; · прямая, косвенная и относительная адресация данных и команд; · 36 или 68 восьмиразрядных регистров общего назначения (GPR) или ОЗУ; · четыре источника прерывания: o внешний вход RB0/INT; o переполнение таймера TMR0; o изменение сигналов на линиях порта B; o завершение записи данных в память EEPROM; · 64 x 8 электрически перепрограммируемая EEPROM память данных с возможностью выполнения 1000000 циклов стирания/записи; · сохранение данных в EEPROM в течение как минимум 40 лет.

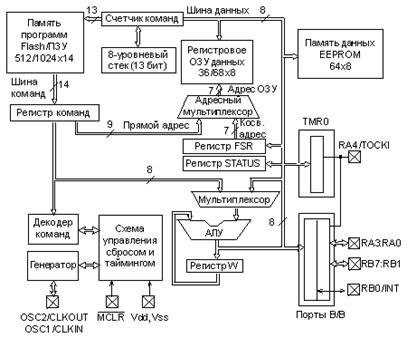

Микроконтроллеры подгруппы PIC16F8X обладают развитыми возможностями ввода/вывода: · 13 линий ввода-вывода с индивидуальной установкой направления обмена; · высокий втекающий/вытекающий ток, достаточный для управления светодиодами: · максимальный втекающий ток – 25 мА; · максимальный вытекающий ток – 20 мА; · 8-битный таймер/счетчик TMR0 с 8-битным программируемым предварительным делителем. Специализированные микроконтроллерные функции включают следующие возможности: · автоматический сброс при включении (Power-on-Reset); · таймер включения при сбросе (Power-up Timer); · таймер запуска генератора (Oscillator Start-up Timer); · сторожевой (Watchdog) таймер WDT с собственным встроенным генератором, обеспечивающим повышенную надежность; · EEPROM бит секретности для защиты кода; · экономичный режим SLEEP; · выбираемые пользователем биты для установки режима возбуждения встроенного генератора; · последовательное встроенное устройство программирования Flash/EEPROM памяти программ и данных с использованием только двух выводов. КМОП технология обеспечивает МК подгруппы PIC16F8X дополнительные преимущества: · статический принцип работы; · широкий диапазон напряжений питания: 2,0 ... 6,0 В; · низкое энергопотребление: · менее 2 мА при 5В и 4МГц; · порядка 15 мкА при 2В и 32КГц; · менее 1 мкА для SLEEP-режима при 2В. Микроконтроллеры подгруппы PIC16F8X различаются между собой только объемом ОЗУ данных, а также объемом и типом памяти программ. Наличие в составе подгруппы МК с Flash-памятью программ облегчает создание и отладку прототипов промышленных образцов изделий. 2. Особенности архитектурыУпрощенная структурная схема МК подгруппы PIC16F8X приведена на рис. 1.  Рис. 1. Структурная схема МК подгруппы PIC16F8X Архитектура основана на концепции раздельных шин и областей памяти для данных и для команд (гарвардская архитектура). Шина данных и память данных (ОЗУ) – имеют ширину 8 бит, а программная шина и программная память (ПЗУ) имеют ширину 14 бит. Такая концепция обеспечивает простую, но мощную систему команд, разработанную так, что битовые, байтовые и регистровые операции работают с высокой скоростью и с перекрытием по времени выборок команд и циклов выполнения. 14-битовая ширина программной памяти обеспечивает выборку 14-битовой команды в один цикл. Двухступенчатый конвейер обеспечивает одновременную выборку и исполнение команды. Все команды выполняются за один цикл, исключая команды переходов. Микроконтроллеры PIC16F83 и PIC16CR83 адресуют 512х14 памяти программ, а PIC16F84 и PIC16CR84 – 1Кх14 памяти программ. Вся память программ является внутренней. Микроконтроллер может прямо или косвенно обращаться к регистрам или памяти данных. Все регистры специальных функций, включая счетчик команд, отображаются на память данных. Ортогональная (симметричная) система команд позволяет выполнять любую команду над любым регистром с использованием произвольного метода адресации. Ортогональная архитектура и отсутствие специальных исключений делает программирование МК группы PIC16F8X простым и эффективным. Назначение выводов МК подгруппы PIC16F8X приведено в табл. 2.

Микроконтроллер содержит 8-разрядное АЛУ и рабочий регистр W. АЛУ является арифметическим модулем общего назначения и выполняет арифметические и логические функции над содержимым рабочего регистра и любого из регистров контроллера. АЛУ может выполнять операции сложения, вычитания, сдвига и логические операции. Если не указано иное, то арифметические операции выполняются в дополнительном двоичном коде. В зависимости от результата операции, АЛУ может изменять значения бит регистра STATUS: C (Carry), DC (Digit carry) и Z (Zero). 3. Организация памяти программ и стекаСчетчик команд в МК PIC16F8Х имеет ширину 13 бит и способен адресовать 8Кх14бит объема программной памяти. Однако физически на кристаллах PIC16F83 и PIC16CR83 имеется только 512х14 памяти (адреса 0000h-01FFh), а в МК PIC16F84 и PIC16CR84 – 1Кх14 памяти (адреса 0000h-03FFh). Обращение к адресам выше 1FFh (3FFh) фактически есть адресация в те же первые 512 адресов (первые 1К адресов). Организация памяти программ и стека приведена на рис. 4. В памяти программ есть выделенные адреса. Вектор сброса находится по адресу 0000h, вектор прерывания – по адресу 0004h. Обычно по адресу 0004h располагается подпрограмма идентификации и обработки прерываний, а по адресу 0000h – команда перехода на метку, расположенную за подпрограммой обработки прерываний.  Рис. 4. Организация памяти программ и стека 4. Организация памяти данныхПамять данных МК разбита на две области. Первые 12 адресов – это область регистров специальных функций (SFR), а вторая – область регистров общего назначения (GPR). Область SFR управляет работой прибора. Обе области разбиты в свою очередь на банки 0 и 1. Банк 0 выбирается обнулением бита RP0 регистра статуса (STATUS). Установка бита RP0 в единицу выбирает банк 1. Каждый банк имеет протяженность 128 байт. Однако для PIC16F83 и PIC16CR83 память данных существует только до адреса 02Fh, а для PIC16F84 и PIC16CR84 – до адреса 04Fh. На рис. 5 изображена организация памяти данных.  Рис. 5. Организация памяти данных Некоторые регистры специального назначения продублированы в обоих банках, а некоторые расположены в банке 1 отдельно. Регистры с адресами 0Ch-4Fh могут использоваться как регистры общего назначения, которые представляют собой статическое ОЗУ. Адреса регистров общего назначения банка 1 отображаются на банк 0. Следовательно, когда установлен банк 1, то обращение к адресам 8Ch-CFh фактически адресует банк 0. В регистре статуса помимо бита RP0 есть еще бит RB1, что позволяет обращаться к четырем страницам (банкам) будущих модификаций этого кристалла. К ячейкам ОЗУ можно адресоваться прямо, используя абсолютный адрес каждого регистра, или косвенно, через регистр указатель FSR. Косвенная адресация использует текущее значение разрядов RP1:RP0 для доступа к банкам. Это относится и к EEPROM памяти данных. В обоих случаях можно адресовать до 512 регистров. 5. Порты ввода/выводаКонтроллеры подгруппы PIC16F8X имеют два порта: PORTA (5 бит) и PORTB (8 бит) с побитовой индивидуальной настройкой на ввод или на вывод. Порт A (PORTA) представляет собой 5-битовый фиксатор, соответствующий выводам контроллера RA<4:0>. Линия RA4 имеет вход триггера Шмитта и выход с открытым стоком. Все остальные линии порта имеют ТТЛ входные уровни и КМОП выходные буферы. Адрес регистра порта А – 05h. Каждой линии порта поставлен в соответствие бит направления передачи данных, который хранится в управляющем регистре TRISA, расположенном по адресу 85h. Если бит управляющего TRISA регистра имеет значение 1, то соответствующая линия будет устанавливаться на ввод. Ноль переключает линию на вывод и одновременно выводит на нее содержимое соответствующего регистра-фиксатора порта. При включении питания все линии порта по умолчанию настроены на ввод. На рис. 8 дана схема линий RA<3:0> порта A.  Рис. 8. Схема линий RA <3:0 порта А. Выводы порта имеют защитные диоды к Vdd и Vss Операция чтения порта А считывает состояние выводов порта, в то время как запись в него изменяет состояние триггеров порта. Все операции с портом являются операциями типа "чтение-модификация-запись". Поэтому запись в порт предполагает, что состояние выводов порта вначале считывается, затем модифицируется и записывается в триггер-фиксатор. Вывод RA4 мультиплексирован с тактовым входом таймера TMR0. Схема линии RA4 порта А приведена на рис. 9. Порт В (PORTB) – это двунаправленный 8-битовый порт, соответствующий выводам RB<7:0> контроллера и расположенный по адресу 06h. Относящийся к порту В управляющий регистр TRISB расположен на первой странице регистров по адресу 86h. Если бит управляющего TRISB регистра имеет значение 1, то соответствующая линия будет устанавливаться на ввод. Ноль переключает линию на вывод и одновременно выводит на нее содержимое соответствующего регистра защелки. При включении питания все линии порта по умолчанию настроены на ввод.  Рис. 9. Схема линии RA4 порта А. Вывод порта имеет защитный диод только к Vss У каждой ножки порта В имеется небольшая активная нагрузка (около 100мкА) на линию питания (pull-up). Она автоматически отключается, если эта ножка запрограммирована как вывод. Более того, управляющий бит /RBPU регистра OPTION<7> может отключить (при RBPU=1) все нагрузки. Сброс при включении питания также отключает все нагрузки. Четыре линии порта В (RB<7:4>) могут вызвать прерывание при изменении значения сигнала на любой из них. Если эти линии настроены на ввод, то они опрашиваются и защелкиваются в цикле чтения Q1. Новая величина входного сигнала сравнивается со старой в каждом командном цикле. При несовпадении значения сигнала на ножке и в фиксаторе генерируется высокий уровень. Выходы детекторов "несовпадений" RB4, RB5, RB6, RB7 объединяются по ИЛИ и генерируют прерывание RBIF (запоминаемое в регистре INTCON<0>). Любая линия, настроенная как вывод, в этом сравнении не участвует. Прерывание может вывести кристалл из режима SLEEP. В подпрограмме обработки прерывания следует сбросить запрос прерывания одним из следующих способов: · прочитать (или записать в) порт В. Это завершит состояние сравнения; · обнулить бит RBIF регистра INTCON<0>. При этом необходимо иметь в виду, что условие "несовпадения" будет продолжать устанавливать признак RBIF. Только чтение порта В может устранить "несовпадение" и позволит обнулить бит RBIF. Прерывание по несовпадению и программно устанавливаемые внутренние активные нагрузки на этих четырех линиях могут обеспечить простой интерфейс, например, с клавиатурой, с выходом из режима SLEEP по нажатию клавиш. Схемы линий порта B приведены на рис. 10 и 11.  Рис. 10. Схема линий RB <7:4 порта B. Выводы порта имеют защитные диоды к Vdd и Vss  Рис. 11. Схема линий RB <3:0 порта B. Выводы порта имеют защитные диоды к Vdd и Vss При организации двунаправленных портов необходимо учитывать особенности организации ввода/вывода данных МК. Любая команда, которая осуществляет запись, выполняет ее внутри как "чтение-модификация-запись". Например, команды BCF и BSF считывают порт целиком, модифицируют один бит и выводят результат обратно. Здесь необходима осторожность. В частности, команда BSF PORTB, 5 (установить в единицу бит 5 порта B) сначала считывает все реальные значения сигналов, присутствующие в данный момент на выводах порта. Затем выполняются действия над битом 5, и новое значение байта целиком записывается в выходные фиксаторы. Если другой бит регистра PORTB используется в качестве двунаправленного ввода/вывода (скажем, бит 0), и в данный момент он определен как входной, то входной сигнал на этом выводе будет считан и записан обратно в выходной триггер-фиксатор этого же вывода, стирая предыдущее состояние. До тех пор, пока эта ножка остается в режиме ввода, никаких проблем не возникает. Однако если позднее линия 0 переключится в режим вывода, ее состояние будет неопределенным. На ножку, работающую в режиме вывода, не должны нагружаться внешние источники токов ("монтажное И", "монтажное ИЛИ"). Большие результирующие токи могут повредить кристалл. Необходимо выдерживать определенную последовательность обращения к портам ввода/вывода. Запись в порт вывода происходит в конце командного цикла. Но при чтении данные должны быть стабильны в начале командного цикла. Будьте внимательны в операциях чтения, следующих сразу за записью в тот же порт. Здесь надо учитывать инерционность установления напряжения на выводах. Может потребоваться программная задержка, чтобы напряжение на ножке (которое зависит от нагрузки) успело стабилизироваться до начала исполнения следующей команды чтения. 6. Память данных в РПЗУ (EEPROM)Микроконтроллеры подгруппы PIC6F8X имеют энергонезависимую память данных 64х8 EEPROM бит, которая допускает запись и чтение во время нормальной работы (во всем диапазоне питающих напряжений). Эта память не принадлежит области регистровой памяти ОЗУ. Доступ к ней осуществляется посредством косвенной адресации через регистры специальных функций: EEDATA <08h>, который содержит 8-битовые данные для чтения/записи и EEADR <09h>, включающий адрес ячейки, к которой идет обращение. Для управления процессом чтения/записи используются два регистра: EECON1 <88h> и EECON2 <89h>. При записи байта автоматически стирается предыдущее значение, и записываются новые данные (стирание перед записью). Все эти операции производит встроенный автомат записи EEPROM. Содержимое ячеек этой памяти при выключении питания сохраняется. Регистр EEADR может адресовать до 256 байт данных EEPROM. В МК подгруппы PIC6F8X используются только первые 64 байта, адресуемые шестью младшими битами EEADR<5:0>. Однако старшие два бита также декодируются. Поэтому эти два бита должны быть установлены в ‘0’, чтобы адрес попал в доступные 64 бита адресного пространства. Регистр EECON2 не является физическим регистром. Он используется исключительно при организации записи данных в EEPROM. Чтение регистра EECON2 дает нули. При считывании данных из памяти EEPROM необходимо записать нужный адрес в EEADR регистр и затем установить бит RD EECON1<0> в единицу. Данные появятся в следующем командном цикле в регистре EEDATA и могут быть прочитаны. Данные в регистре EEDATA фиксируются. При записи в память EEPROM необходимо сначала записать адрес в EEADR-регистр и данные в EEDATA-регистр. Затем следует выполнить специальную последовательность команд, производящую непосредственную запись: movlw 55h movwf EECON2 movlw AAh movwf EECON2 bsf EECON1,WR;установить WR бит, начать запись Во время выполнения этого участка программы все прерывания должны быть запрещены, для точного выполнения временной диаграммы. Время записи – примерно 10 мс. Фактическое время записи может изменяться в зависимости от напряжения, температуры и индивидуальных свойств кристалла. В конце записи бит WR автоматически обнуляется, а флаг завершения записи EEIF, он же запрос на прерывание, устанавливается. Для предотвращения случайных записей в память данных предусмотрен специальный бит WREN в регистре EECON1. Рекомендуется держать бит WREN выключенным, кроме тех случаев, когда нужно обновить память данных. Более того, кодовые сегменты, которые устанавливают бит WREN, и те, которые выполняют запись, следует хранить на различных адресах, чтобы избежать случайного выполнения их обоих при сбое программы. 7. Организация прерыванийМК подгруппы PIC16F8X имеют четыре источника прерываний: · внешнее прерывание с вывода RB0/INT; · прерывание от переполнения счетчика/таймера TMR0; · прерывание от изменения сигналов на линиях порта RB<7:4>; · прерывание по окончании записи данных в EEPROM. Все прерывания имеют один и тот же вектор/адрес – 0004h. Однако в управляющем регистре прерываний INTCON соответствующим битом-признаком записывается, от какого именно источника поступил запрос прерывания. Исключение составляет прерывание по завершении записи в EEPROM, признак которого находится в регистре EECON1. Бит общего разрешения/запрещения прерывания GIE (INTCON <7>) разрешает (если = 1) все индивидуально незамаскированные прерывания или запрещает их (если = 0). Каждое прерывание в отдельности может быть дополнительно разрешено/запрещено установкой/сбросом соответствующего бита в регистре INTCON. Бит GIE при сбросе обнуляется. Когда начинает обрабатываться прерывание, бит GIE обнуляется, чтобы запретить дальнейшие прерывания, адрес возврата посылается в стек, а в программный счетчик загружается адрес 0004h. Время реакции на прерывание для внешних событий, таких как прерывание от ножки INT или порта B, составляет приблизительно пять циклов. Это на один цикл меньше, чем для внутренних событий, таких как прерывание по переполнению от таймера TMR0. Время реакции всегда одинаковое. В подпрограмме обработки прерывания источник прерывания может быть определен по соответствующему биту в регистре признаков. Этот флаг-признак должен быть программно сброшен внутри подпрограммы. Признаки запросов прерываний не зависят от соответствующих маскирующих битов и бита общего маскирования GIE. Команда возврата из прерывания RETFIE завершает прерывающую подпрограмму и устанавливает бит GIE, чтобы опять разрешить прерывания. Логика прерываний контроллера изображена на рис. 14.  Рис. 5.14. Логика прерываний микроконтроллера Внешнее прерывание на ножке RB0/INT осуществляется по фронту: либо по нарастающему (если в регистре OPTION бит INTEDG=1), либо по спадающему (если INTEDG=0). Когда фронт обнаруживается на ножке INT, бит запроса INTF устанавливается в единицу (INTCON <1>). Это прерывание может быть замаскировано сбросом управляющего бита INTE в ноль (INTCON <4>). Бит запроса INTF необходимо очистить прерывающей программой перед тем, как опять разрешить это прерывание. Прерывание INT может вывести процессор из режима SLEEP, если перед входом в этот режим бит INTE был установлен в единицу. Состояние бита GIE также определяет, будет ли процессор переходить на подпрограмму прерывания после выхода из режима SLEEP. Переполнение счетчика TMR0 (FFh->00h) устанавливает в единицу бит запроса T0IF (INTCON<2>). Это прерывание может быть разрешено/запрещено установкой/сбросом бита маски T0IE (INTCON<5>). Сброс запроса T0IF – дело программы обработки. Любое изменение сигнала на одном из четырех входов порта RB<7:4> устанавливает в единицу бит RBIF (INTCON<0>). Это прерывание может быть разрешено/запрещено установкой/сбросом бита маски RBIE (INTCON<3>). Сброс запроса RBIF – дело программы обработки. Признак запроса прерывания по завершении записи в EEPROM, EEIF (EECON1<4>) устанавливается в единицу по окончании автоматической записи данных в EEPROM. Это прерывание может быть замаскировано сбросом бита EEIE (INTCON<6>). Сброс запроса EEIF – дело программы обработки. 1) Этот буфер имеет вход триггера Шмитта, когда конфигурируется в режиме RC-генератора и КМОП-вход в остальных случаях. 2) Этот буфер имеет вход триггера Шмитта, когда конфигурируется в качестве входа внешнего прерывания. 3) Этот буфер имеет вход триггера Шмитта, когда используется в режиме последовательного программирования. 4) Этот буфер имеет вход триггера Шмитта, когда используется в режиме последовательного программирования. Заключения: Эти микроконтроллеры представляют собой простые недорогие микроконтроллеры с минимальной периферией. Способность работать при малом напряжении питания (до 2 В) делает их удобными для применения в переносных конструкциях. В состав семейства входят микроконтроллеры подгруппы PIC16HV5XX, способные работать непосредственно от батареи в диапазоне питающих напряжений до 15 В; Использование в современном микроконтроллере достаточного мощного вычислительного устройства с широкими возможностями, построенного на одной микросхеме вместо целого набора, значительно снижает размеры, энергопотребление и стоимость построенных на его базе устройств. Используются в управлении различными устройствами и их отдельными блоками: в вычислительной технике: материнские платы, контроллеры дисководов жестких и гибких дисков, CD и DVD, электронике и разнообразных устройствах бытовой техники, в которой используется электронные системы управления — стиральных машинах, микроволновых печах, посудомоечных машинах, телефонах и современных приборах, различных роботах, системах «умный дом», и др.. В промышленности: устройства промышленной автоматики — от программируемого реле и встраиваемых систем до ПЛК, систем управления станками Использованные литературы: Бродин В. Б., Калинин А. В. Системы на микроконтроллерах и БИС программируемой логики. — М.: ЭКОМ, 2002. — ISBN 5-7163-0089-8. Жан М. Рабаи, Ананта Чандракасан, Боривож Николич. Цифровые интегральные схемы. Методология проектирования = Digital Integrated Circuits. — 2-е изд. — М.: Вильямс, 2007. — ISBN 0-13-090996-3. Микушин А. Занимательно о микроконтроллерах. — М.: БХВ-Петербург, 2006. — ISBN 5-94157-571-8. Новиков Ю. В., Скоробогатов П. К. Основы микропроцессорной техники. Курс лекций. — М.: Интернет-университет информационных технологий, 2003. — ISBN 5-7163-0089-8. Фрунзе А. В. Микроконтроллеры? Это же просто! — М.: ООО «ИД СКИМЕН», 2002. — Т. 1. — ISBN 5-94929-002-X. Фрунзе А. В. Микроконтроллеры? Это же просто! — М.: ООО «ИД СКИМЕН», 2002. — Т. 2. — ISBN 5-94929-003-8. Фрунзе А. В. Микроконтроллеры? Это же просто! — М.: ООО «ИД СКИМЕН», 2003. — Т. 3. — ISBN 5-94929-003-7. | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||