Особенности процессорных архитектур. Cisc и risc мархитектура. Их краткая характеристика

Скачать 2.4 Mb. Скачать 2.4 Mb.

|

|

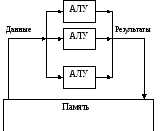

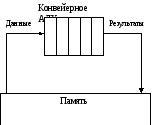

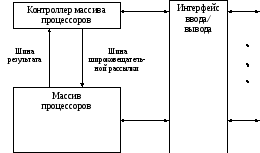

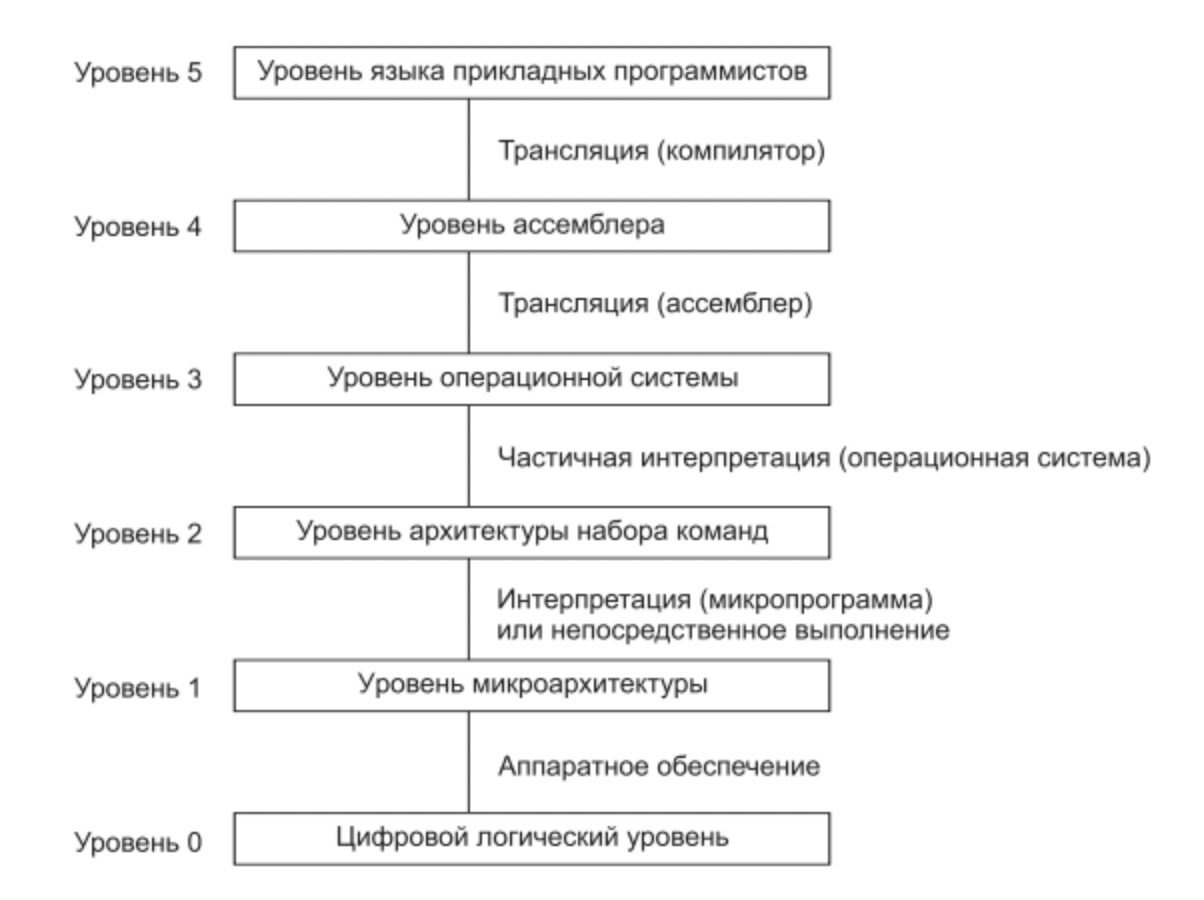

Особенности процессорных архитектур. CISC и RISC Мархитектура. Их краткая характеристика. Уровень архитектуры команд включает набор машинных команд, которые выполняются микропрограммой-интерпретатором или аппаратным обеспечением. Двумя основными архитектурами набора команд, используемыми компьютерной промышленностью на современном этапе развития вычислительной техники, являются архитектуры CISC и RISC. CISC – Complete Instruction Set Computer (CISC-архитектура, компьютер на микропроцессоре с полным набором команд) RISC– Reduced Instruction Set Computer (RISC-архитектура, компьютер с сокращенным набором команд) CISC (Complicated Instruction Set Computer — использующий полный набор команд). Традиционная архитектура с широкой системой команд МП. Характеризуется следующим набором свойств: · большим числом различных по формату и длине команд; · введением большого числа различных режимов адресации; · обладает сложной кодировкой инструкции. Процессору с архитектурой CISC приходится иметь дело с более сложными инструкциями неодинаковой длины. Выполнение одиночной CISC-инструкции может происходить быстрее, однако обрабатывать несколько таких инструкций параллельно сложнее. Достоинства архитектуры CISC Компактность наборов инструкций уменьшает размер программ и уменьшает количество обращений к памяти. Наборы инструкций включают поддержку конструкций высокоуровневого программирования. Недостатки архитектуры CISC Нерегулярность потока команд. Высокая стоимость аппаратной части. Сложности с распараллеливанием вычислений. · RISC (Reduced Instruction Set Computer). Архитектура с сокращенным набором команд. Все команды одинакового формата с простой кодировкой. Обращение к памяти происходит посредством команд загрузки и записи, остальные команды типа регистр-регистр. Команда, поступающая в CPU, уже разделена по полям и не требует дополнительной дешифрации. Часть кристалла освобождается для включения дополнительных компонентов. Степень интеграции ниже, чем в предыдущем архитектурном варианте, поэтому при высоком быстродействии допускается более низкая тактовая частота. Команда меньше загромождает ОЗУ, CPU дешевле. Программной совместимостью указанные архитектуры не обладают. Отладка программ на RISC более сложна. Данная технология может быть реализована программно-совместимым с технологией CISC (например, суперскалярная технология). Поскольку RISC-инструкции просты, для их выполнения нужно меньше логических элементов, что в конечном итоге снижает стоимость процессора. Но большая часть программного обеспечения сегодня написана и откомпилирована специально для CISC-процессоров фирмы Intel. Для использования архитектуры RISC нынешние программы должны быть перекомпилированы, а иногда и переписаны заново. Достоинства архитектуры RISC 1.снижение нерегулярности потока команд 2.обогащение пространственным параллелизмом Недостатки архитектуры RISC 1.каждое действие выполняется в 1 такт 2. Виды обеспечения вычислительных систем. Определения. Примеры.Выделяются следующие основные виды обеспечения вычислительных систем: программное, техническое (аппаратное), математическое, информационное, лингвистическое, организационное и методическое. Программное обеспечение — это совокупность всей информации, данных и программ, которые обрабатываются компьютерными системами. Прикладное программное обеспечение предоставляет пользователю дружественный интерфейс общения с ЭВМ. Для составления программы ему достаточно знать правила по использованию ЭВМ в терминах своей предметной области — предметно-ориентированную среду программирования. (Текстовые редакторы, веб браузеры, экспертные системы, профессиональное программное обеспечение - сапр и тд.) Системное программное обеспечение является неотъемлемой частью ЭВМ. Это программы, управляющие работой компьютера и выполняющие различные вспомогательные функции, например, управление ресурсами компьютера, создание копий информации, проверка работоспособности устройств компьютера, выдача справочной информации о компьютере и др. Инструментальное ПО Специфическое обеспечение любой компьютерной техники. Его можно было бы отнести к прикладному, но из-за специфики применения его выделили в отдельный вид. Основная функция – отладка, настройка, переписывание программного кода. Сюда входят компиляторы, отладчики, переводчики высокого уровня, редакторы, интерпретаторы и другие средства. Они необходимы, потому что техника не понимает человеческих слов. Чтобы ей «объяснить», что надо сделать, требуется специальный «машинный язык». Математическое обеспечение ЭВМ. Математическое обеспечение — МО состоит из фонда программ вычислительных алгоритмов, в частности, фонд содержит решения типовых задач математической физики.(Короче это математические проги). Математическое обеспечение – совокупность математических методов, моделей, алгоритмов обработки информации, используемых при решении задач в информационной системе (функциональных и автоматизации проектирования информационных систем). Аппаратное обеспечение (англ. hardware – аппаратные средства, технические средства) включает в себя все физические части компьютера, но не включает программное обеспечение, которое им управляет, и не включает информацию, имеющуюся на компьютере. Под аппаратным обеспечением понимают обычно все узлы, модули и блоки, составляющие компьютер или компьютерную систему. В современных компьютерах используется «открытая архитектура», т.е. состав аппаратного обеспечения компьютера можно изменить, поменяв один из модулей, или расширить, вставив дополнительный модуль. Лингвистическое обеспечение представляет собой целостную совокупность формальных языков описания информации и алгоритмов ее обработки. Информационно обеспечение Совокупность программ и предварительно подготовленных данных, необходимых для работы этих программ. Рассмотрим, например, систему автоматической проверки орфографии в редактируемом тексте. Ее работа заключается в том, что лексические единицы исходного текста сравниваются с заранее заготовленным массивом данных (словарем). В данном случае для успешной работы системы необходимо иметь кроме аппаратного и программного обеспечения специальные наборы словарей, подключаемые извне. Это пример информационного обеспечения вычислительной техники. Организационное обеспечение системы — это организация следующих работ и мероприятий: создание структуры, обеспечивающей нормальную эксплуатацию системы; ввод в действие системы; опытно-производственная эксплуатация и проведение приемочных испытаний; ввод в промышленную эксплуатацию. Включает положения, инструкции, приказы, штатные расписания, квалификационные требования и другие документы, регламентирующие организационную структуру подразделений проектной организации и их взаимодействие с комплексом средств автоматизированного проектирования. Методическое обеспечение определяет объект проектирования, процесс проектирования и взаимосвязь между машиной и человеком (т.е. что проектировать и как управлять процессом проектирования). Разработка методического обеспечения требует знаний предметной области проектирования и технических средств, с тем, чтобы определить, какие задачи и этапы проектирования выполнять в автоматическом режиме, какие оставить за проектировщиком, а какие необходимо осуществлять в интерактивном режиме пользователя и системы. Методическое обеспечение включает также пакет документов, в которых отражены состав, правила отбора и эксплуатации средств автоматизации проектирования. Кроме того, в методических документах каждой системы излагается технология проектирования, дается описание циклов проектирования, типовых сочетаний программ, рационального распределения функций между человеком и ЭВМ. 3. Векторные и векторно-конвейерные вычислительные системы. Матричные вычислительные системы. К классу SIMD относятся вычислительные системы, где множество элементов данных подвергается параллельной, но однотипной обработке. В SIMD-системах имеется одно устройство управления, обеспечивающее последовательное выполнение команд программы. На стадии выполнения общая команда транслируется множеству процессоров (в простейшем случае — АЛУ), каждый из которых обрабатывает свои данные. Векторные и векторно-конвейерные вычислительные системы. Хотя производительность ВС общего назначения неуклонно возрастает, по-прежнему остаются задачи, требующие существенно большей вычислительной мощности. К таким, прежде всего, следует отнести задачи моделирования реальных процессов и объектов, для которых характерна обработка больших регулярных массивов чисел в форме с плавающей запятой. Большие регулярные массивы чисел в форме с плавающей запятой представляются матрицами и векторами, а алгоритмы их обработки описываются в терминах матричных операций. Как известно, основные матричные операции сводятся к однотипным действиям над парами элементов исходных матриц, которые чаще всего можно производить параллельно. Для обработки массивов требуются вычислительные средства, позволяющие с помощью единой команды производить действие сразу над всеми элементами массивов — средства векторной обработки. Под вектором понимается одномерный массив однотипных данных (обычно в форме с плавающей точкой), регулярным образом расположенный в памяти вычислительной системы. Если обработке подвергаются многомерные массивы, их также рассматривают как векторы. Векторный процессор – процессор, в котором операндами некоторых команд могут выступать упорядоченные массивы данных – векторы. Векторный процессор может быть реализован в двух вариантах. В первом он представляет собой дополнительный блок к универсальной вычислительной машине (системе). Во втором – векторный процессор является как основой самостоятельной ВС. Наиболее распространенными подходами к архитектуре средств векторной обработки являются: -  конвейерное АЛУ: конвейерное АЛУ:- массив АЛУ:  В варианте с конвейерным АЛУ предполагается, что операции над числами достаточно сложны и поддаются разбиению на отдельные фазы. В варианте с массивом АЛУ одновременные операции над элементами векторов проводятся с помощью нескольких параллельно используемых АЛУ. Матричные вычислительные системы. Назначение матричных вычислительных систем во многом схоже с назначением векторных ВС — обработка больших массивов данных. В основе матричных систем лежит матричный процессор (array processor), состоящий из регулярного массива процессорных элементов (ПЭ). Организация систем подобного типа на первый взгляд достаточно проста. Они имеют общее управляющее устройство, генерирующее поток команд, и большое число ПЭ, работающих параллельно и обрабатывающих каждый свой поток данных. Однако на практике, чтобы обеспечить достаточную эффективность системы при решении широкого круга задач, необходимо организовать связи между процессорными элементами так, чтобы наиболее полно загрузить процессоры работой. Именно характер связей между ПЭ и определяет разные свойства системы. Ранее уже отмечалось, что подобная схема применима и для векторных вычислений. Между матричными и векторными системами есть существенная разница. Матричный процессор интегрирует множество идентичных функциональных блоков (ФБ), логически объединенных в матрицу и работающих в SIMD-стиле. Не столь существенно, как конструктивно реализована матрица процессорных элементов — на едином кристалле или на нескольких. Важен сам принцип — ФБ логически скомпонованы в матрицу и работают синхронно, то есть присутствует только один поток команд для всех блоков. Векторный процессор имеет встроенные команды для обработки векторов данных, что позволяет эффективно загрузить конвейер из функциональных блоков. В свою очередь, векторные процессоры проще использовать, потому что команды для обработки векторов — это более удобная для человека модель программирования, чем SIMD. Структура:  Массив процессоров (МПр) производит параллельную обработку множественных элементов данных. Единый поток команд, управляющий обработкой данных в массиве процессоров, генерируется контроллером массива процессоров (КМП). КМП выполняет последовательный программный код, реализует операции условного и безусловного перехода, транслирует в МПр команды, данные и сигналы управления. Команды выполняются процессорами в режиме жесткой синхронизации. Сигналы управления используются для синхронизации команд и пересылок, а также для управления процессом вычислений. Команды, данные и сигналы управления передаются из КМП в массив процессоров по шине широковещательной рассылки. Поскольку выполнение операций условного перехода зависит от результатов вычислений, результаты обработки данных в массиве процессоров транслируются из КМП по шине результата. Массив процессоров помимо множества процессоров должен включать в себя множество модулей памяти. Кроме того, в массиве должна быть реализована сеть взаимосвязей, как между процессорами, так и между процессорами и модулями памяти. Таким образом, под термином массив процессоров понимается блок, состоящий из процессоров, модулей памяти и сети соединений. В матричных SIMD-системах распространение получили распространение два основных типа архитектурной организации массива процессорных элементов. В первом варианте “процессорный элемент-процессорный элемент“ (“ПЭ-ПЭ“) все процессорные элементы (ПЭ) связаны между собой сетью соединений. Каждый ПЭ – это процессор с локальной памятью. Процессорные элементы выполняют команды, получаемые из КМП по шине широковещательной рассылки, и обрабатывают данные как хранящиеся в их локальной памяти, так и поступающие из КМП. Для трансляции результатов из отдельных ПЭ в КМП служит шина результата. Второй вид архитектуры - “процессор-память“. В этом случае двунаправленная сеть соединений связывает множество процессоров с множеством модулей памяти. Процессоры управляются через шину широковещательной рассылки. Обмен данными между процессорами осуществляется как через сеть, так и через модули памяти. 4. Метрики производительности конвейера Чтобы охарактеризовать эффект, достигаемый за счет конвейеризации вычислений, обычно используют три метрики: ускорение, эффективность и производительность. Под ускорением понимается отношение времени обработки без конвейера и при его наличии. Теоретически наилучшее время обработки входного потока из N значений TNK на конвейере с К ступенями и тактовым периодом TK можно определить выражением: Формула отражает тот факт, что до появления на выходе конвейера результата обработки первого элемента должно пройти K тактов, а последующие результаты будут следовать в каждом такте. В процессоре без конвейера общее время выполнения составляет NKTK. Таким образом, ускорение вычислений S за счет конвейеризации вычислений можно описать формулой: При N-->∞ ускорение стремится к величине, равной количеству ступеней в конвейере. Еще одной метрикой, характеризующей конвейерный процессор, является эффективность Е — доля ускорения, приходящаяся на одну ступень конвейера: В качестве третьей метрики часто выступает пропускная способность или производительность Р — эффективность, деленная на длительность тактового периода: При N-->∞ эффективность стремится к единице, а производительность – к частоте тактирования конвейера:  . .5. Классы конфликтов, возникающих в конвейерах и способы их устранения. Конфликты — это такие ситуации в конвейерной обработке, которые препятствуют выполнению очередной команды в предназначенном для нее такте. Конфликты делятся на три группы: Структурные (аппаратные средства процессора не могут поддерживать все возможные комбинации команд в режиме одновременного выполнения с совмещением) по управлению (возникают при конвейеризации команд переходов и других команд, изменяющих значение счетчика команд) по данным (возникают в случаях, когда выполнение одной команды зависит от результата выполнения предыдущей команды) Причины структурных конфликтов: 1. Не полностью конвейерная структура процессора, при которой некоторые ступени отдельных команд выполняются более одного такта. Этой ситуации можно было бы избежать двумя способами. Первый предполагает увеличение времени такта до такой величины, которая позволила бы все этапы любой команды выполнять за один такт. Однако при этом существенно снижается эффект конвейерной обработки, так как все этапы всех команд будут выполняться значительно дольше, в то время как обычно нескольких тактов требует выполнение лишь отдельных этапов очень небольшого количества команд. Второй способ предполагает использование таких аппаратных решений, которые позволили бы значительно снизить затраты времени на выполнение действия, приводящего к появлению "пузырей" (например, использовать матричные схемы умножения). Но это приведет к усложнению схемы процессора и сокращению на кристалле места для реализации на этой БИС других, функционально более важных узлов. 2. Недостаточное дублирование некоторых ресурсов. Одним из типичных примеров таких конфликтов служит конфликт из-за доступа к запоминающим устройствам. Борьба с конфликтами такого рода проводится путем увеличения количества однотипных функциональных устройств, которые могут одновременно выполнять одни и те же или схожие функции Разрешение этой ситуации состоит в том, чтобы дать возможность выполняться командам в одном конвейере вне зависимости от ситуации в других конвейерах, а аппаратные средства микропроцессора должны гарантировать, что результаты выполненных команд будут записаны в приемник в том порядке, в котором команды записаны в программе. Это обеспечивается путем использования так называемого принципа неупорядоченного выполнения команд. Суть его заключается в следующем. Блок выборки и декодирования выбирает команды из памяти и заносит их в буфер команд. По мере готовности операндов и исполнительного блока соответствующего типа команды извлекаются из буфера для обработки. Порядок их исполнения может отличаться от предписанного программой. Решение конфликтов по управлению: Простейший способ разрешения этой ситуации - использование так называемого метода выжидания. Он заключается в замораживании операций в конвейере путем блокировки выполнения любой команды, следующей за командой условного перехода, до тех пор, пока не станет известным направление перехода. Привлекательность такого решения заключается в его простоте. Главный недостаток - резкое уменьшение преимуществ конвейерной обработки. В инженерных задачах примерно каждая шестая команда является командой условного перехода, поэтому приостановки конвейера при выполнении команд переходов до определения истинного направления перехода существенно скажутся на производительности процессора. Решение конфликтов по данным: Устранение конфликтов, связанных с ложными взаимозависимостями данных, часто возможно путем переименования регистров (register renamINg). Суть этого механизма заключается в следующем. Процессоры, использующие переименование регистров, фактически имеют больше восьми регистров, определяемых архитектурой х86 или IA32. При этом если какой-либо команде требуется использовать регистр, процессор динамически ставит в соответствие этому логическому (архитектурному) регистру один из более многочисленных физических регистров. Если другая команда пытается обратиться к тому же логическому регистру, процессор для предотвращения конфликта может поставить ему в соответствие другой физический регистр. Такие переименования действуют, пока команды продвигаются по конвейерам. 6. Сигналы. Объем информации. Количество информации и энтропия. Свойства информации. Сигнал (лат. signum — знак) — процесс изменения во времени физического состояния какого-либо объекта, служащий для отображения, регистрации или передачи сообщений. Сигнал — это материальный носитель (переносчик) сообщений Для информации существуют свои единицы измерения информации. Если рассматривать сообщения информации как последовательность знаков, то их можно представлять битами, а измерять в байтах, килобайтах, мегабайтах, гигабайтах, терабайтах и петабайтах. Единицей измерения количества информации является бит – это наименьшая (элементарная) единица. Байт – основная единица измерения количества информации. Байт – довольно мелкая единица измерения информации. Например, 1 символ – это 1 байт. 1 байт = 8 бит 1 Кб = 1024 байта 1 Мб = 1024 Кб 1 Гб = 1024 Мб 1 Тб = 1024 Гб 1 Пб = 1024 Тб Энтропия — это среднее кол-во информации приходящееся на одно сообщение Свойства информации: 1. Полнота — свойство информации исчерпывающе (для данного потребителя) характеризовать отображаемый объект или процесс; 2. Актуальность — способность информации соответствовать нуждам потребителя в нужный момент времени; 3. Достоверность — свойство информации не иметь скрытых ошибок. Достоверная информация со временем может стать недостоверной, если устареет и перестанет отражать истинное положение дел; 4. Доступность — свойство информации, характеризующее возможность ее получения данным потребителем; 5. Релевантность — способность информации соответствовать нуждам (запросам) потребителя; 6. Защищенность — свойство, характеризующее невозможность несанкционированного использования или изменения информации; 7. Эргономичность — свойство, характеризующее удобство формы или объема информации с точки зрения данного потребителя. 7. Устройство управления современного процессора. Определение. Микрокоманда. Микрооперация. Микропрограмма. Задачи, решаемые устройством управления. Устройство управления (УУ) - узел микропроцессора, выполняющий управление компонентами. Оно вырабатывает распределенную во времени и пространстве последовательность внутренних и внешних управляющих сигналов, обеспечивающих выборку и выполнение команд. На этапе цикла выборки команды УУ интерпретирует команду, выбранную из программной памяти. На этапе выполнения команды в соответствии с типом реализуемой операции УУ формирует требуемый набор команд низкого уровня для арифметико-логического устройства и других устройств. Эти команды задают последовательность простейших низкоуровневых операций, таких, как пересылка данных, сдвиг данных, установка и анализ признаков, запоминание результатов и др. Такие элементарные низкоуровневые операции называют микрооперациями, а команды, формируемые устройством управления, называются микрокомандами. Последовательность микрокоманд, соответствующая одной команде, называется микропрограммой. В задачи устройства управления входит выборка и декодирование потока инструкций, выдача кодов функций в исполнительные устройства, принятие решений по признакам результатов вычислений, синхронизация узлов микропроцессора. 8. Организация ввода/вывода в вычислительной системе. Системные и локальные шины. Устройства ввода/вывода Вводом/выводом называют передачу данных между ядром ЭВМ, включающим в себя процессор и ОП(оперативная память), и периферийными устройствами. Система ввода-вывода – это единственное средство общения ЭВМ с внешним миром. Ее возможности в серийных ЭВМ представляют собой один из важнейших параметров, определяющих выбор машины для конкретного применения. Существует три режима ввода-вывода: · Программный ввод-вывод (нефорсированный). · ввод-вывод по прерыванию (форсированный). · Прямой доступ к памяти (ПДП). Программный ввод-вывод. Инициирование и управление вводом-выводом осуществляет процессор по командам прикладной программы. Периферийные устройства играют пассивную роль и только сигнализируют о своем состоянии, в частности о готовности к операциям ввода-вывода. Ввод-вывод по прерыванию. Операции ввода-вывода инициирует периферийное устройство, генерируя сигнал запроса прерывания, при этом процессор переключается на подпрограмму обслуживания данного периферийного устройства, вызвавшего прерывание. Непосредственно операциями ввода-вывода управляет процессор. Прямой доступ к памяти. Процессор в передаче данных не участвует. Он отключается от системной магистрали, а все операции обмена данными идут под управлением специального управляющего устройства – контроллера ПДП. Этот режим используется для быстродействующих периферийных устройств, когда пропускной способности процессора недостаточно. Передача данных осуществляется двумя способами: а) отдельными битами, и тогда промежуточный интерфейс называется последовательным; б) полными словами (например, целым байтом), и тогда промежуточный интерфейс называется параллельным. Информация, передаваемая в процессе ввода-вывода, подразделяется: а) на собственно данные; б) управляющие данные. Управляющие данные от процессора называются также командными словами или приказами. Они инициируют действия, не связанные непосредственно с передачей данных (запуск устройства, запрещение прерываний, установка режимов и т.д.). Управляющие данные от периферийного устройства называются словами состояния. Они содержат информацию об определенных признаках (о готовности устройства к передаче данных, о наличии ошибок при обмене и т.д.). Состояние обычно представляется в декодированной форме – один бит для каждого признака. Одним из простейших механизмов, позволяющих организовать взаимодействие различных подсистем, является единственная центральная шина, к которой подсоединяются все подсистемы. Системная шина - шина, предназначенная для передачи данных между периферийными устройствами и центральным процессором, или между периферийными устройствами и оперативной памятью. Локальной шиной называется шина, электрически выходящая непосредственно на контакты микропроцессора. Она обычно объединяет процессор, память, схемы буферизации для системной шины и ее контроллер, а также некоторые вспомогательные схемы. Типичными примерами локальных шин является PCI. Локальная шина предназначена для обеспечения непосредственного доступа процессора к периферийным устройствам (например, графическим или сетевым адаптерам). ((Системная шина ISA позволяет синхронизировать работу процессора и шины с разными тактовыми частотами. Она работает на частоте 8 МГц, что соответствует максимальной скорости передачи 16 Мбайт/с. Системная шина EISA обеспечивает адресное пространство в 4 Гбайт, 32-битовую передачу данных (в том числе и в режиме DMA), улучшенную систему прерываний и арбитраж DMA, автоматическую конфигурацию системы и плат расширения. Устройства шины ISA могут работать на шине EISA. Шина PCI (Peripheral Component Interconnect) поддерживает 32-битовый канал передачи данных между процессором и периферийными устройствами, работает на тактовой частоте 33 МГц и имеет максимальную пропускную способность 120 Мбайт/с.)) Устройства ввода. По большей части данная техника является датчиком, которые преобразует неэлектрические величин, в сигналы или же цифровой код. Таким образом человек и прочие аспекты, могут взаимодействовать с компьютером, работать с ним. Говоря более простым языком, устройство ввода – это такая техника, которая является переводчиком между вами и компьютером, помогая вам достичь полного понимания и качественной работы. Самые популярные представители данного вида: Мышка, преобразует перемещения в сигнал, чтобы компьютер понимал, что вы производите те или иные действия. Клавиатура, посылает сигналы о нажатии клавиш для взаимодействия с ПК. Устройства вывода. Второй тип, главная цель подобной техники – это преобразовать цифровой код, который подается аппаратным обеспечением компьютера, в неэлектрические сигналы или же графическую информацию. С устройствами вывода, человек взаимодействует ежедневно. В список популярных представителей входят следующие виды техники: Монитор, переводит сигналы в удобную для человеческого восприятия форму, а именно в графическое изображение, таким образом пользователь может работать с ПК. Принтер – это устройство, которое преображает цифровые файлы и отпечатывает их на бумаге. Таким образом человек может преобразовать цифровой файл и физический вид. Акустическая система – переводит сигналы в звуковое сопровождение. В данную категорию входят колонки, наушники и прочие, подобные устройства. Имеется третья категория, которая совмещает две предыдущие, а именно устройства ввода-вывода. Они совмещают в себе качества двух предыдущих групп, таким образом могут, как принимать сигнал, так и раздавать его. В число подобных устройств входят: Интерактивные доски. Дисководы. Роутеры и подобные устройства. 9. Классификация вычислительных систем. Альтернативная классификация. Под вычислительной системой (ВС) понимают совокупность взаимосвязанных и взаимодействующих процессоров или ЭВМ, периферийного оборудования и программного обеспечения, предназначенную для сбора, хранения, обработки и распределения информации. Существует большое количество признаков, по которым классифицируют вычислительные системы. По назначению вычислительные системы делят на: универсальные и специализированные. Специализированные системы ориентированы на решение узкого класса задач, в отличие от универсальных, предназначенных для широкого спектра задач. По типу построения вычислительные системы разделяются на: -многомашинные-многопроцессорные По типу ЭВМ или процессоров, используемых для построения ВС, различают: -однородные системы -неоднородные системы. По методам управления элементами ВС различают: -централизованные -децентрализованные -со смешанным управлением. По степени территориальной разобщенности вычислительных модулей ВС делятся на системы: территориально-сосредоточенные – это когда все компоненты располагаются в непосредственной близости друг от друга; распределенные – это когда компоненты могут располагаться на значительном расстоянии, например, вычислительные сети; структурно-одноуровневые – это когда имеется лишь один общий уровень обработки данных; многоуровневые (иерархические) структуры – это когда в иерархических ВС машины или процессоры распределены по разным уровням обработки информации, некоторые машины (процессоры) могут специализироваться на выполнении определенных функций. По режиму работы ВС различают системы, работающие в оперативном и неоперативном временных режимах. Альтернативная классификация. Все вычислительные системы в зависимости от способа обработки информации, заложенного в их архитектуру, можно разделить на четыре класса. Разрядно-последовательные пословно-последовательные (n=m=1). В каждый момент времени такие компьютеры обрабатывают только один двоичный разряд. Представителем данного класса служит давняя система MINIMA с естественным описанием (1,1). Разрядно-параллельные пословно-последовательные (n > 1 , m = 1). Большинство классических последовательных компьютеров, принадлежит к данному классу: IBM 701 с описанием (36,1), PDP-11 (16,1), IBM 360/50 и VAX 11/780 - с описанием (32,1). Разрядно-последовательные пословно-параллельные (n = 1 , m > 1). Как правило, вычислительные системы данного класса состоят из большого числа одноразрядных процессорных элементов, каждый из которых может независимо от остальных обрабатывать свои данные. Типичными примерами служат STARAN (1, 256) и MPP (1,16384) фирмы Goodyear Aerospace, прототип известной системы ILLIAC IV компьютер SOLOMON (1, 1024) и ICL DAP (1, 4096). Разрядно-параллельные пословно-параллельные (n > 1, m > 1). Большая часть существующих параллельных вычислительных систем, обрабатывая одновременно mn двоичных разрядов, принадлежит именно к этому классу: ILLIAC IV (64, 64), TI ASC (64, 32), C.mmp (16, 16), CDC 6600 (60, 10), BBN Butterfly GP1000 (32, 256). 10. Назначение, принципы построения и характеристики арифметико-логических устройств (АЛУ). Арифметико-логическое устройство (АЛУ) (англ. arithmetic and logic unit, ALU) – устройство или же блок процессора, который предназначен для выполнения логических и математических операций над двоичными числами. АЛУ входит в состав любого микропроцессора. Пример работы АЛУ на операции сложения Функционально АЛУ состоит из двух регистров (Регистр1, Регистр 2), схемы управления и сумматора. Арифметическая операция выполняется по тактам: ● Значения операнда 1, участвующего в арифметической операции по шине данных поступает в Регистр 1 ● Значения операнда 2, участвующего в арифметической операции по шине данных поступает в Регистр 2 ● По шине инструкций поступает инструкция на выполнение операции в схему управления ● Данные из регистров поступают в сумматор, схема управления дает команду на выполнение сложения ● Результат сложения поступает в Регистр 1 ● Признаки выполнения операции в АЛУ поступают в регистр флагов. Характеристики АЛУ: ● Разрядность ● Состав операции ● Форматы обрабатываемых данных ● Способ построения и функционирования ● Быстродействие ● Надежность 11. Многоуровневая организация ЭВМ. Структурная организация и архитектура вычислительных систем. Многоуровневая организация ЭВМ:  Большинство современных компьютеров состоит из двух и более уровней. Существуют машины даже с шестью уровнями. Уровень 0 — это аппаратное обеспечение машины. Его электронные схемы исполняют машинно зависимые программы уровня 1. На цифровом логическом уровне объекты называются вентилями. Хотя вентили строятся из аналоговых компонентов (таких как транзисторы), они могут быть точно смоделированы как цифровые устройства. У каждого вентиля есть одно или несколько цифровых входных данных (сигналов, представляющих 0 или 1). Вентиль вычисляет простые функции этих сигналов, такие, как И или ИЛИ. Каждый вентиль формируется из нескольких транзисторов. Несколько вентилей формируют 1 бит памяти, который может содержать 0 или 1. Биты памяти, объединенные в группы, например, по 16, 32 или 64, формируют регистры. Каждый регистр может содержать одно двоичное число в определенном диапазоне.\ Следующий уровень называется уровнем микроархитектуры. На этом уровне находятся наборы из (обычно) 8 или 32 регистров, которые формируют локальную память и схему, называемую АЛУ (арифметико-логическое устройство). АЛУ исполняет простые арифметические операции. Регистры вместе с АЛУ формируют тракт данных, по которому поступают данные. Уровень 2 - уровень архитектуры набора команд. Каждый производитель публикует руководство для компьютеров, которые он продает, под названием «Руководство по машинному языку X», «Принципы работы компьютера Y» и т. п. Подобное руководство содержит информацию именно об этом уровне, а не о более низких уровнях. Описываемый в нем набор машинных команд в действительности исполняется микропрограммой-интерпретатором или аппаратным обеспечением. Следующий уровень обычно является гибридным. Большинство команд в его языке есть также и на уровне архитектуры набора команд (команды, имеющиеся на одном из уровней, вполне могут быть представлены и на других уровнях). У этого уровня есть некоторые дополнительные особенности: новый набор команд, другая организация памяти, способность исполнять две и более программ одновременно и некоторые другие. При построении уровня 3 возможно большее разнообразие, чем при построении уровней 1 и 2. Между уровнями 3 и 4 есть принципиальная разница. Нижние три уровня не предназначены для использования рядовыми программистами. Они изначально ориентированы на интерпретаторы и трансляторы, обеспечивающие работу на более высоких уровнях. Эти трансляторы и интерпретаторы создаются системными программистами, которые специализируются на разработке новых виртуальных машин. Уровни с четвертого и выше предназначены для прикладных программистов, решающих конкретные задачи. Структурная организация и архитектура вычислительных систем: Организация ВС: Структурная организация определяет устройство ВС – задает структуру на уровне устройств ВС и организацию связей между этими устройствами на уровне аппаратных интерфейсов; Функциональная организация определяет принципы функционирования ВС, т. е. собственно вычислительные процессы. Два уровня представления архитектуры ВС: 1. Программная архитектура включает в себя аспекты, видимые программистам и, соответственно, программам; 2. Аппаратная архитектура включает аспекты, невидимые для программиста Основные компоненты архитектуры ВС: 1. Вычислительные и логические возможности 1. Система команд 2. Формат команд - то, из чего состоит команда 3. Способы адресации 4. Назначение и состав регистров 2. Аппаратные средства 1. Структура 2. Организация памяти 3. Организация ввода-вывода 4. Принципы управления 3. Программное обеспечение 1. ОС 2. Языки программирования 3. Прикладное ПО 12 Основные архитектурные понятия. Типы команд. Типы данных Способы адресации. Основные архитектурные понятия: Архитектура – совокупность общих принципов организации аппаратно-программных средств и их характеристик, определяющая функциональные возможности вычислителя при решении соответствующих классов задач. Архитектура – логическое построение вычислителя, как оно представляется программисту, разрабатывающему программу на машинно-ориентированном языке. В рамках этого подхода архитектура определяет возможности ВС, а организация – реализацию этих возможностей в конкретных моделях. Алгоритм — конечный набор предписаний, позволяющий получить регулярным путем решение задачи за конечное число шагов. Алгоритм обладает рядом свойств: дискретность, конечность, массовость, результативность. Программа — упорядоченная последовательность команд, подлежащих обработке на ЭВМ. Алгоритм решения задачи вводится в ЭВМ в виде программы, написанной на каком-либо языке программирования, и хранится в памяти ЭВМ в форме машинных кодов команд, осуществляющих управление ходом вычислительного процесса. Типы команд: Команды передачи данных (перепись), копирующие информацию из одного места в другое. Арифметические операции, которым фактически обязана своим рождением вычислительная техника. Конечно, доля вычислительных действий в современном компьютере заметно уменьшилась, но они по-прежнему играют в программах важную роль. Отметим, что к основным арифметическим действиям обычно относятся сложение и вычитание (последнее внутри процессора чаще всего тем или иным способом также сводится к сложению). Что касается умножения и деления, то они во многих ЭВМ выполняются по специальным программам. Логические операции, позволяющие компьютеру производить анализ получаемой информации. После выполнения такой команды, с помощью условного перехода ЭВМ способна выбрать дальнейший ход выполнения программы. Простейшими примерами команд рассматриваемой группы могут служить сравнение, а также известные логические операции И, ИЛИ, НЕ (инверсия). Кроме того, к ним часто добавляются анализ отдельных битов кода, их сброс и установка. Сдвиги двоичного кода влево и вправо. Для доказательства важности этой группы команд достаточно вспомнить правило умножения столбиком: каждое последующее произведение записывается в такой схеме со сдвигом на одну цифру влево. В некоторых частных случаях умножение и деление вообще может быть заменено сдвигом (вспомните, что, дописав или убрав ноль справа, т.е. фактически осуществляя сдвиг числа, можно увеличить или уменьшить его в 10 раз). Команды ввода и вывода информации для обмена с внешними устройствами. В некоторых ЭВМ внешние устройства являются специальными служебными адресами памяти, поэтому ввод и вывод осуществляется с помощью команд переписи К  оманды управления, реализующие нелинейные алгоритмы. Сюда прежде всего следует отнести условный и безусловный переход, а также команды обращения к подпрограмме (переход с возвратом). Некоторые ЭВМ имеют специальные команды для организации циклов, но это не обязательно: любой цикл может быть сведен к той или иной комбинации условного и безусловного переходов. Система адресации обеспечивает в МП устройствах доступ к операндам, хранящимся в устройствах памяти, внутренних программно- доступных регистрах и внешних устройствах через порты ввода/вывода. Длина формата команды (общее количество бит в коде команды) определяет скорость выполнения команды и зависит от способа адресации операндов. Способы адресации играют большую роль в организации управления ходом выполнения программы, во многом определяют скорость обработки информации. Существуют следующие основные способы адресации: 1. - прямая, 2- косвенная 3 - непосредственная, 4 - автоинкрементная (автодекрементная), 5- страничная, 6- индексная, 7 - относительная Прямая адресация – исполнительный адрес размещается в адресном поле команды. В этом способе непосредственно используется счетчик команд и аккумулятор МП. При прямой адресации содержимое счетчика команд передается на ША и из адресуемой ячейки выбирается очередная команда, поступающая в устройство управления МП. С помощью прямой адресации в АЛУ может вызываться и операнд. Для этого на ША передается адрес ячейки памяти, содержащийся в команде. При необходимости изменения последовательного порядка выполнения программы адресуется ячейка памяти, содержащая адрес условного или безусловного перехода. Команда, содержащая прямой адрес, занимает 2-3 ячейки памяти, что соответственно требует и 2-3 обращений к памяти. Еще одно обращение может потребоваться для непосредственного вызова операнда. С использованием прямой адресации могут быть загружены только аккумулятор и регистры выделенные для хранения косвенного адреса (в МП типа К580, i - 8080 и 8085 это регистровая пара Н). В современных микроконтроллерах для косвенной адресации обычно используется несколько регистровых пар. Преимущества этого способа адресации – простота и наглядность, не требуется вычисление исполнительного адреса. Недостаток – низкая скорость обработки информации, кроме того, во многих микропроцессорных системах для поля адреса в формате команды выделяется небольшое число битов, что ограничивает доступный для данного способа объем адресного пространства памяти. Непосредственная адресация- данные включены в команду и собственно обращения к памяти при этом способе загрузки регистров не требуется. Команда вместо указания адреса операнда содержит этот операнд непосредственно. Непосредственная адресация используется при операциях с константами, исполнение команд с непосредственной адресацией отличается быстротой. Косвенная адресация– адресное поле команды указывает не адрес операнда, а лишь адрес ячейки, в которой хранится косвенный адрес, по которому можно получить операнд. В МП косвенная адресация обычно является неявной регистровой. В этом случае команда предписывает выполнить операцию над операндом, адрес которого содержится в регистрах общего назначения (обычно для этого выделяются определенные регистры блока РОН). Так, команда MOV REG,Mзагружает любой регистр из ячейки памяти, адрес которой содержится в регистровой паре H,L. Команда LDAX загружает аккумулятор с использованием адреса, содержащегося в регистровой паре B или D (используя регистры B или D можно осуществить косвенную загрузку только аккумулятора). Преимущество косвенной адресации в том, что косвенный адрес операнда содержит больше битов, чем число битов в адресном поле команды, т.е. доступен больший объем адресного пространства памяти. Недостатком является увеличение времени для извлечения операнда по сравнению со способом прямой адресации. Относительная индексная адресация (автоинкрементная и автодекрементная) – базовый исполнительный адрес вычисляется так же, как и при регистровой косвенной адресации, а следующие исполнительные адреса получаются увеличением или уменьшением текущего адреса операнда на определенную величину после каждой обработки адреса. Обычно такая адресация используется при обработке массивов данных. В этом случае список данных представляется как совокупность индексных операндов. Операнды с индексами помещаются в соседних ячейках памяти. Для организации доступа к этим ячейкам памяти используются индексные регистры аналогичные в данном случае счетчику команд. Для двумерного массива истинный адрес Страничная адресация– память делится на ряд страниц одинаковой длины. Адресация страниц осуществляется по содержимому программного счетчика или регистра страниц. Адресация памяти внутри страниц производится адресом, который содержится в команде. Относительная адресация– исполнительный адрес получается сложением адресного поля команды с содержимым базового регистра процессора. Это сложение производится в специальном сумматоре. Относительная адресация применяется в командах перехода. |