Адик 3ЛР Э и У ЭВМ. Отчет по лабораторной работе 3 по дисциплине Элементы и узлы эвм

Скачать 179.77 Kb. Скачать 179.77 Kb.

|

|

МИНИСТЕРСТВО НАУКИ И ВЫСШЕГО ОБРАЗОВАНИЯ И РОССИЙСКОЙ ФЕДЕРАЦИИ ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ «МОСКОВСКИЙ АВИАЦИОННЫЙ ИНСТИТУТ (национальный исследовательский университет)» (МАИ) Филиал «ВОСХОД» Кафедра Б21-ВСиТ «Утверждаю» ст. преподаватель __________ Дронов А.А. «_____» _____________2022 г. ОТЧЕТ по лабораторной работе №3 по дисциплине: «Элементы и узлы ЭВМ» на тему: «Синтез комбинационных схем на логических элементах» Выполнили студенты гр. ДВМ 2-74 _______ Бимырза А.К. «_____» _____________2022 г. Байконур 2022 г. Цель работы Реализация различных двоичных функций, заданных таблицей истинности, при помощи логических элементов с потенциальным способом задания информации. 1 Синтез комбинационной схемы на логических элементах Исходные данные указаны в таблице 1. Таблица 1 – Исходные данные

Написать выражение функций в СДНФ: F(Y1) =  1 1 2 2 3+ 3+ 1 1 2 2 3+ 3+ 1 1 2 2 3; 3;F(Y2) =  1 1 2 2 3+ 3+ 1 1 2 2 3+ 3+ 1 1 2 2 3+ 3+ 1 1 2 2 3; 3;F(Y3) =  1 1 2 2 3+ 3+ 1 1 2 2 3+ 3+ 1 1 2 2 3; 3;F(Y4) =  1 1 2 2 3+ 3+ 1 1 2 2 3+ 3+ 1 1 2 2 3+ 3+ 1 1 2 2 3. 3.Провести минимизацию методом карт Карно: f(Y1) =  1 1 3+ 3+ 1 1 2 2

f(Y2) =  1 1 2+ 2+ 1 1 2 2

f(Y3) =  1 1 3+ 3+ 1 1 2 2

f(Y4) =  2 2 3+ 3+ 2 2 3 3

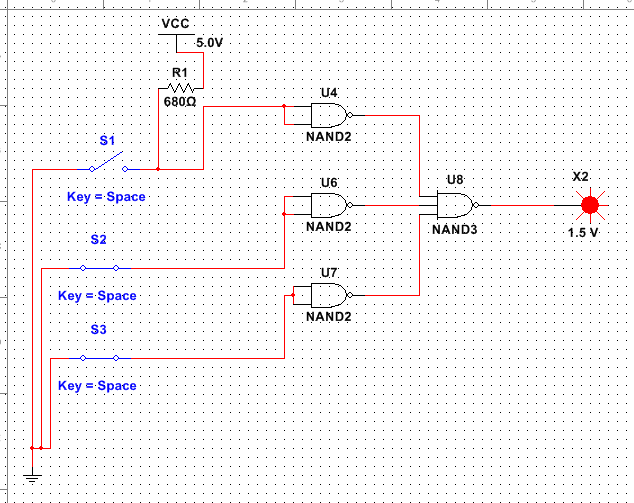

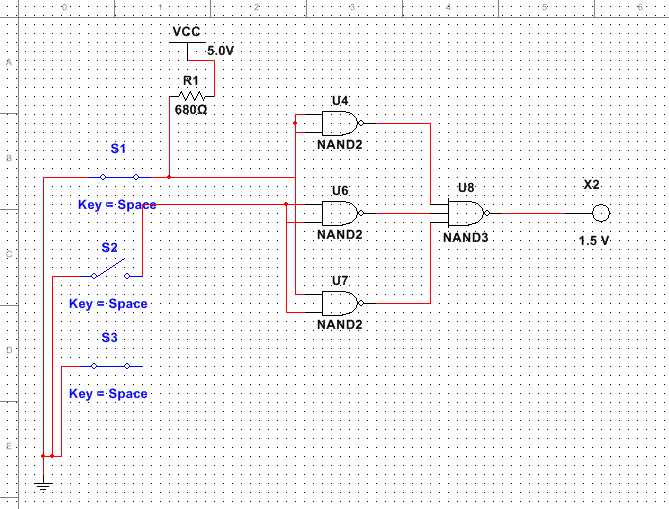

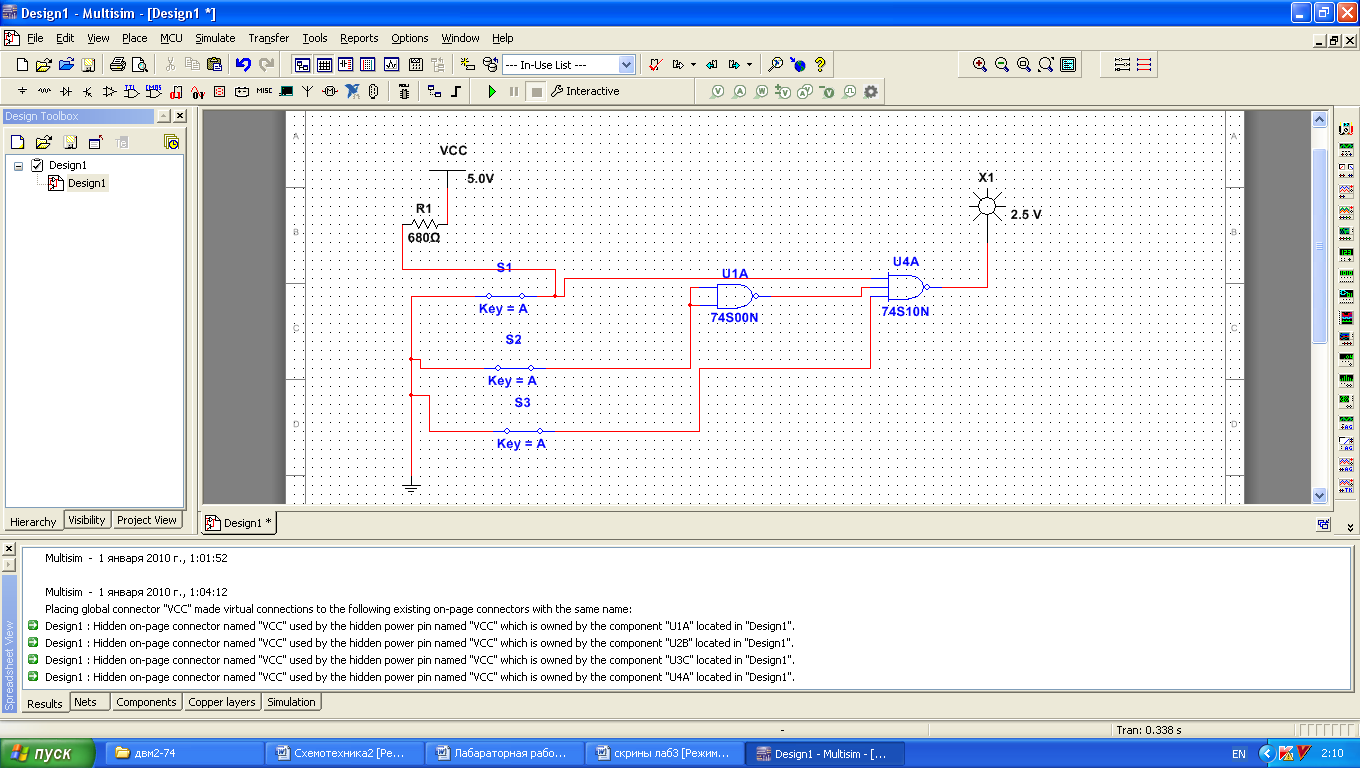

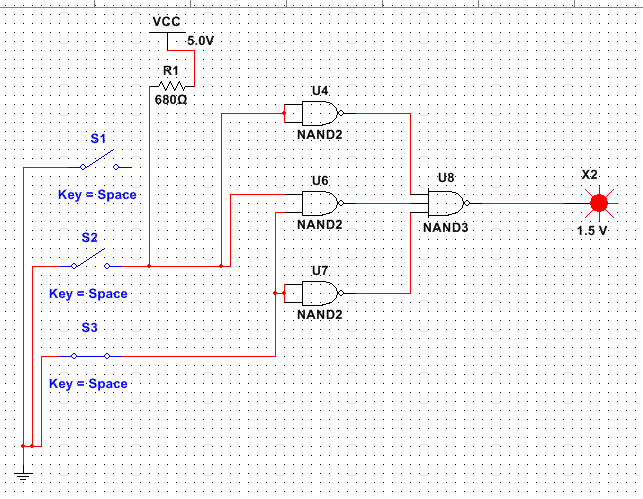

Преобразовать полученную МДНФ логической функции из базиса функций И, ИЛИ, НЕ в базис функций И-НЕ: f(Y1) =  ; ;f(Y2) =  ; ;f(Y3) =  ; ;f(Y4) =  . .Спроектировать схемы на элементах Шеффера, реализующие полученные функции. Заключение В данной лабораторной работе была проведена реализация различных двоичных функций, заданных таблицей истинности, при помощи логических элементов с потенциальным способом задания информации. В Приложении А (рис. А.1-А.2) и Приложении Б (рис. Б.1-Б.2) показаны спроектированные схемы на элементах Шеффера с использованием приложения Electronics Workbench Multisim. Приложение А (Обязательное)  Рисунок А.1 –Схема логическая для Y1  Рисунок А.2 - Схема логическая для Y2 Приложение Б (Обязательное)  Рисунок Б.1 - Схема логическая для Y3  Рисунок Б.2 - Схема логическая для Y4 |