Отчет защищен с оценкой преподаватель ассистент

Скачать 0.85 Mb. Скачать 0.85 Mb.

|

|

ГУАП КАФЕДРА № 42 ОТЧЕТ ЗАЩИЩЕН С ОЦЕНКОЙ ПРЕПОДАВАТЕЛЬ

РАБОТУ ВЫПОЛНИЛ

Санкт-Петербург 2022 Цель работы: приобрести навыки создания, редактирования и компиляции проекта прошивки программируемых логических интегральных схем (ПЛИС) в системе автоматизированного проектирования Quartus Задание: Задание заключается в формировании простейшего проекта, содержащего один логический элемент, количество входов которого не менее трёх и не более шести. Длительность периода сигнала равна величине сетки, которая задаётся равной произведению номера студента в списке группы и 10 нс (например, студент №5 использует величину сетки 50 нс), скважность у всех вариантов равна 50%. Необходимо осуществить проверку его работы, задавая значения входных сигналов: 1. в соответствии с таблицей истинности логического элемента, как на рисунке 23 (длительность одного состояния равна одному такту); 2. как минимум один из сигналов формируется в виде постоянной логической единица (иконка 1 временной диаграммы); 3. как минимум один из сигналов формируется в виде синхросигнала (иконка «часы» временной диаграммы); 4. как минимум один из сигналов формируется случайно (иконка R временной диаграммы). Длительность исследуемого временного интервала (End Time) равна произведению количеству возможных состояний (равное 2n , где n – количество входов логического элемента) на величину сетки. Порядок выполнения работы 1. Согласовать вариант задания с преподавателем во время занятия по расписанию, удостовериться в правильном понимании задания и критериев его оценки. 2. Запустить среду Quartus. Сформировать новый проект в среде Quartus. 3. Построить схему в графическом редакторе. Осуществить компилирование, исправить возможные ошибки. 4. Сформировать данные для временной диаграммы в соответствии с вариантом задания. Осуществить моделирование, убедиться в правильности работы созданного проекта. 5. Сохранить файлы проекта, закрыть проект, выйти из среды Quartus. 6. Вновь запустить среду Quartus. Открыть созданный ранее проект, осуществить компиляцию и моделирование. Убедиться в воспроизводимости полученных ранее результатов. 7. Повторить п. 5. Закончить работу. Схема проекта После создания рабочего проекта, создаем новый файл типа Block Diagram,который содержит описание всей схемы проекта. При помощи команды «Insert» вставляем логический элемент «И» с тремя входами X1,X2,X3 и выводами output.  Рисунок 1 -Соединения в САПР Quartus в виде схемы с логическим элементом И Результаты выполнения работы Рисунок 2-Таблица истинности

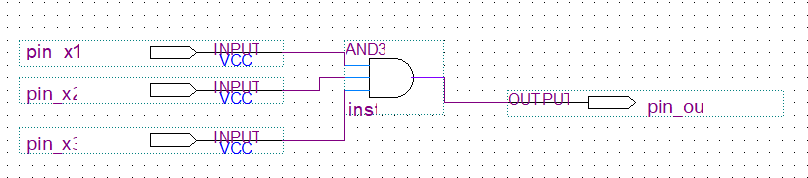

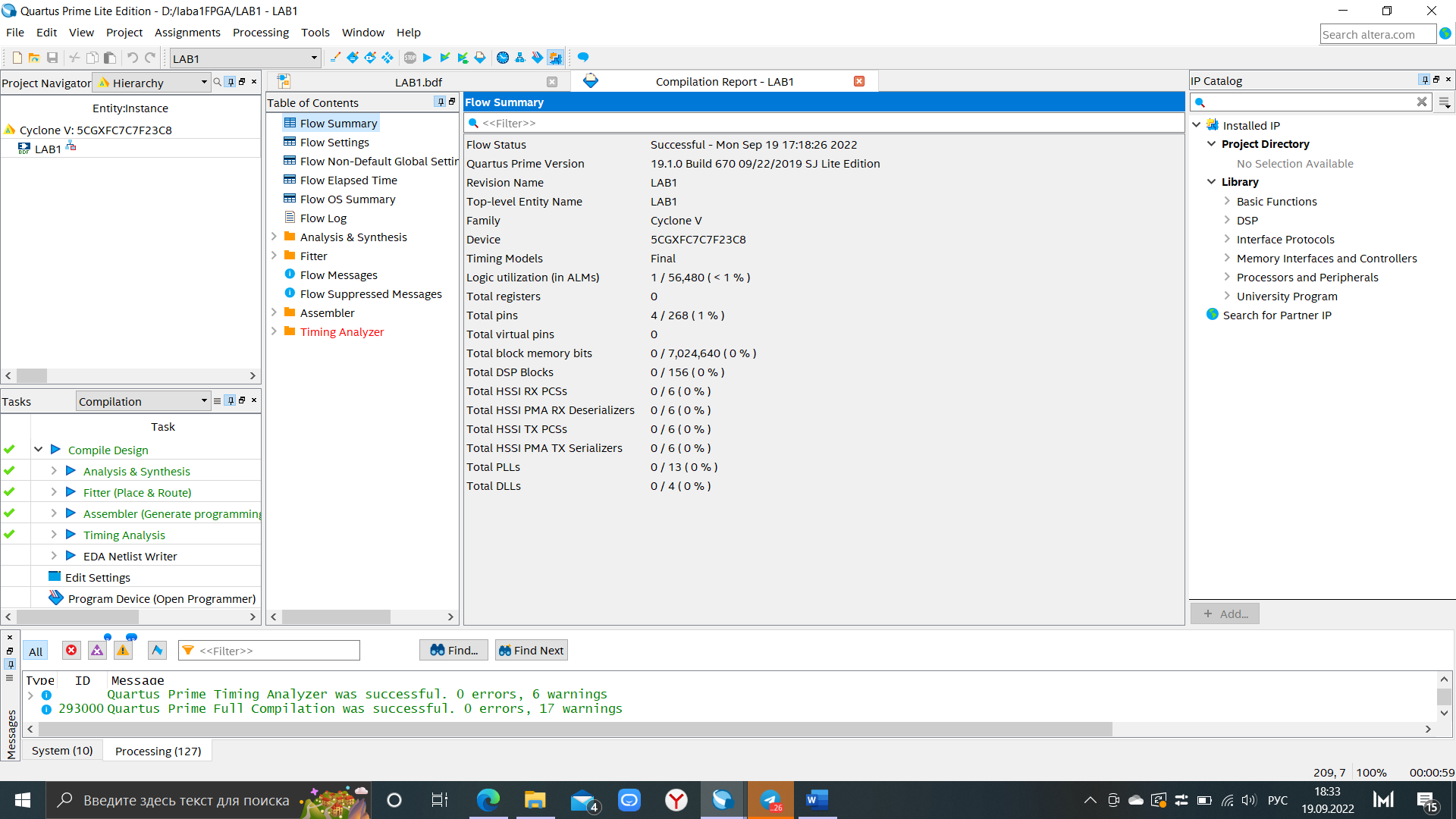

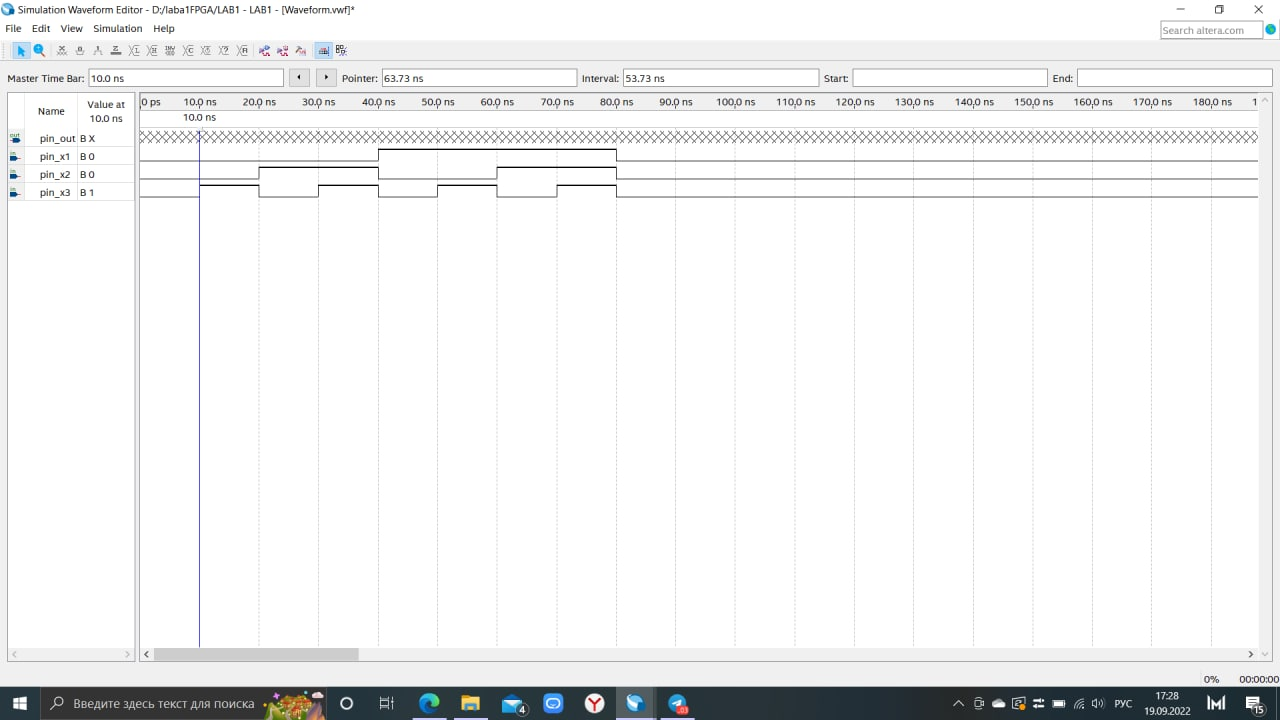

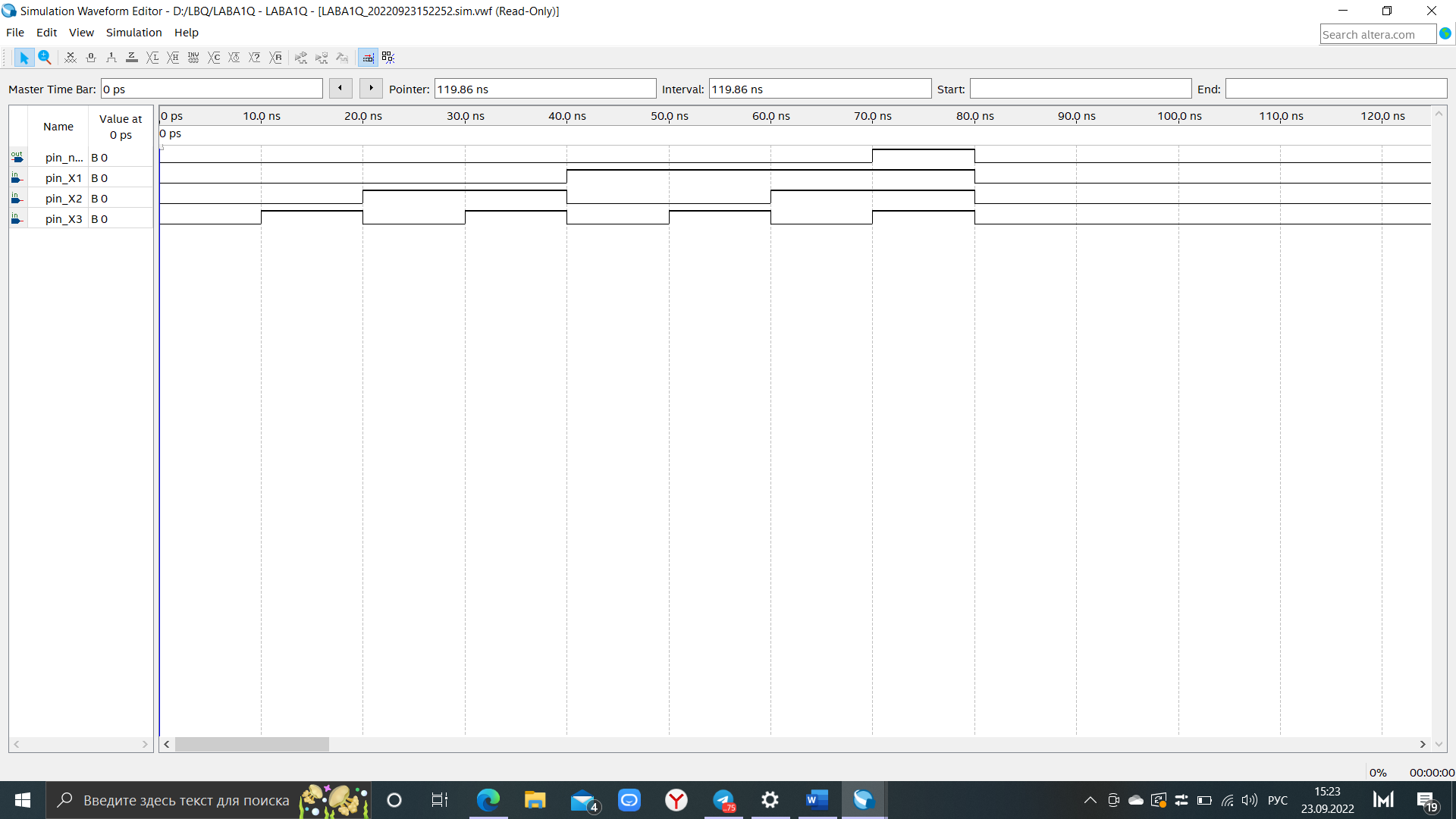

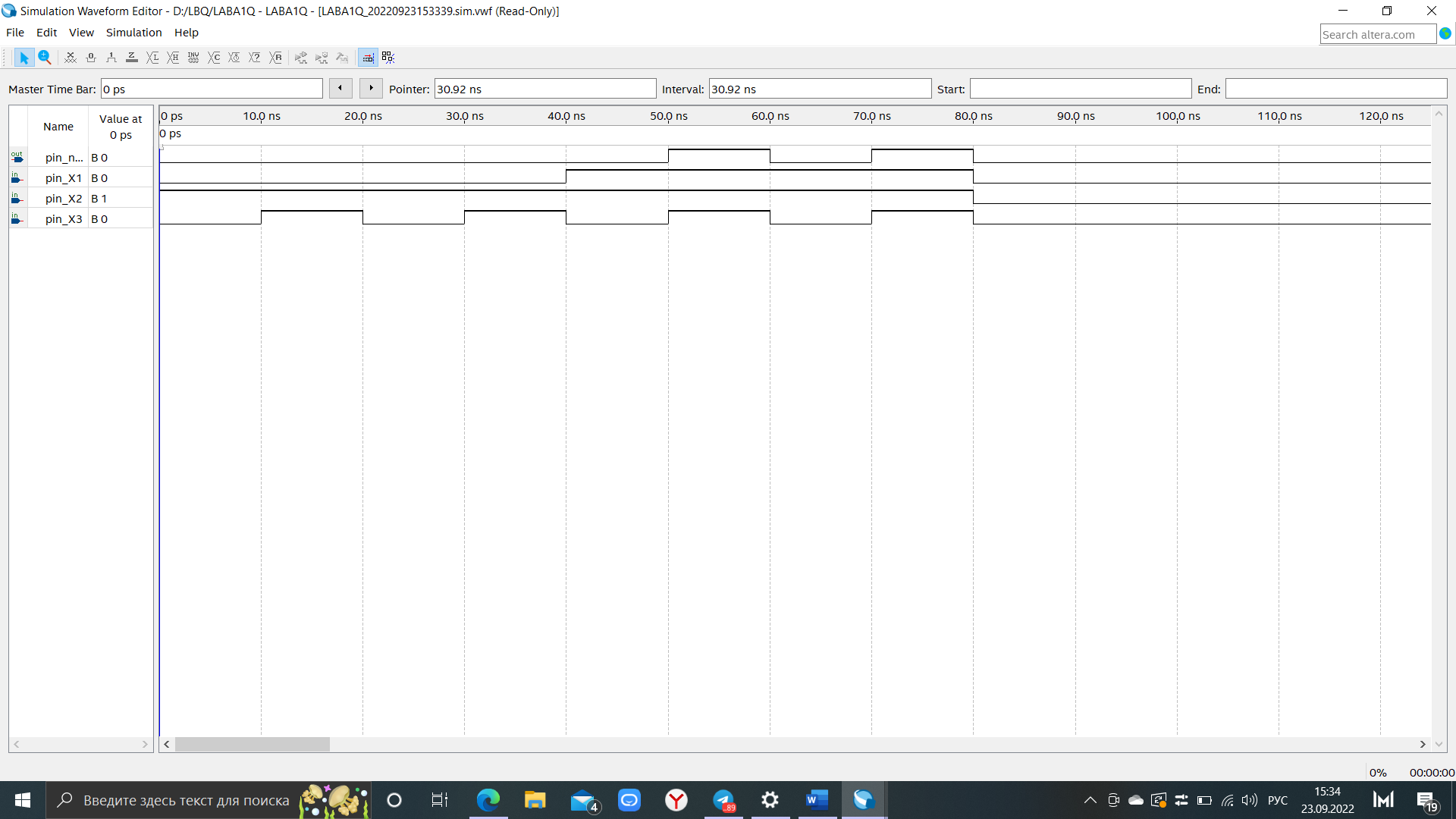

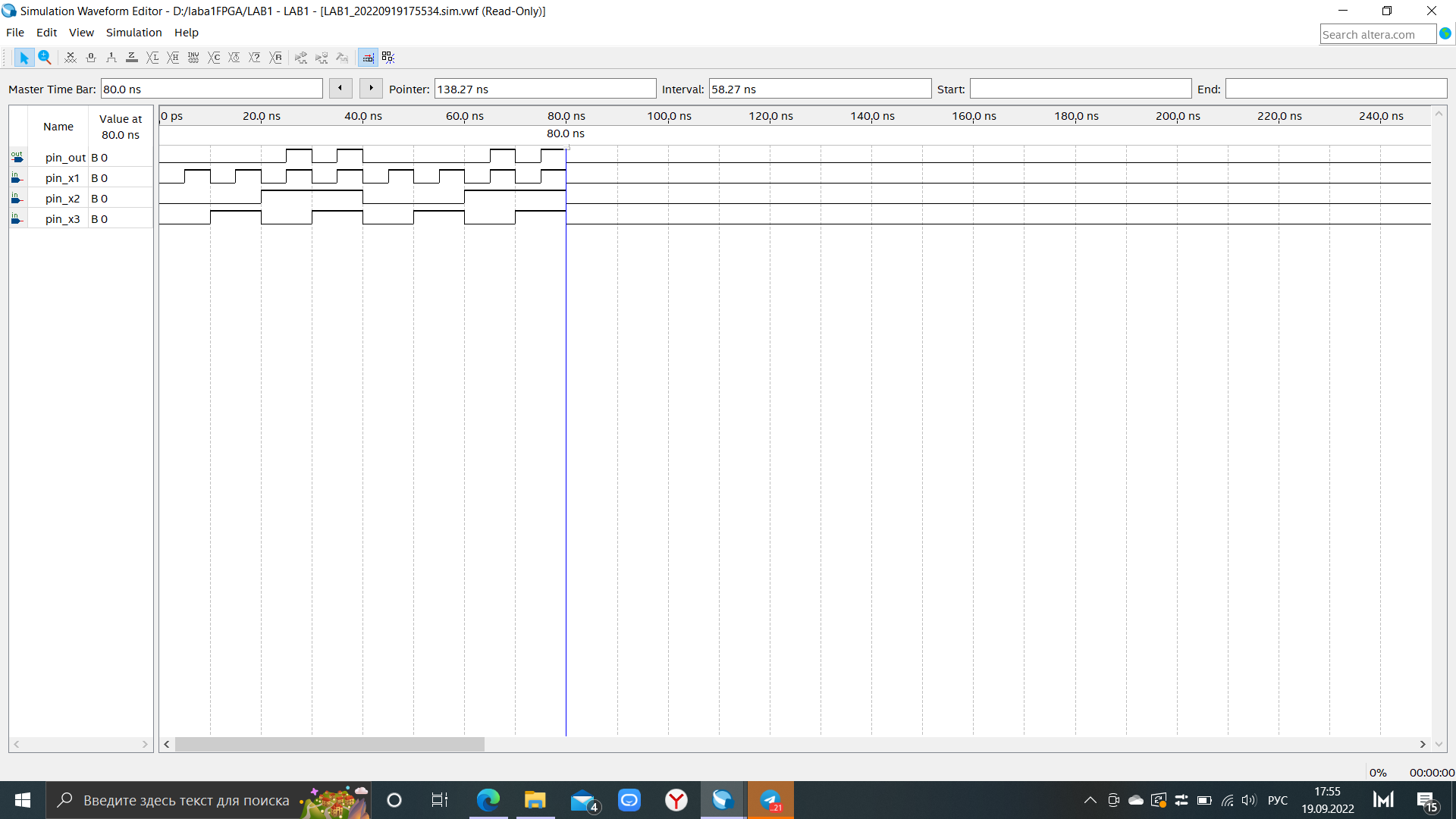

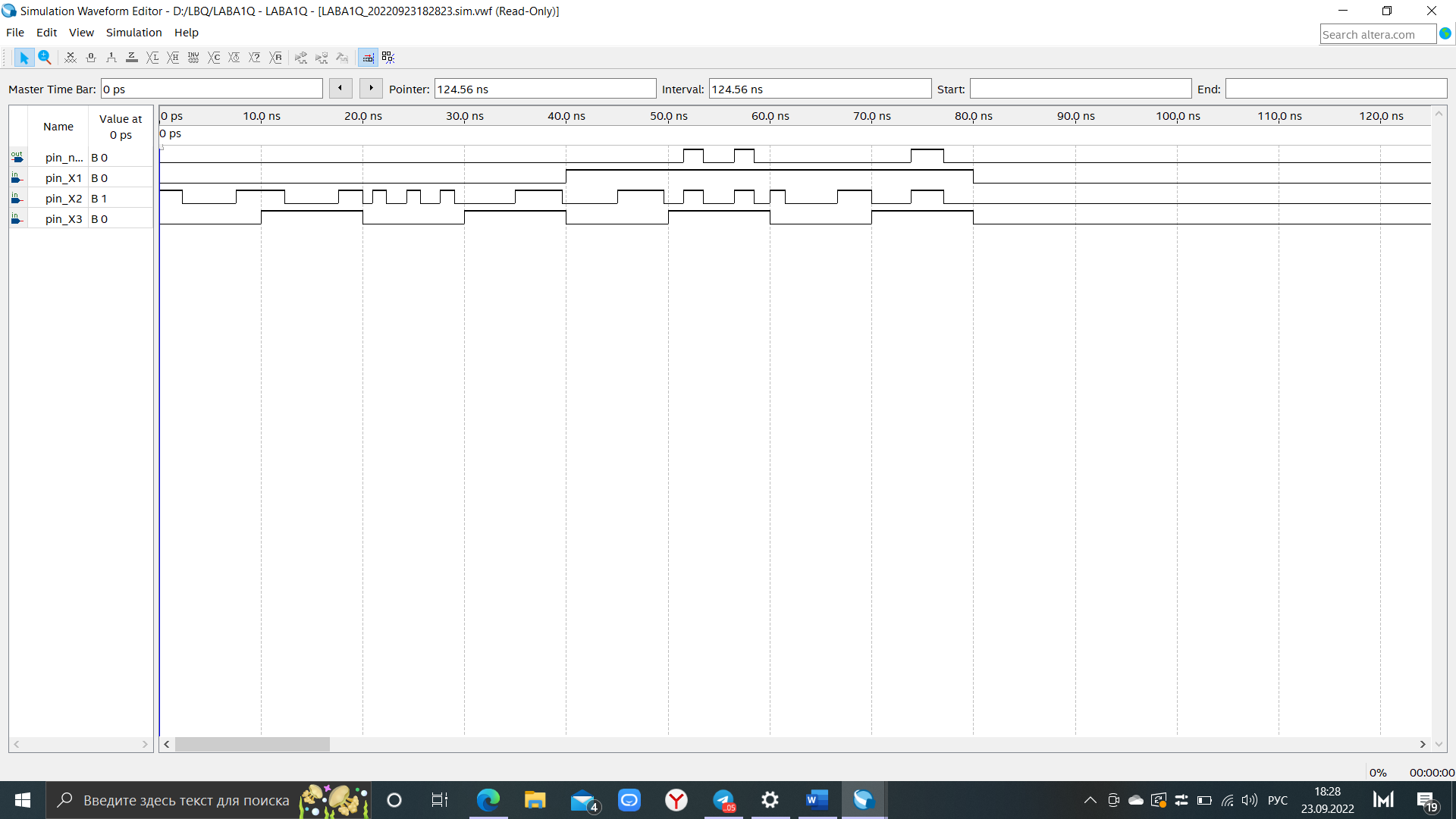

Далее проект был откомпилирован для проведения логической симуляции, результат представлен на рисунке 3.  Рисунок 3 – Сообщение о результатах компиляции На рисунке 4 представлена диаграмма при значениях входных сигналов, соответствующих таблице истинности. Шаг сигнала 10ns.  Рисунок 4 – Начальные данные для временной диаграммы На рисунке 5 представлен результат временной диаграммы при значениях входных сигналов, соответствующих таблице истинности.  Рисунок 5 – Временная диаграмма, соответствующая таблице истинности На рисунке 6 представлена временная диаграмма при постоянном значении, равном логической единице, одного из входных сигналов.  Рисунок 6 - Временная диаграмма при постоянной логической единицы На рисунке 7 представлена временная диаграмма при условии, что один из входных сигналов формируется в виде синхросигнала.  Рисунок 7 – Временная диаграмма при синхросигнале Рисунок 7 – Временная диаграмма при синхросигналеНа рисунке 8 представлена временная диаграмма при условии, что один из входных сигналов формируется в виде случайного сигнала.  Рисунок 8 – Временная диаграмма при случайном сигнале Вывод: В данной лабораторной работе было осуществлено знакомство с программой Quartus. Был создан проект со схемой 3-х входового логического элемента И, рассмотрено поведение элемента на временных диаграммах при различных значениях входных сигналов. Задание было выполнено в соответствии с требованиями лабораторной работы. |