Полупроводниковые диоды. Полупроводниковый диод

Скачать 1.64 Mb. Скачать 1.64 Mb.

|

D-триггерыD-триггеры также называют триггерами задержки(от англ. Delay). D-триггер синхронныцй Пример условного графического обозначения (УГО) D-триггера с динамическим синхронным входом С и с дополнительными асинхронными инверсными входами S и R

D-триггер (D от англ. delay — задержка[10][11][12] либо от data[13] - данные) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. После прихода активного фронта импульса синхронизации на вход С D-триггер открывается. Сохранение информации в D-триггерах происходит после спада импульса синхронизации С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы. D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине. В одноступенчатых D-триггерах во время прозрачности все изменения информации на входе D передаются на выход Q. Там, где это нежелательно, нужно применять двухступенчатые (двухтактные, Master-Slave, MS) D-триггеры. Условное графическое обозначение D-триггера со статическим входом синхронизации С D-триггер двухступенчатыйВ одноступенчатом триггере имеется одна ступень запоминания информации, а в двухступенчатом — две такие ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер обозначают ТТ. Двухступенчатый D – триггер называют триггером с динамическим управлением. Общая схема двухступенчатого триггера T-триггерыТ-триггер (от англ. Toggle - переключатель) часто называют счётным триггером, так как он является простейшим счётчиком до 2. Т-триггер асинхронныйАсинхронный Т-триггер не имеет входа разрешения счёта - Т и переключается по каждому тактовому импульсу на входе С.  Работа схемы асинхронного двухступенчатого T-триггера с парафазным входом на двух парафазных D-триггерах на восьми логических вентилях 2И-НЕ. Слева — входы, справа — выходы. Синий цвет соответствует 0, красный — 1 T-триггер синхронный

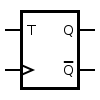

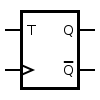

Условное графическое обозначение (УГО) синхронного T-триггера с динамическим входом синхронизации С на схемах. Синхронный Т-триггер[14], при единице на входе Т, по каждому такту на входе С изменяет своё логическое состояние на противоположное, и не изменяет выходное состояние при нуле на входе T. Т-триггер можно построить на JK-триггере, на двухступенчатом (Master-Slave, MS) D-триггере и на двух одноступенчатых D-триггерах и инверторе. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К. В двухступенчатом (Master-Slave, MS) D-триггере инверсный выход Q соединяется со входом D, а на вход С подаются счётные импульсы. В результате триггер при каждом счётном импульсе запоминает значение Q, то есть будет переключаться в противоположное состояние. Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена на 2. T-триггер двухступенчатый со сложной логикойTV-триггер двухступенчатый со сложной логикойJK-триггер JK-триггер с дополнительными асинхронными инверсными входами S и R

JK-триггер[15][16] работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (отангл. Jerk — включение) аналогичен входу S у RS-триггера. Вход K (от англ. Kill — отключение) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации. На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К[17]. Алгоритм функционирования JK-триггера можно представить формулой Условное графическое обозначение JK-триггера со статическим входом С Граф переходов JK-триггера Карта Карно JK-триггера JK-триггер двухступенчатый со сложной логикой

JK-триггер[править | править исходный текст] JK-триггер с дополнительными асинхронными инверсными входами S и R

JK-триггер[15][16] работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (отангл. Jerk — включение) аналогичен входу S у RS-триггера. Вход K (от англ. Kill — отключение) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах, однако это никак не помогает при нарушении правил разработки логических схем. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации. На базе JK-триггера возможно построить D-триггер или Т-триггер. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединив входы J и К[17]. Алгоритм функционирования JK-триггера можно представить формулой Условное графическое обозначение JK-триггера со статическим входом С Граф переходов JK-триггера Карта Карно JK-триггера JK-триггер двухступенчатый со сложной логикой[править | править исходный текст]

D-триггеры[править | править исходный текст]D-триггеры также называют триггерами задержки(от англ. Delay). D-триггер синхронный[править | править исходный текст] Пример условного графического обозначения (УГО) D-триггера с динамическим синхронным входом С и с дополнительными асинхронными инверсными входами S и R

D-триггер (D от англ. delay — задержка[10][11][12] либо от data[13] - данные) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. После прихода активного фронта импульса синхронизации на вход С D-триггер открывается. Сохранение информации в D-триггерах происходит после спада импульса синхронизации С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Рассуждая чисто теоретически, парафазный (двухфазный) D-триггер можно образовать из любых RS- или JK-триггеров, если на их входы одновременно подавать взаимно инверсные сигналы. D-триггер в основном используется для реализации защёлки. Так, например, для снятия 32 бит информации с параллельной шины, берут 32 D-триггера и объединяют их входы синхронизации для управления записью информации в защёлку, а 32 D входа подсоединяют к шине. В одноступенчатых D-триггерах во время прозрачности все изменения информации на входе D передаются на выход Q. Там, где это нежелательно, нужно применять двухступенчатые (двухтактные, Master-Slave, MS) D-триггеры. Условное графическое обозначение D-триггера со статическим входом синхронизации С D-триггер двухступенчатый[править | править исходный текст]В одноступенчатом триггере имеется одна ступень запоминания информации, а в двухступенчатом — две такие ступени. Вначале информация записывается в первую ступень, а затем переписывается во вторую и появляется на выходе. Двухступенчатый триггер обозначают ТТ. Двухступенчатый D – триггер называют триггером с динамическим управлением. Общая схема двухступенчатого триггера T-триггеры[править | править исходный текст]Т-триггер (от англ. Toggle - переключатель) часто называют счётным триггером, так как он является простейшим счётчиком до 2. Т-триггер асинхронный[править | править исходный текст]Асинхронный Т-триггер не имеет входа разрешения счёта - Т и переключается по каждому тактовому импульсу на входе С.  Работа схемы асинхронного двухступенчатого T-триггера с парафазным входом на двух парафазных D-триггерах на восьми логических вентилях 2И-НЕ. Слева — входы, справа — выходы. Синий цвет соответствует 0, красный — 1 T-триггер синхронный[править | править исходный текст]

Условное графическое обозначение (УГО) синхронного T-триггера с динамическим входом синхронизации С на схемах. Синхронный Т-триггер[14], при единице на входе Т, по каждому такту на входе С изменяет своё логическое состояние на противоположное, и не изменяет выходное состояние при нуле на входе T. Т-триггер можно построить на JK-триггере, на двухступенчатом (Master-Slave, MS) D-триггере и на двух одноступенчатых D-триггерах и инверторе. Как можно видеть в таблице истинности JK-триггера, он переходит в инверсное состояние каждый раз при одновременной подаче на входы J и K логической 1. Это свойство позволяет создать на базе JK-триггера Т-триггер, объединяя входы J и К. В двухступенчатом (Master-Slave, MS) D-триггере инверсный выход Q соединяется со входом D, а на вход С подаются счётные импульсы. В результате триггер при каждом счётном импульсе запоминает значение Q, то есть будет переключаться в противоположное состояние. Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена на 2.

RS-триггеры[править | править исходный текст]RS-триггер асинхронный[править | править исходный текст]

Асинхронный RS-триггер с инверсными входами RS-триггер синхронный[править | править исходный текст]

Схема синхронного RS-триггера совпадает со схемой одноступенчатого парафазного (двухфазного) D-триггера, но не наоборот, так как в парафазном (двухфазном) D-триггере не используются комбинации S=0, R=0 и S=1, R=1. Алгоритм функционирования синхронного RS-триггера можно представить формулой где x — неопределённое состояние. Условное графическое обозначение синхронного RS-триггера Схема синхронного RS-триггера на элементах 2И-НЕ Граф переходов синхронного RS-триггера Карта Карно синхронного RS-триггера RS-триггер двухступенчатый со сложной логикой[править | править исходный текст]Рис. 1 Схема RS-триггера двухступенчатого со сложной логикой на элементах 2И-НЕ и 3И-НЕ УГО данного триггера изображено на рис.1. Следует отметить, что на данном рисунке неправильно подается тактовый сигнал (На второй каскад тактовый сигнал должен подаваться с инверсией).

Регистр — устройство, используемое для хранения n-разрядных двоичных данных и выполнения преобразований над ними. Регистр представляет собой упорядоченный набор триггеров, обычно D-, число n которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное[уточнить] цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами. Основой построения регистров являются D-триггеры, RS-триггеры.

Шифратор (кодер) — (англ. encoder) логическое устройство, выполняющее логическую функцию (операцию) — преобразование позиционного n-разрядного кода в m-разрядный двоичный, троичный или k-ичный код. Двоичный шифратор выполняет логическую функцию преобразования унитарного n-ичного однозначного кода в двоичный. При подаче сигнала на один из n входов (обязательно на один, не более) на выходе появляется двоичный код номера активного входа. Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением: где — число входов, — число выходных двоичных разрядов. Троичный шифратор выполняет логическую функцию преобразования унарно n-ичного однозначного (одноединичного или однонулевого) кода в троичный. При подаче сигнала («1» в одноединичном коде или «0» в однонулевом коде) на один из n входов на выходе появляется троичный код номера активного входа. Число входов и выходов в полном троичном шифраторе связано соотношением: , где — число входов, — число выходных троичных разрядов. Число входов и выходов в полном k-ичном шифраторе связано соотношением: , где — число входов, — число выходных k-ичных разрядов, — основание системы счисления. Приоритетный шифратор отличается от шифратора наличием дополнительной логической схемы выделения активного уровня старшего входа для обеспечения условия работоспособности шифратора (только один уровень на входе активный). Уровни сигналов на остальных входах схемой игнорируются.

Устройство электромеханических приборов В аналоговых электромеханических измерительных приборах непосредственной оценки электромагнитная энергия, подведенная к прибору непосредственно из измеряемой цепи, преобразуется в механическую энергию углового перемещения подвижной части относительно неподвижной. Эти приборы относят к приборам прямого действия. Они состоят из электрического преобразователя (измерительной цепи), электромеханического преобразователя (измерительного механизма), отсчетного устройства Измерительная цепь обеспечивает преобразование электрической измеряемой величины X в некоторую промежуточную электрическую величину Y (ток или напряжение), функционально связанную с измеряемой величиной X. Величина Y непосредственно воздействует на измерительный механизм (ИМ). По характеру преобразования измерительная цепь может представлять собой совокупность элементов (резисторов, конденсаторов, выпрямителей, термопар и др.). Различные измерительные цепи позволяют использовать один и тот же ИМ при измерениях разнородных величин, напряжения, тока, сопротивления, меняющихся в широких пределах. Измерительный механизм, являясь основной частью конструкции прибора, преобразует электромагнитную энергию в механическую энергию, необходимую для отклонения его подвижной части относительно неподвижной. У большинства измерительных механизмов перемещение подвижной части состоит в повороте относительно неподвижной на угол б. Отсчетное устройство состоит из указателя и шкалы. Оно преобразует угловое перемещение подвижной части в перемещение указателя l, которое выражается в делениях шкалы. В зависимости от принципа преобразования электромагнитной энергии в механическое угловое перемещение подвижной части измерительного механизма, электромеханические приборы подразделяются на следующие группы (системы): 1) магнитоэлектрические; 2) электромагнитные; 3) электродинамические; 4) ферродинамические; 5) электростатические; 6) индукционные. Устройство и принцип действия электродинамического ИМ Работа измерительных механизмов электродинамической системы (рис. 10а и 10б) основана на взаимодействии магнитных полей двух катушек с токами: неподвижной 1 и подвижной 2. Подвижная катушка, укрепленная на оси или растяжках, может поворачиваться внутри неподвижной. Рис. 10а Рис. 10б При протекании в обмотках катушек токов I1 и I2 возникают электромагнитные силы, стремящиеся так повернуть подвижную часть, чтобы магнитные потоки подвижной и неподвижной катушек совпали. Неподвижная катушка 1 обычно выполняется из двух одинаковых частей, разделенных воздушным зазором. Благодаря этому обеспечиваются требуемая конфигурация магнитного поля и удобство расположения оси. Неподвижная и подвижная катушки механизма (обычно бескаркасные) имеют круглую или прямоугольную форму и изготовляются из медного или алюминиевого провода. Подвижная катушка укрепляется на опорах или растяжках. Для подвода тока к подвижной катушке используются спиральные пружины или растяжки. Применяются стрелочные или световые указатели. Собственное магнитное поле электродинамических механизмов, силовые линии которого замыкаются по воздуху, невелико. Внешнее магнитное поле вызывает появление дополнительного момента от взаимодействия тока в подвижной катушке с потоком этого поля. При работе электродинамического механизма на постоянном токе оказывают влияние постоянные магнитные поля. Если же измерительный механизм применяется в цепи переменного тока, то возникает погрешность от действия переменных магнитных полей той же частоты, что и частота тока в катушках. Для защиты от влияний внешних магнитных полей применяется экранирование, т.е. измерительный механизм помещают внутри одного или двух экранов из ферромагнитного материала. Уравнение преобразования для электродинамического ИМ, работающего на переменном токе имеет следующий вид: где - взаимная индуктивность между катушками; - угол сдвига фаз между токами в катушках. Следовательно, характер шкалы зависит от произведения и производной dM12/dб . Взаимная индуктивность между катушками определяется их формой, размерами и взаимным расположением. При протекании по катушкам постоянных токов уравнение преобразования можно представить в следующем виде: (22) Основными достоинствами электродинамических механизмов являются одинаковые показания на постоянном и переменном токе (при последовательном соединении катушек), что позволяет с большой точностью градуировать их на постоянном токе, а также стабильность показаний во времени. Электродинамические механизмы не содержат ферромагнитных сердечников. Указанные свойства электродинамических механизмов позволяют выпускать на их основе лабораторные многопредельные приборы высоких классов точности 0,5; 0,2; 0,1 для измерений на постоянном и переменном токе. Выпускаются миллиамперметры и амперметры с пределами от 1 мА до 10 А на частоты до 10 кГц, многопредельные вольтметры с пределами от 1,5 В до 600 В на частоты до 5 кГц с током полного отклонения от 60 до 3 мА, многопредельные однофазные ваттметры с пределами по току от 25 мА до 10 А и по напряжению от 15 до 600 В. Недостатки электродинамических механизмов: невысокая чувствительность, большое собственное потребление мощности, чувствительность к перегрузкам.

Мультиплексоры и демультиплексорыВо многих случаях возникает необходимость последовательного опроса логических состояний большого числа переменных и передача их на один выход. Эту функцию выполняет мультиплексор, который коммутирует в желаемом порядке информацию, поступающую с нескольких входных шин на одну выходную. С помощью мультиплексора осуществляется временное разделение информации, поступающей по разным каналам. Мультиплексор имеет две группы входов. Одни входы информационные, другие служат для управления. К последним относятся адресные и разрешающие входы. Если мультиплексор имеет n-адресных входов, то число информационных входов будет 2n. На рис. 3.22 показана принципиальная схема простейшего мультиплексора вида «две линии к одной» (2:1)  Рис. 3.22 В этой схеме используется один внешний сигнал (адрес). Не трудно убедиться в том, что если А = 1, то F = X1, а если А = 0, то F = X2. На этом же принципе строятся и более сложные схемы мультиплексоров. В мультиплексорах на КМДП-структурах коммутирующим элементом служит двунаправленный ключ, поэтому их можно использовать для коммутации и аналоговых сигналов. Демультиплексоры в функциональном отношении противоположны мультиплексорам. Здесь сигналы с одного информационного входа распределяются в желаемой последовательности по нескольким выходам. Выбор нужной выходной шины, как в мультиплексоре обеспечивается кодом на адресных входах. При m адресных входах демодулятор будет иметь 2m выходов. Идею работы демультиплексора поясняет рис. 3.23. Вход Х-информационный, Вход А-адресный. Если А = 1, то F1 = 0, а F2 = 1, если А = 0, то F1 = 1, aF2 = 0. На этом же принципе работают схемы с большим числом выходов. Особенность демультиплексоров на КМОП-структурах, заключается в том, что они могут выполнять функцию мультиплексоров. Такая обратимость естественна, так как основой данных схем является двунаправленный ключ.  Рис. 3.23

Для удобства расчета электрических цепей иногда полезно производить замену источника ЭДС эквивалентным источником тока или выполнять обратную замену источника тока эквивалентным источником ЭДС. Источники ЭДС и тока являются эквивалентными, если они обладают одной и той же внешней характеристикой (или ).

При присоединении к ним приемника с некоторым сопротивлением (или ) напряжение u (или ) и ток i (или ) в приемнике будут в обоих случаях одинаковы. Уравнение внешней характеристики источника ЭДС имеет вид (или ).Запишем это уравнение иначе, а именно: (или). Уравнение внешней характеристики источника тока имеет вид (или). Эти внешние характеристики совпадут, если соблюдать условия и или и . По этим равенствам можно вычислить параметры и ( и ) источника тока, эквивалентного заданному источнику ЭДС, имеющему параметры е и rвн ( и Zвн). Соответственно, из соотношений и или и можно получить параметры источника ЭДС, эквивалентного источнику тока. Эквивалентные замены могут быть произведены и для зависимых источников. Пусть в некоторой ветви pс проводимостью имеется зависимый, управляемый током ветви q источник тока . Согласно вышеприведенным формулам, можно преобразовать управляемый током источник тока в управляемый током источник ЭДС. Значение ЭДС будет равно и внутреннее сопротивление ZBH = Zp = 1/ Yр. Преобразуем две параллельно соединенные ветви, содержащие источники ЭДС и и сопротивления Z1 =1/ Y1и Z2=1/Y2(рис. 2.11), в одну эквивалентную ветвь.  Рис. 2.11. Преобразование двух параллельно соединенных ветвей в одну эквивалентную ветвь Рассматривая параллельно соединенные на рис. 2.11 ветви как источники ЭДС и с внутренними сопротивлениями Z1 и Z2, заменим их эквивалентными источниками тока и с внутренними проводимостями Y1=1/Z1 и Y2=1/Z2 (рис. 2.11). Объединив эти два источника тока в один с внутренней проводимостью Y= Y1+ Y2, перейдем от него к источнику ЭДС с внутренним сопротивлением Распространяя полученный результат на nпараллельно соединенных ветвей, найдем, что заменяющая их эквивалентная ветвь содержит источник ЭДС  и сопротивление

.

Метод эквивалентного генератора — метод преобразования электрических цепей, в котором схемы, состоящие из нескольких ветвей с источниками ЭДС, приводятся к одной ветви с эквивалентным значением. |