Курсовой проект по теме Микропроцессорные устройства управления роботами. Пояснительная записка к курсовой работе по дисциплине Микропроцессорные устройства управления роботов

Скачать 437.1 Kb. Скачать 437.1 Kb.

|

|

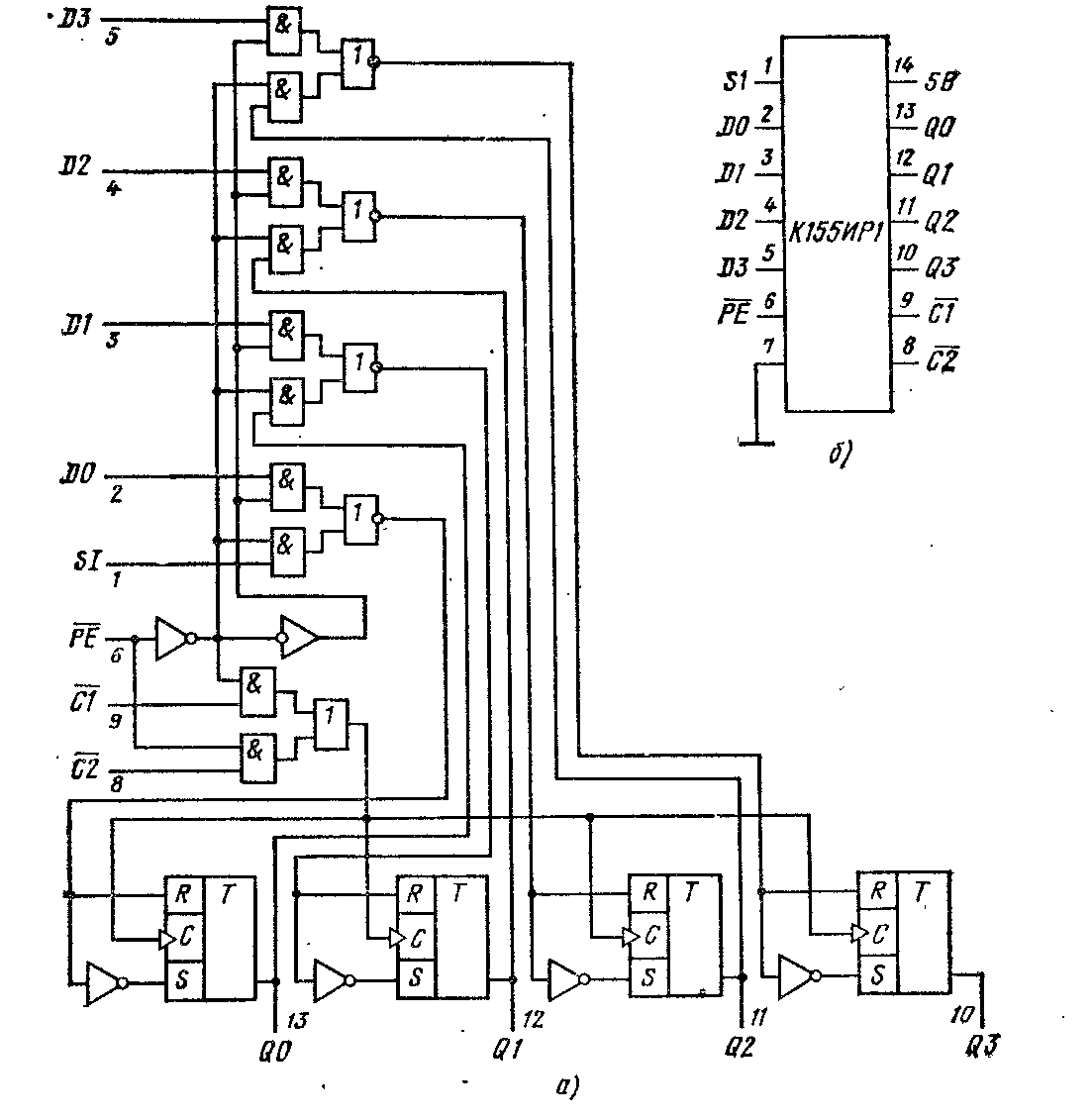

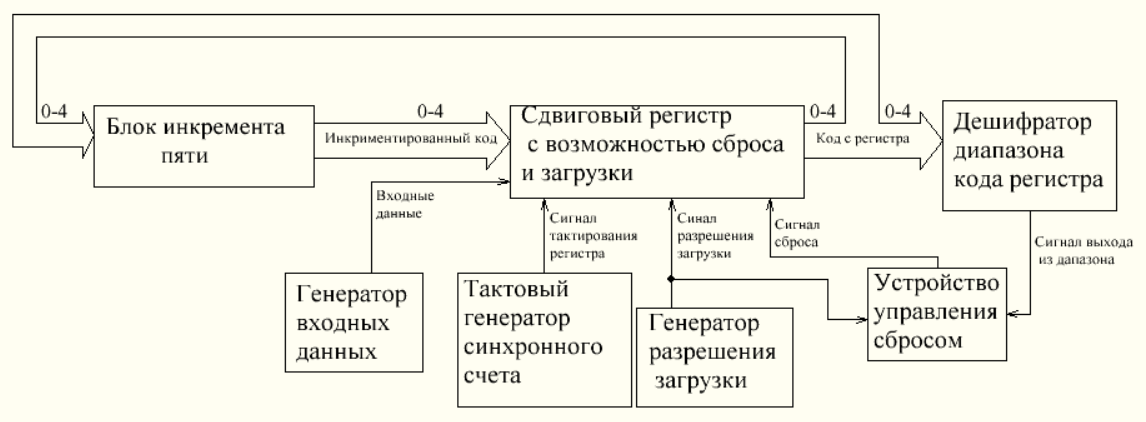

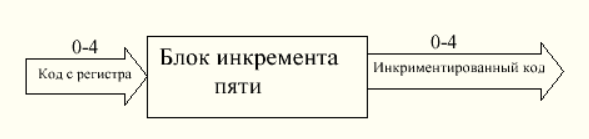

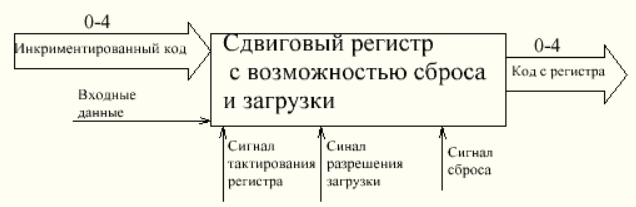

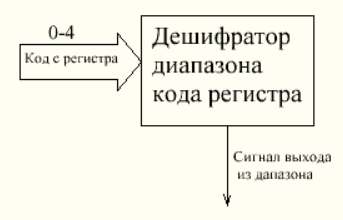

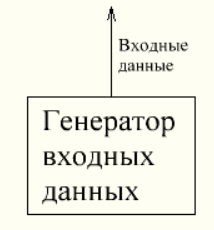

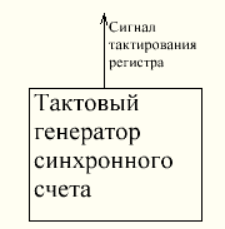

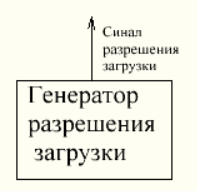

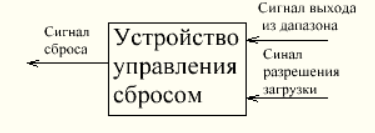

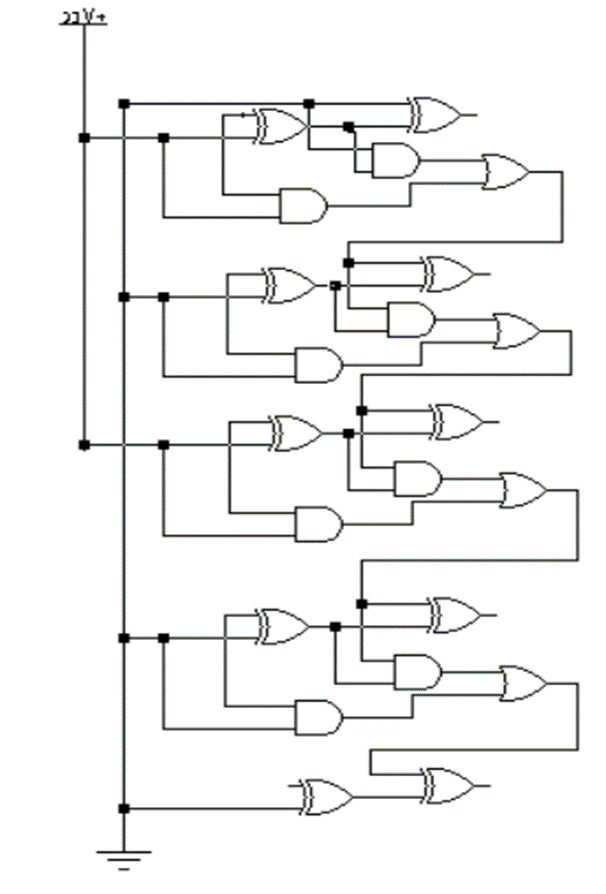

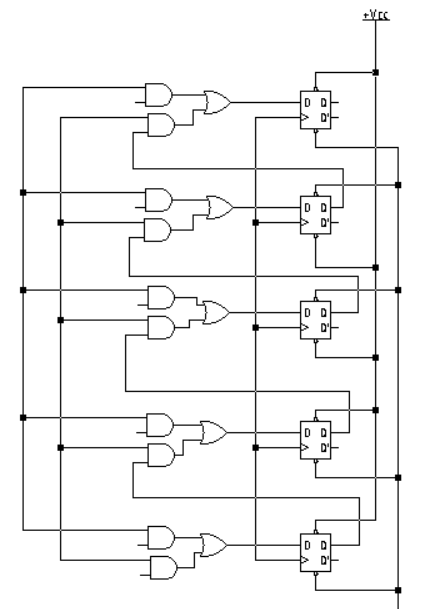

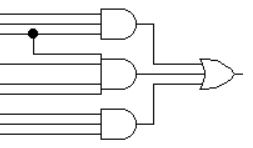

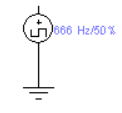

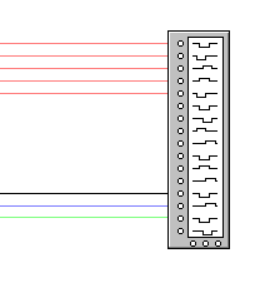

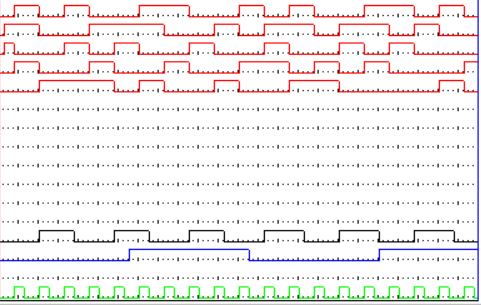

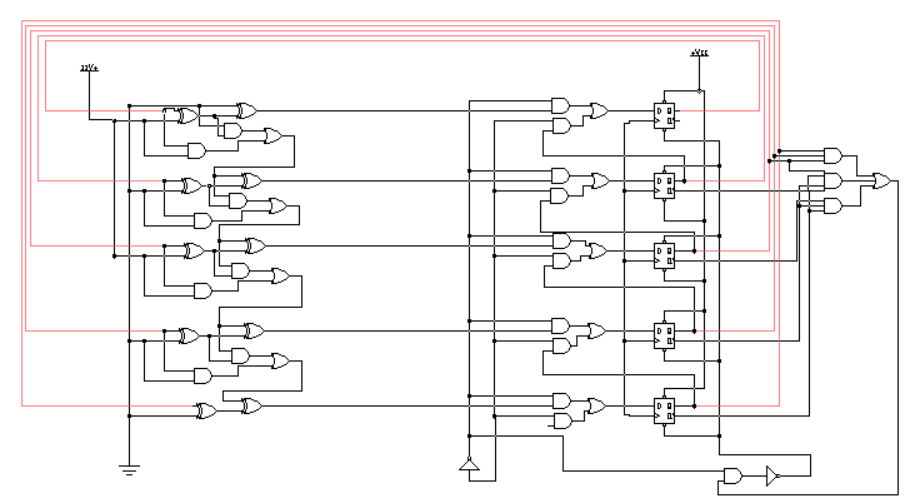

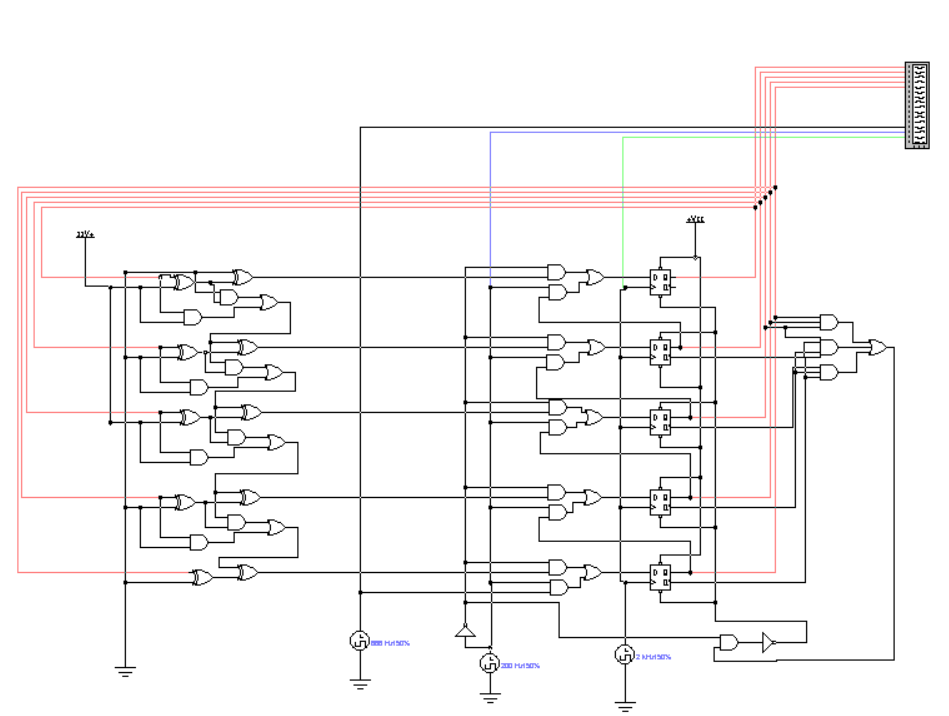

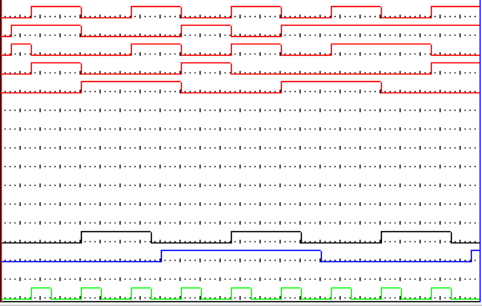

МИНОБРНАУКИ РОССИИ Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования «Тульский государственный университет» Кафедра «Робототехника и автоматизация производства» Пояснительная записка к курсовой работе по дисциплине «Микропроцессорные устройства управления роботов» Выполнил студент группы 623091-ПБ: Божин И.Д Проверил доц., ктн. Зайчиков И.В. Тула 2022 Задание Разработать, смоделировать и протестировать электрическую схему цифрового устройства на элементах «И», «ИЛИ», «ИСКЛЮЧАЮЩЕЕ ИЛИ НЕ», RS и DC-триггерах, выполняющий следующую функцию: счетчик 5 разрядов с последовательной загрузкой слева увеличивающий код на +5 в диапазоне от 6 до 27 со сбросом в 6. СодержаниеВведение 5 1.Описание разрабатываемого цифрового блока 6 1.1.Постановка задачи и анализ возможных вариантов ее функционально-схемной реализации 6 1.2.Общие сведения и электрическая схема стандартных базовых цифровых элементов 6 1.3.Функциональное назначение разрабатываемого блока 8 1.4.Описание функциональной схемы цифрового блока с применением элементарных цифровых элементов булевой алгебры 9 1.4.1 Блок инкремента пяти 9 1.4.2 Сдвиговый регистр с возможностью загрузки и сброса 10 1.4.3 Дешифратор диапазона кода регистра 10 1.4.4 Генератор входных данных 11 1.4.5 Тактовый генератор синхронного счета 11 1.4.6 Генератор разрешения загрузки 11 1.4.7 Устройство управления сбросом 12 1.5 Описание электрической схемы разрабатываемого цифрового блока и отличий от базовой реализации 12 1.5.1 Блок инкремента пяти 12 1.5.2 Сдвиговый регистр с возможностью сброса и загрузки 13 1.5.3 Дешифратор диапазона кода регистра 14 1.5.4 Устройство управления сбросом 15 1.6.Описание тестовой электрической схемы разрабатываемого цифрового блока для моделирования 16 1.6.1 Генератор входных данных 16 1.6.2 Тактовый генератор синхронного счета 16 1.6.3 Генератор разрешения загрузки 16 1.6.4 Логический анализатор 17 1.7.Описание диаграмм сигналов цифрового блока по результатам тестового моделирования 18 19 Заключение 20 Приложение1 22 Приложение2 23 Приложение3 24 ВведениеЦелью курсовой работы является овладение основными навыками анализа и применения основных дискретных элементов цифровой комбинационной схемотехники при создании устройств, решающих задачу преобразования информации различного назначения и применяемых в микропроцессорных системах с вычислителями. В процессе выполнения курсовой решается комплекс задач, результатом которых является ознакомление с внутренней функциональной схемой и реализацией узлов цифровой логики, возможностями применения элементов в цифровых схемах и разработка схемного решения для заданного узла, позволяющего правильно выполнять поставленные задачи и выполнять информационно-преобразовательные операции в соответствии с алгоритмом функционирования разрабатываемого блока. 1.Описание разрабатываемого цифрового блока1.1.Постановка задачи и анализ возможных вариантов ее функционально-схемной реализацииРазрабатываемый цифровой блок должен работать по следующему принципу: в устройство записывается некоторый код по последовательному входу, этот код увеличивается на 5 до тех пор пока оно входит в диапазон допустимых значений. Если в регистр записан код, выходящий за пределы диапазона, регистр сбрасывается, с предустановкой на нём числа 6. Далее происходит счёт с инкрементом 5, начиная от числа шесть, пока в устройство не будет записано новое число. Устройство должно иметь два режима работы. В первом режиме происходит последовательная загрузка данных в устройство с внешнего устройства. Во втором режиме происходит инкремент пяти кода загруженного в устройство. Для реализации последовательной загрузки данных следует использовать сдвиговый регистр. Инкремент пяти можно реализовать на сумматоре, на первую группу входов которого поступают данные с регистра, а входы второй группы подключены к земле и источнику постоянного тока таким образом, чтобы на них постоянно подавалось число пять. Для переключения режимов работы, на синхронные входы триггеров, составляющих регистр можно поставить мультиплексоры. Управление сменой режимов будет производиться по сигналу с внешнего генератора. Распознавание выхода кода на регистре из диапазона допустимых значений можно выполнить посредством дешифратора. Чтобы исключить возможность сброса регистра во время передачи, сигнал с дешифратора должен блокироваться до окончания передачи. Такую блокировку можно выполнить с помощью элемента «И», на один вход которого поступает сигнал с дешифратора, а на другой инвертированный сигнал с генератора разрешения загрузки. 1.2.Общие сведения и электрическая схема стандартных базовых цифровых элементовПрототипом принимаем 4-разрядный сдвиговый регистр К155ИР1. Он имеет последовательный вход данных S1(вывод 1), четыре параллельных входа D0-D3(выводы 2-5), а также четыре выхода Q0-Q3(выводы 13-10) от каждого из триггеров. Регистр имеет два тактовых входа C1 и С2. От любого из пяти входов данных код поступит на выходы синхронно с отрицательным перепадом, поданным на выбранный тактовый вход. Вход разрешения параллельной загрузки PE служит для выбора режима работы регистра. Если на вход PE даётся напряжение высокого уровня, разрешается работа тактовому входу С2. В момент прихода на этот вход отрицательного перепада тактового импульса в регистр загружаются данные от параллельных входов D0-D3. Если на вход PE подано напряжение низкого уровня, разрешается работа тактовому входу С1. Отрицательные фронты последовательности тактовых импульсов сдвигают данные от последовательного входа S1 на выход Q0, затем на Q1, Q2 и Q3, т.е. вправо. Сдвиг данных по регистру влево получится, если соединить выход Q3 и вход D2, Q2 и D1, Q1 и D0. Регистр надо перевести в параллельный режим, подав на вход PE напряжение высокого уровня. Напряжение на входе PE модно менять только, если на обоих тактовых входах уровни низкие. Однако, если на входе С1 напряжение низкого уровня, перемена сигнала на входе PE от низкого уровня к высокому не меняет состояния выходов.  Рис. 1.2.1. Регистр К155ИР1(а) и его цоколевка(б) 1.3.Функциональное назначение разрабатываемого блокаДанное устройство предназначено для операции инкремента, выходной код увеличивается на константу в размере 5. Оно работает в заданном диапазоне работы, за который она не может заходить. В устройство наблюдается 2 режима работы: синхронный счет, синхронная последовательная загрузка с внешнего устройства и сброс в заданную константу. Для данных режимов определяется соответственно от низшего к высшему. Среди 2 режимов самым большой приоритет имеет сброс устройства, то есть если выполняется сброс блокируется другой режима. Принцип работы разрабатываемого цифрового устройства состоит в следующем. С выхода регистра пятиразрядный код приходит на дешифратор, который проверяет входит ли данное число в диапазон или нет. Если код удовлетворяет условиям дешифратора то он переходит в сумматор, который к результирующему коду инкрементирует 5, который передает на входы триггеров новый код и при перепаде с низкого на высокий уровень записывает его в регистр. При выходе из диапазона дешифратор подает сигнал на сброс и регистр сбрасывается в заданное значение. Поскольку константа является началом диапазона, он продолжает свою работу. По сигналу разрешения происходит последовательная загрузка с сдвигового регистра в регистр, этот код загружается с внешнего устройства. 1.4.Описание функциональной схемы цифрового блока с применением элементарных цифровых элементов булевой алгебры Рисунок 1.4.1 Функциональная схема разрабатываемого цифрового блока При низком уровне генератора разрешения загрузки, входные данные последовательно загружаются в регистр. При высоком уровне генератора разрешения загрузки, путём подачи шины выходных данных на блок инкремента пяти, формируется код на 5 больше предыдущего и подаётся на входы регистра. За счёт это выполняется операция счёта плюс 5. Дешифратор проверяет шину выходящую с регистра на наличие запрещённых кодов, дешифрировав такой код на его выходе появляется высокий уровень, поступающий на устройство управлением сброса. При низком уровне, поступающем с генератора разрешения загрузки, устройство управлением сбросом формирует на своем выходе низкий уровень, который сбрасывает состояние регистра в 6. 1.4.1 Блок инкремента пятиБлок инкремента пяти выполняет операцию инкремента пяти над кодом поступившим с регистра, на выходе выдаёт результат суммы в виде инкрементирующего кода.  Рисунок 1.4.2 Блок инкремента пяти 1.4.2 Сдвиговый регистр с возможностью загрузки и сбросаПредназначен для вывода конечных данных работы схемы. При высоком уровне сигнала разрешения загрузки, производится последовательная загрузка кода с генератора входных данных и вывод его. При низком уровне сигнала разрешения загрузки по фронту сигнала тактирования регистра производится вывод кода из Сдвигового регистра.  Рисунок 1.4.3 Сдвиговый регистр с возможностью сброса и загрузки 1.4.3 Дешифратор диапазона кода регистраДешифратор диапазон кода регистра, настроен на распознавание запрещённых кодов не входящих в диапазон от 6 до 27. При распознании такого кода на выходе дешифратора появляется высокий уровень.  Рисунок 1.4.4 Дешифратор диапазона кода регистра 1.4.4 Генератор входных данныхГенератор входных данных имитирует подачу последовательного входного кода с внешнего устройства.  Рисунок 1.4.5 Генератор входных данных 1.4.5 Тактовый генератор синхронного счетаТактовый генератор синхронного счета выдаёт стробирующий сигнал, по которому происходит запись данных с блока инкремента пяти или сдвиг вправо.  Рисунок 1.4.6 Тактовый генератор синхронного счета 1.4.6 Генератор разрешения загрузкиГенератор разрешения загрузки переключает режимы работы регистра. При низком уровне загрузка разрешена c сумматора. При высоком загрузка запрещена и реализуется сдвиг вправо.  Рисунок 1.4.7 Генератор разрешения загрузки 1.4.7 Устройство управления сбросомПри одновременном поступление высокого уровня с дешифратора и с низкого уровня генератора разрешения загрузки на выходе устройства формируется низкий уровень приводящий к сбросу.  Рисунок 1.4.8 Устройство управления сбросом 1.5 Описание электрической схемы разрабатываемого цифрового блока и отличий от базовой реализацииЭлектрическая схема разрабатываемого цифрового блока вынесена в приложение 1. 1.5.1 Блок инкремента пятиСхема блока инкремента пяти получена на базе пятиразрядного сумматора. Сумматор построен на элементах «И», «ИЛИ», «Исключающее ИЛИ». На первую группу входов сумматора подаётся код с регистра. Вторая группа входов запитана следующим образом: первый и третий разряды запитаны на источник постоянного тока, остальные разряды подключены к земле. Такое подключение обеспечивает инкремент пяти входящего кода.  Рисунок 1.5.1 Блок инкрементации пяти 1.5.2 Сдвиговый регистр с возможностью сброса и загрузкиСдвиговый регистр с возможностью сброса и загрузки собран на RSDC-триггерах, «И», «ИЛИ». Регистр состоит из 5 RSDC-триггерах и мультиплексора состоящий из двух «И» и одного объединяющего «ИЛИ». На триггерах выполнена предустановка в 6 с помощью выходов триггера –«SET» и «RESET». При подаче сигнала высокого уровня с генератора разрешения загрузки устанавливается режим последовательной загрузки данных с внешнего устройства, которые подаются на входы и выводятся на выход регистра. При подаче сигнала низкого уровня устанавливается режим загрузки с блока инкремента пяти в сдвиговый регистр с возможностью сброса и загрузки.  Рисунок 1.5.2 Сдвиговый регистр с возможностью сброса и загрузки 1.5.3 Дешифратор диапазона кода регистраДешифратор диапазона кода регистра построен на базе трёх элементов «И» и одного элемента «ИЛИ». Код с регистра параллельно поступает на входы элементов «И», выходы которых в свою очередь соединены с входами элемента «ИЛИ». Первая группа запрещённых кодов от 28 до 31 распознаётся с помощью подачи прямого сигнала 4,3 и 2 разряда на элемент «И». Вторая группа запрещённых кодов состоит из 4 и 5 распознаётся с помощью подачи инверсного сигнала 1, 3 и 4 и прямого сигнала 2 разряда на элемент «И». Третья группа запрещённых кодов от 0 до 3 и распознаётся с помощью подачи инверсного сигнала 2,3 и 4 разряда на элемент «И». Дешифратор распознаёт коды шины выходных данных Q0..Q4. Таблица 1.5.1

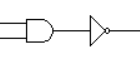

Рисунок 1.5.3 Дешифратор диапазона кода регистра 1.5.4 Устройство управления сбросомУстройство управление сбросом представляет собой элемент «И» с инвертированным выходом. На один вход приходит сигнал с дешифратора, на второй вход поступает инвертированный сигнал с генератора разрешения загрузки. Таким образом, на выходе устройства формируется низкий уровень при одновременном поступлении на вход высокого уровня с дешифратора и низкого уровня с генератора разрешения загрузки.  Рисунок 1.5.4 Устройство управления сбросом 1.6.Описание тестовой электрической схемы разрабатываемого цифрового блока для моделированияТестовая электрическая схемы разрабатываемого цифрового блока для моделирования вынесена в приложение 2 1.6.1 Генератор входных данныхГенератор входных данных имитирует подачу последовательного входного кода с внешнего устройства. Он подаёт сигнал с частотой 666 Гц и скважностью 50%.  Рисунок 1.6.1 Генератор входных данных 1.6.2 Тактовый генератор синхронного счетаДанный генератор выдаёт тактовый сигнал, по которому регистр производит запись по параллельным и последовательным входам. Характеристики этого генератора таковы: частота 2000 Гц, скважность 50%.  Рисунок 1.6.2 Тактовый генератор синхронного счета 1.6.3 Генератор разрешения загрузкиСигнал с генератора разрешения загрузки переключает режимы работы сдвигового регистра. При высоком уровне разрешается последовательная загрузка данных с внешнего устройства и реализуется сдвиг вправо. При низком уровне от генератора происходит инкремент пяти кода находящегося в регистре. Характеристики этого генератора таковы: частота 321 Гц, скважность 50%  Рисунок 1.6.3 Генератор разрешения загрузки 1.6.4 Логический анализаторЛогический анализатор – инструмент, позволяющий отобразить временные диаграммы сигналов смоделированной схемы. На входы анализатора поступают сигналы с выходов сдвигового регистра, сигнал с тактового генератора, сигнал с генератора разрешения загрузки и сигнал с генератора входных данных.  Рисунок 1.6.4 Логический анализатор 1.7.Описание диаграмм сигналов цифрового блока по результатам тестового моделирования Рисунок 1.7.1 Диаграмма Первые пять сигналов – выходные сигналы со сдвигового регистра Шестой сигнал – сигнал генератора входных данных Седьмой сигнал – сигнал разрешения загрузки с генератора входных данных Восьмой сигнал – сигнал тактового генератора синхронного счета Изучив временную диаграмму сигналов в схеме, можно увидеть, что по фронтам тактового сигнала происходит изменение содержимого сдвигового регистра. При низком уровне сигнала разрешения загрузки происходит операция инкремента пяти содержимого регистра. При высоком уровне в сдвиговый регистр происходит последовательная загрузка кода с генератора входных данных. В момент образования на выходах регистра кода, выходящего за пределы диапазона допустимых значений, при низком уровне сигнала от генератора разрешения загрузки происходит немедленный сброс содержимого регистра в шесть. ЗаключениеВ данной курсовой работе разработана, смоделирована и протестирована принципиальная схема сумматора, который суммирует два пятиразрядных сигнала и выдаёт их сумму. Моделирование схемы с помощью «Electronics Workbench v5.12» показало работоспособность разработанной схемы. Задание, поставленное в курсовой работе, выполнено. В ходе выполнения курсовой работы получены практические навыки применения знаний по курсу Микропроцессорные устройства управления роботов. Список используемой литературы: 1. В. Л. Шило, «Популярные цифровые микросхемы», 2-е издание, Москва: Радио и связь, 1989 год – 352 стр. Приложение1 Рисунок 2.1 Электрическая схема разрабатываемого цифрового блока Приложение2 Рисунок 2.2 Тестовая электрическая схемы разрабатываемого цифрового блока для моделирования Приложение3 Рисунок 2.3 Диаграмма сигналов цифрового блока |