1.2 Формат данных 1.2 Формат данных

Эмулируемая ЭВМ оперирует над данными, представленными в двухосновных форматах 16 – разрядное слово и 8 – разрядный байт. Данныерассматриваютсякакцелыечисла,старшийразряд–знаковый,отрицательные числа представляются в дополнительном коде. Диапазонпредставлениячисел:

-слово(-32768-32767);

-байт(-128-127)

7

Структура базовой микроЭВМ Структура базовой микроЭВМ

Для реализации процессора – с заданной системой командпредполагаетсяиспользоватьвкачествебазовоймикроЭВМсразрядно-модульнойорганизациинаБИСсерииК1804,построеннуюпотиповойсхеме.ПрограммнаямодельтакоймикроЭВМвключенавучебнуюкросс-системупроектирования микропроцессорныхустройств. В состав процессорабазовоймикроЭВМвходятследующиеблоки:блокмикропрограммногоуправления(БМУ),блокобработкиданных(БОД)иинтерфейсныйблок(ИБ).БМУслужитдлягенерациикодовмикрокоманд,содержащихполя

М1…М15идляуправляющихработойБОДиИБ.БОДосуществляетобработкуинформацииподуправлениемполейМ1,М5…М14,вырабатываемых в БМУ кодов микрокоманд. По результатам выполненияоперацийвБОДформируетсясловосостоянияпроцессораPSW,поступавшее в БМУ. Информация в БМУ и БОД поступает из ИБ по шинеданных BI, а с выхода БОД в ИБ поступают данные по шине ВO и адрес пошине ADR. Поле М15, код которого поступает из БМУ в ИБ, служит дляуправлениявводом-выводом,приэтомосуществляетсяанализFLG,вырабатываемыхвИБ.

8

Функциональная схема БОД. Функциональная схема БОД.

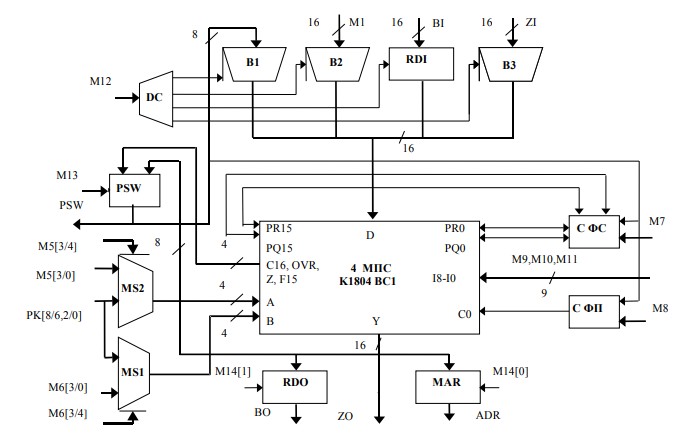

Нарисунке4представленафункциональнаясхемаБОД.ВсоставБОДвходятобрабатывающийузел(ОУ),вентилиВ1иВ2,входнойрегистрданныхRDI,схемаформированияпереноса(СФП)–С0вмладшийразряд,регистрсостоянийPSW,выходнойрегистрданныхRDO,регистрадресаMAR, мультиплексоры адреса MSA и MSB, дешифратор DC.ОбрабатывающийузелвыполненнамикросхемахК1804BCIиможетвыполнятьвсеарифметическиеилогическиеоперации,предусмотренныевданноймикросхеме.Выполняемаяоперациязадаетсядевятиразряднымкодом18-10,которыйобразуетсякодамиМ9,М10,М11.АдресаАиВрегистров во внутреннем регистровом ЗУ операционного блока ОУзадаютсясоответственнокодамиМ5иМ6,приэтомнавходыАиВмогутпоступатькаккодыМ5иМ6,такиразряды8…6или2…0регистракоманд.НавходDоперационногоузламожетподаватьсяинформациясвентилей В1, В2 и регистра RDI, подключение которых к шине DуправляетсякодомМ12.СвыходаYинформацияможетзаноситсявRD0

иливMAR в соответствиис заданнымкодом М14.

Рисунок4.ФункциональнаясхемаБОД

9

|

Скачать 2.21 Mb.

Скачать 2.21 Mb.