|

|

ПОЯСНИТЕЛЬНАЯ ЗАПИСКА к курсовому проектированию по дисциплине «ЭВМ и периферийные устройства» на тему «Процессор универсальной. Процессор универсальной эвм|

|

Скачать 2.21 Mb. | Название | Процессор универсальной эвм | | Анкор | ПОЯСНИТЕЛЬНАЯ ЗАПИСКА к курсовому проектированию по дисциплине «ЭВМ и периферийные устройства» на тему «Процессор универсальной | | Дата | 20.04.2022 | | Размер | 2.21 Mb. | | Формат файла |  | | Имя файла | 18VV1_Repin_PZ.docx | | Тип | Документы

#487486 | | страница | 14 из 14 |

|

Расчет быстродействия процессора Расчет быстродействия процессора

ДлярасчетавременныхпараметровБОДследуетучитыватьегоструктуру.4микропроцессорныхсекцииК1804ВС1,входнойрегистрданных(RDI),выходнойрегистрданных(RDO)ирегистрсостояния(PSW),мультиплексорысхемформированиясдвигов,схемаформированияпереноса.

Для рассматриваемой схемы все операции при расчете временныхпараметровможноразбитьследующимобразом:

логическиеиарифметические;

со сдвигомибезсдвига.

Дляоперацийопределяютсямаксимальныйпутьпрохожденияинформации. На основании задержек элементов через которые проходитинформация по максимальному пути можно рассчитать быстродействиепроцессора.

Операции включают в себя задержку чтения (из РМК БМУ), tРМК =11нс(К531ИР23).

Задержка дешифратора, с помощью которого выбираются шинныеформирователиилиRDI,tDC=20нс (К531ИД7).

Задержкашинныхформирователей,черезкоторыенавходыDпоступаетинформация,tшф=20нс (К531ИД7).

ЗадержкавыполненияоперациивМПСиформированиясигналовпереноса,tвс=100+15=115нс.

Задержкасрабатываниямультиплексоровсхемыформированиясдвиговtсфс =12нс.

Задержка формирования PSW tpsw = 20 нс (К531ИР23).Времяпредустановкиtпр=7 нс.

В итоге получаем следующее время выполнения операции:

tОП=tРМК+tDC+tшф+tвс+tСФС+tPSW+tпр

47

tОП=11+20+20+115+12+29+7=214нс. tОП=11+20+20+115+12+29+7=214нс.

Приполученнойдлительностиоперацииможнозадатьчастотугенераторапримерной равной4.67МГц.

Исходяизполученнойдлительностимашинноготактаможнорассчитатьвремявыполненияопераций,подсчитавнаибольшуюдлинупоследовательностимикрокоманд,ихреализующихиумножитьеенарассчитаннуюдеятельностьмашинноготакта.

Прямая автоинкрементная адресация – 4 микрокоманда.Косвенная автодекрементная адресация – 6 микрокоманд.Относительнаяиндексация–4микрокоманд.

Косвенная автоинкрементная адресация – 6 микрокоманда.Записьрезультата –2микрокоманды.

ВыполнениекомандыBIS–максимальноечисломикрокоманд35,максимальновремявыполнения –35*214=7490 нс.

ВыполнениекомандыNEG–максимальноечисломикрокоманд29,максимальновремявыполнения –29*214=6206 нс.

ВыполнениекомандыBGE–максимальноечисломикрокоманд12,максимальновремявыполнения–12*214=2568 нс.

ВыполнениекомандыINC–максимальноечисломикрокоманд25,

максимальновремявыполнения –25*214=5350нс.

ВыполнениекомандыSEC–максимальноечисломикрокоманд13,максимальновремявыполнения–13*214=2782 нс.

ВыполнениекомандыWAIT–максимальноечисломикрокоманд12,максимальновремявыполнения–12*214=2568 нс.

48

Заключение Заключение

ЦельюкурсовогопроектированияявляласьразработкапроцессорауниверсальнойЭВМ.Процессорразрабатывалсянаосновемикропроцессорного комплекта К1804. В качестве системы команд былаиспользованасистемакомандмикро-ЭВМPDP-11.Тоестьбылопроизведеноэмулированиеэтойсистемыкоманднаразрабатываемоммикропроцессоре.

Разработкавключалавсебяизучениесоставапрограммно-доступных регистров реализуемого процессора, форматы и содержаниезаданного набора команд, особенности адресации к памяти. Была изученаархитектурабазовоймикро-ЭВМнаБИСсерииК1804,накоторойэмулируетсязаданнаясистемакоманд,принципыработыБИС.Былразработаналгоритмвыполненияоперацийвпроцессоре.Поразработаннойсхемеалгоритмапроизводилосьсоставлениедиаграмммикропрограммнойлогики,показывающих,какконкретноописанныепоследовательности микроопераций реализуются в среде базовой микроЭВМ.

49

Литература. Литература.

Калабеков Б.А. Микропроцессоры и их применение в системахпередачииобработкисигналов–М.:Радиоисвязь,1985.

Коннов Н.Н., Пучков В.Г., Шашков Б.Д. Изучение архитектурымикроЭВМ.Методическиеуказания–Пенза:ППИ,1985.

Гурин Е.И., Коннов Н. Н., Механов В.Б. Проектирование процессораЭВМнасекционированныхмикропроцессоровБИС.Методическиеуказания

– Пенза:ППИ,1993.

ШилоВ.Л.ПопулярныемикросхемыТТЛ.–М:Аргус,1993

50

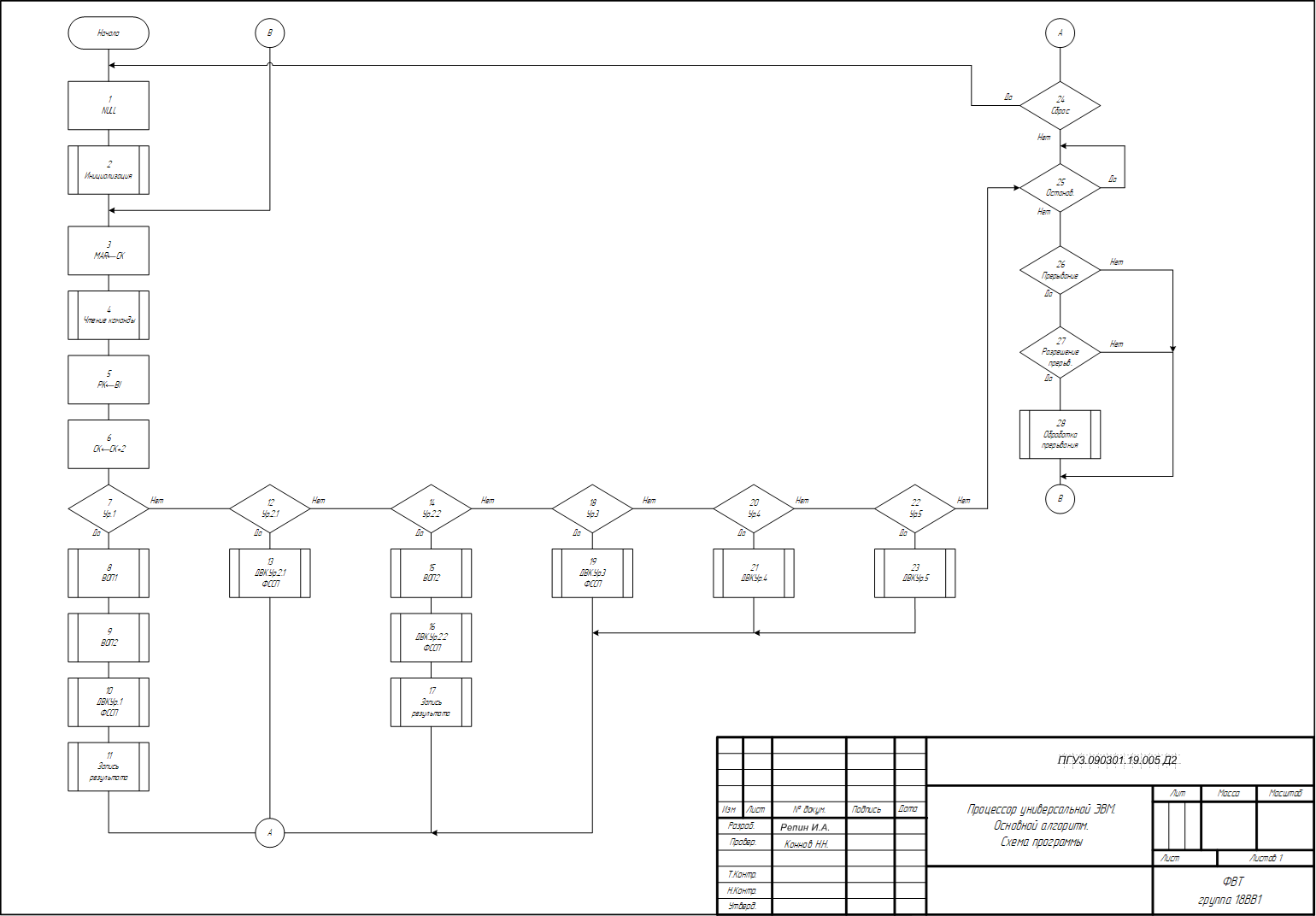

Приложение А1. Схема основного алгоритма

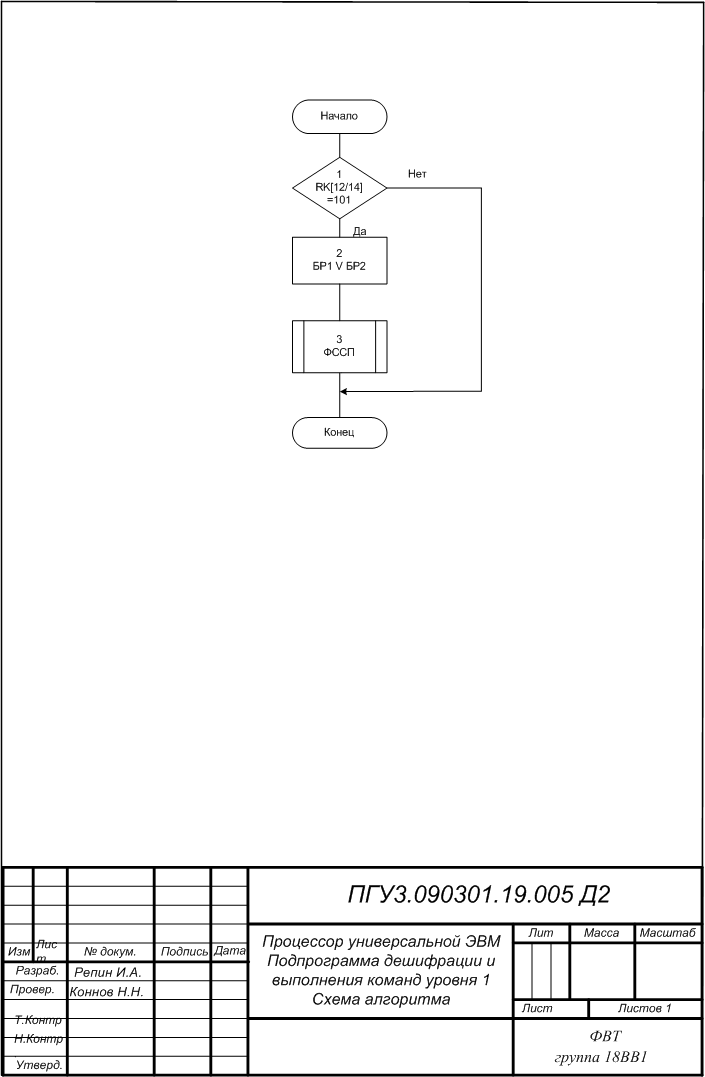

Приложение А.2 Схема подпрограммы дешифрации команд уровня 1

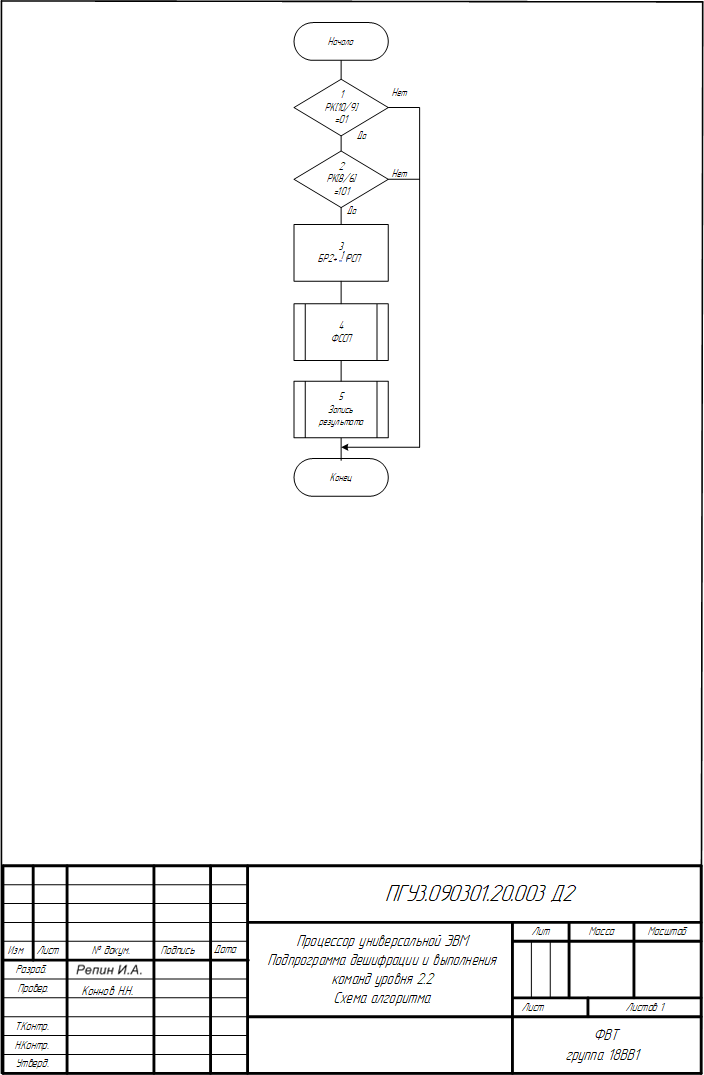

Приложение А.3 Схема подпрограммы дешифрации команд уровня 2.2 Приложение А.3 Схема подпрограммы дешифрации команд уровня 2.2

ПриложениеА.4Схемаподпрограммыдешифрациикомандуровня 3

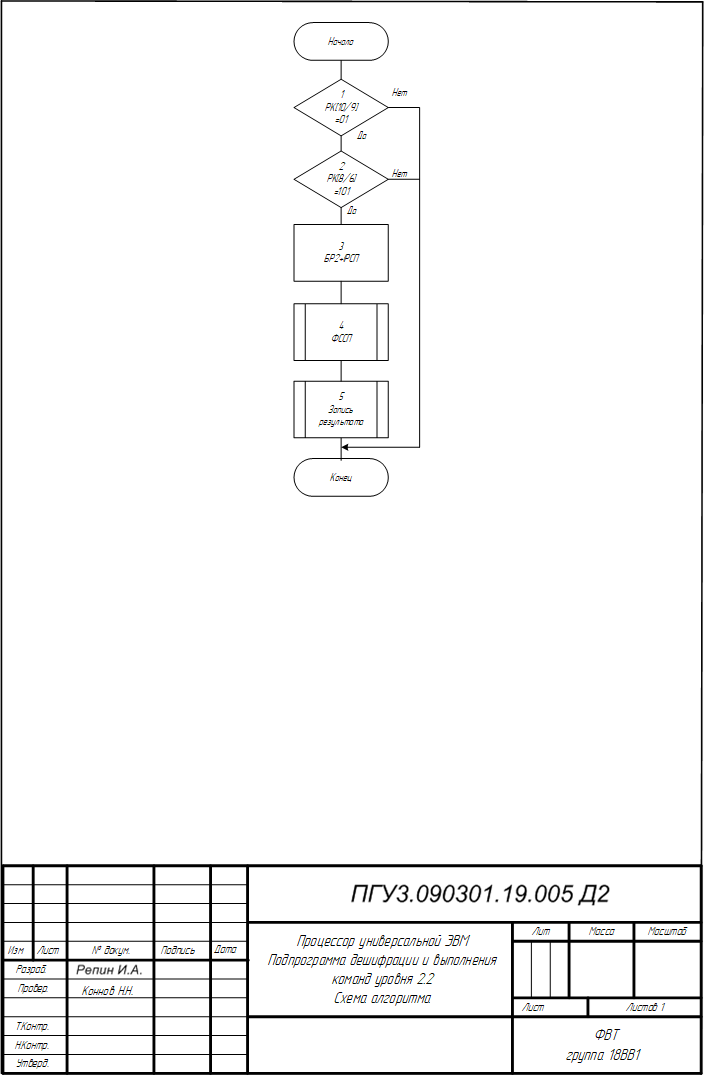

Приложение А.5 Схема подпрограммы дешифрации команд уровня 2.2

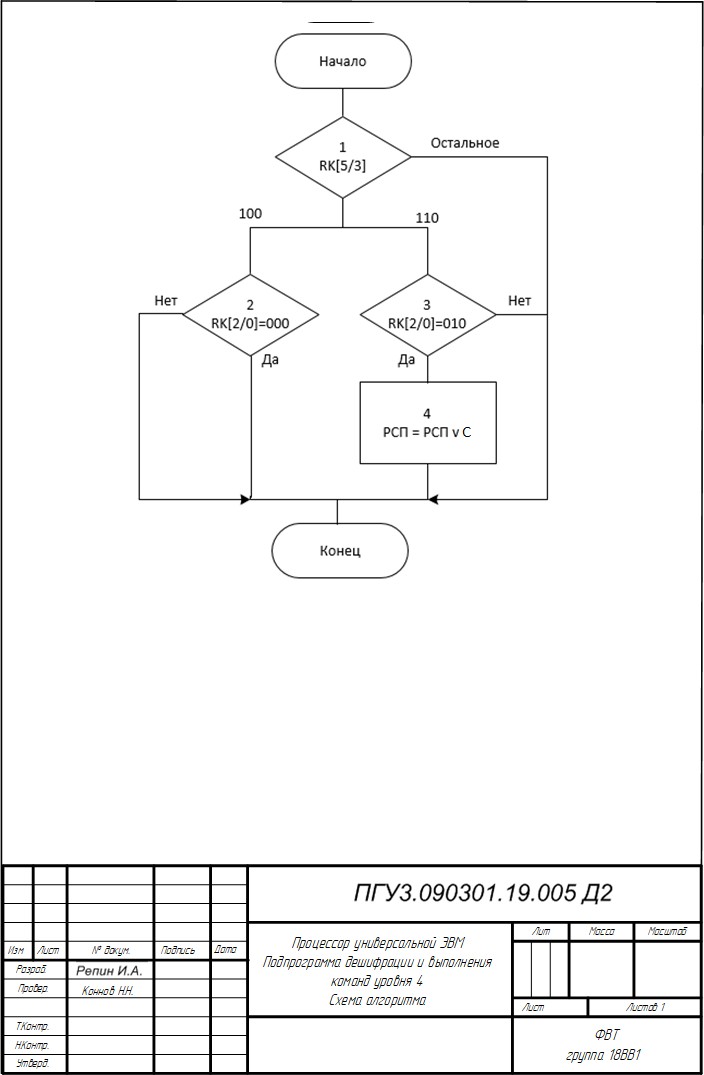

ПриложениеА.6Схемаподпрограммыдешифрациикомандуровня 4

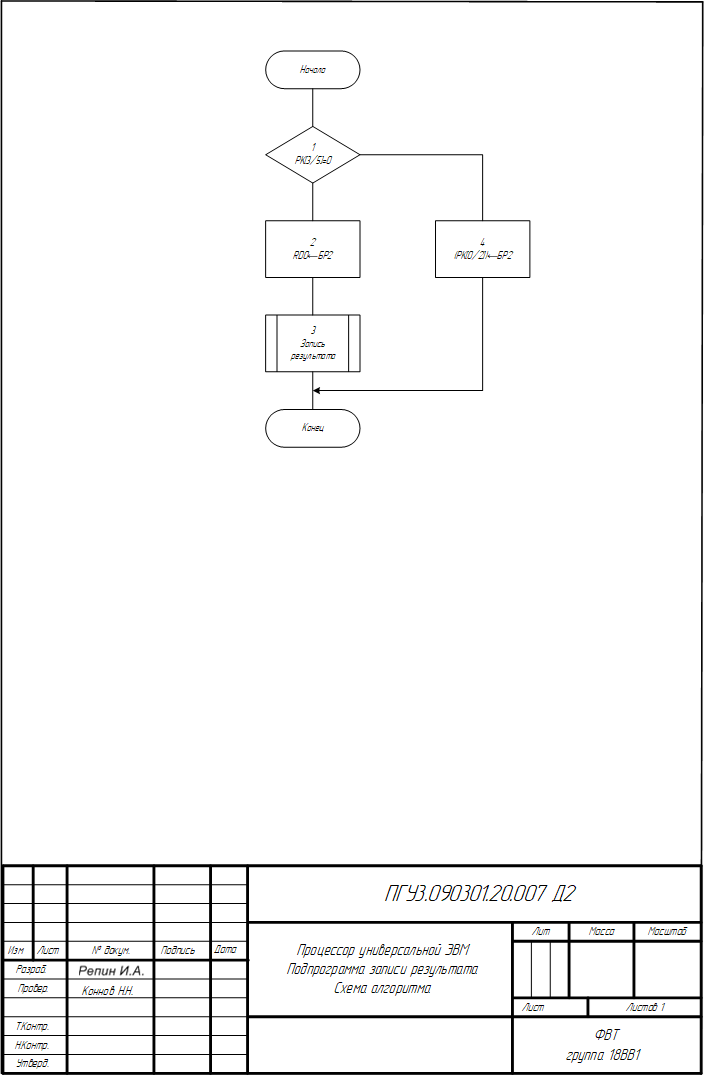

Приложение А.7 Схема подпрограммы записи результата

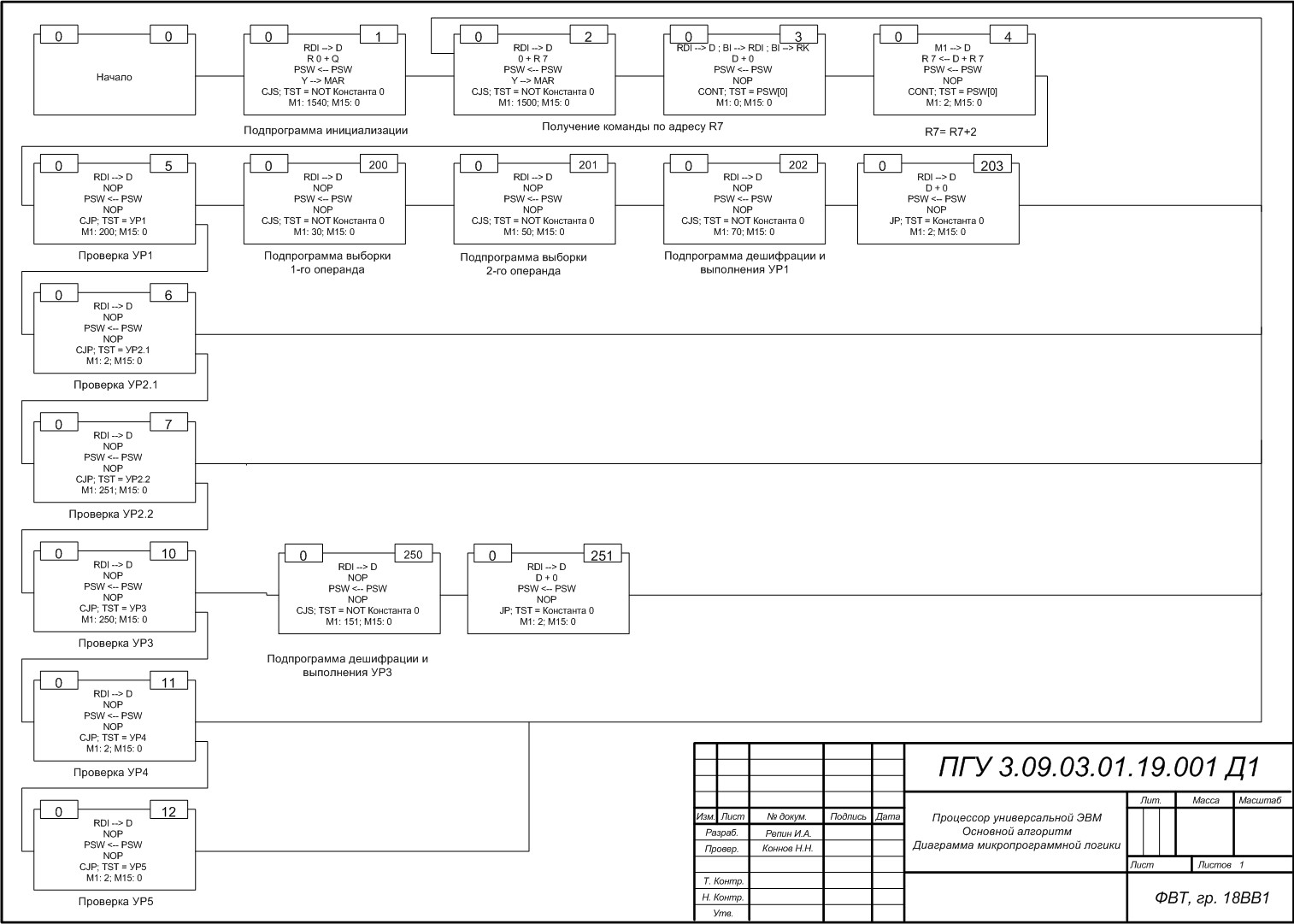

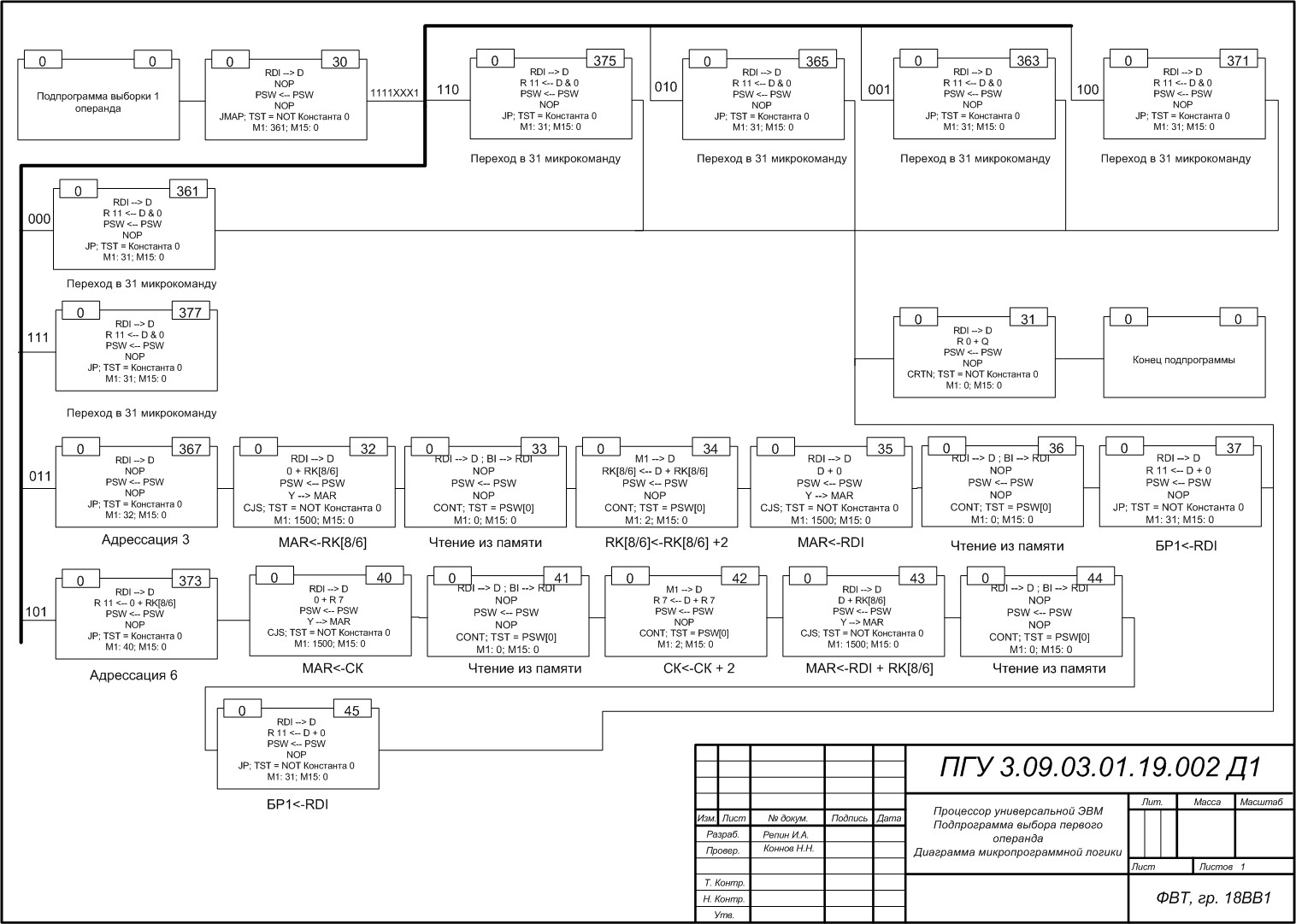

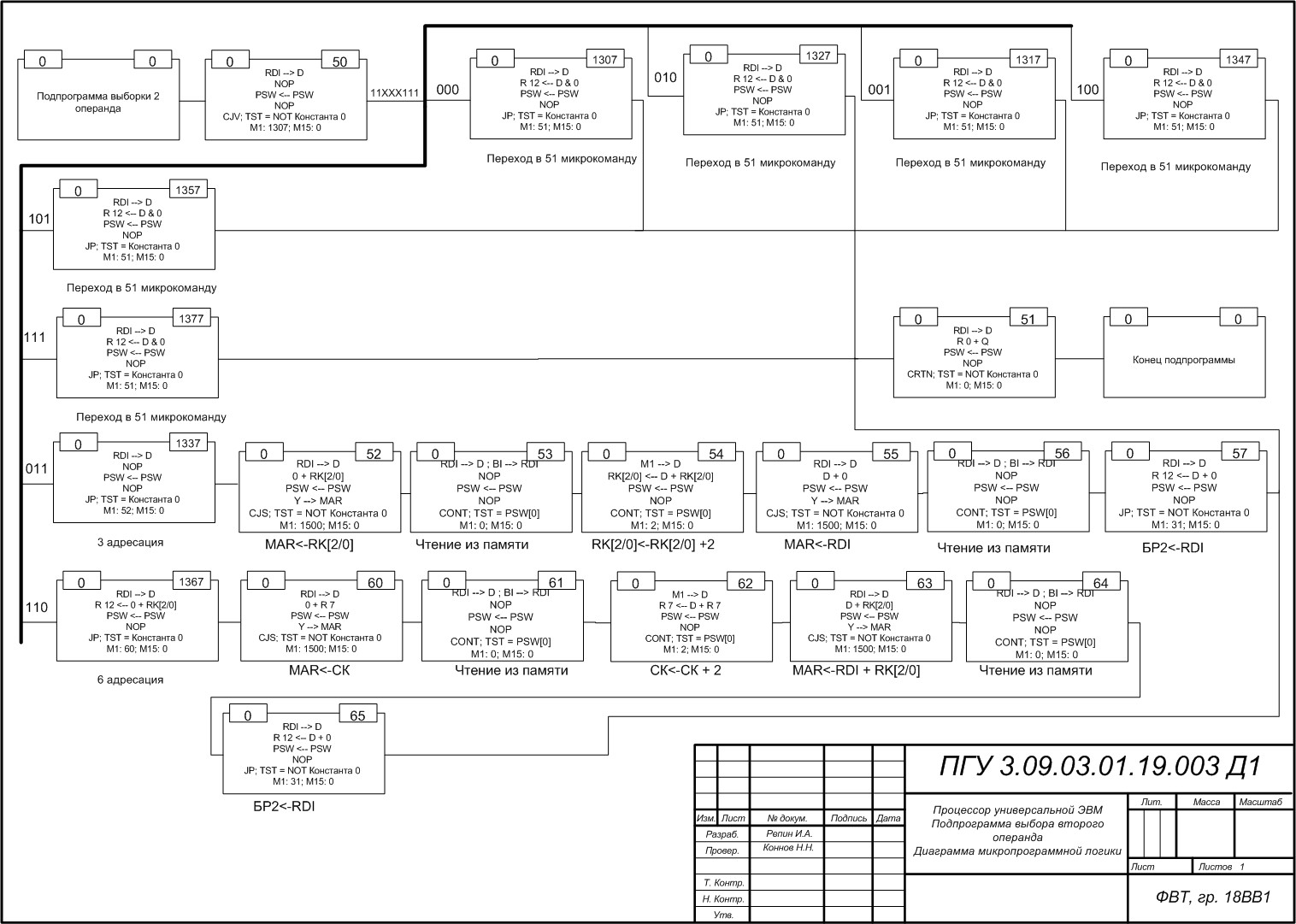

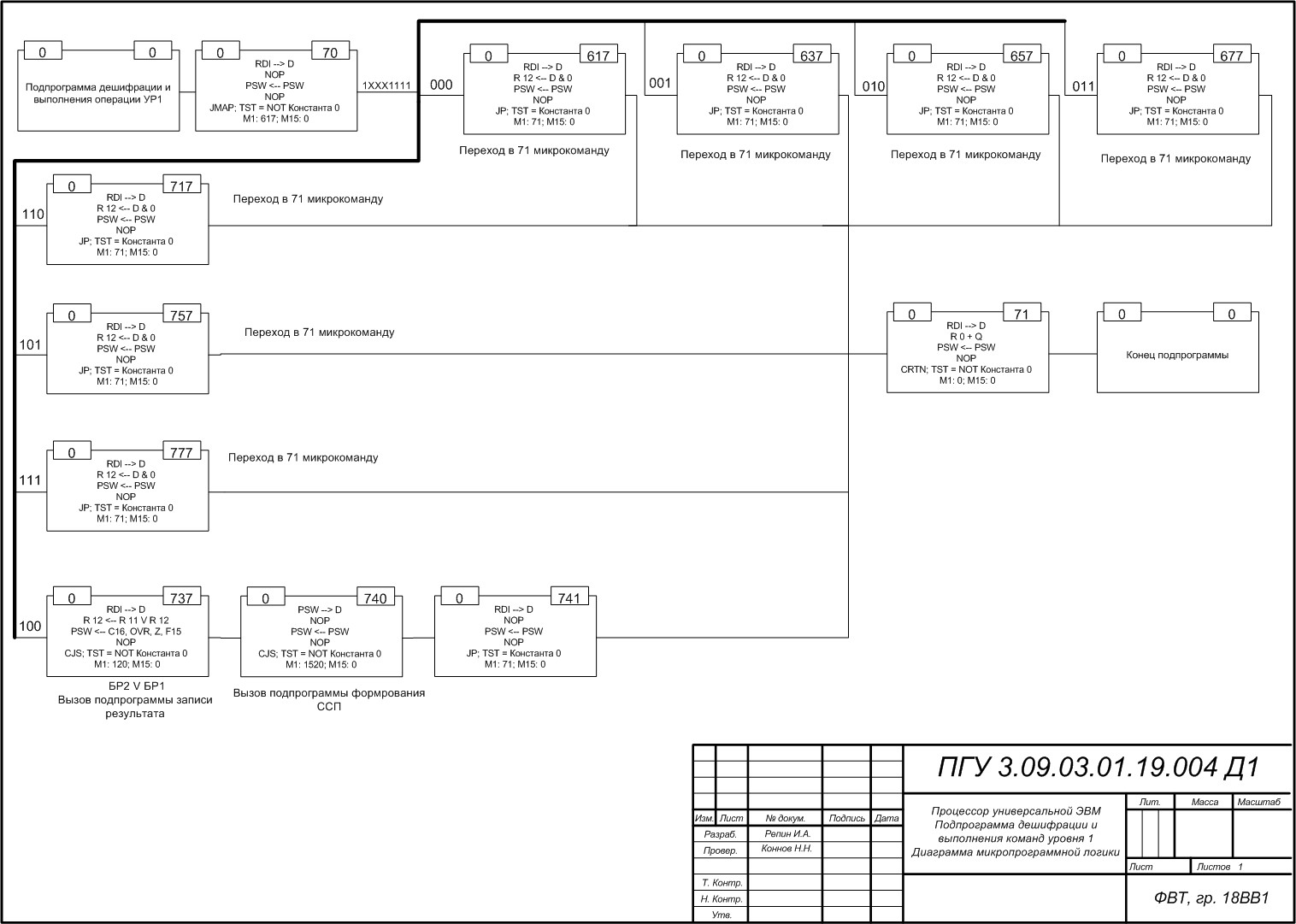

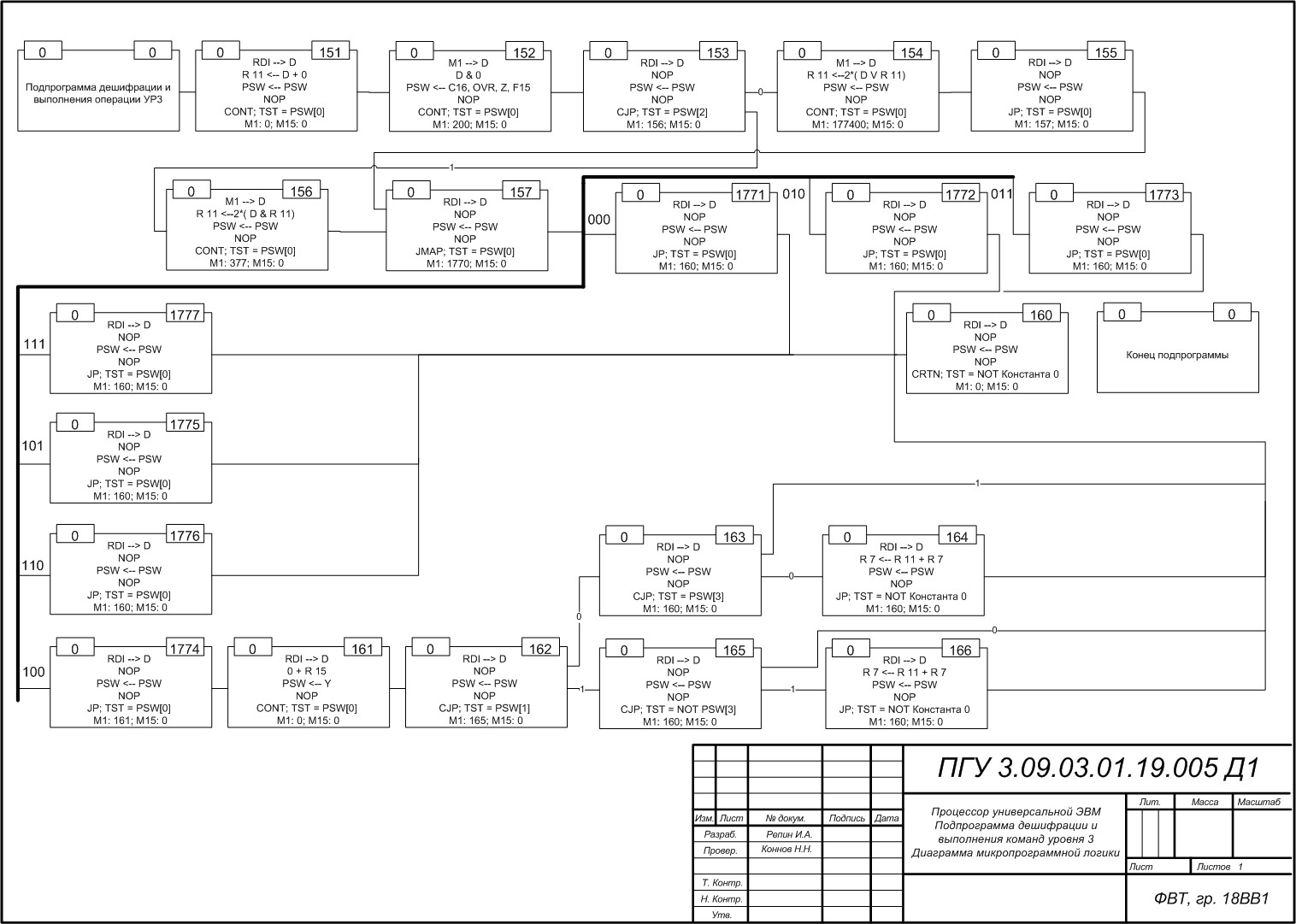

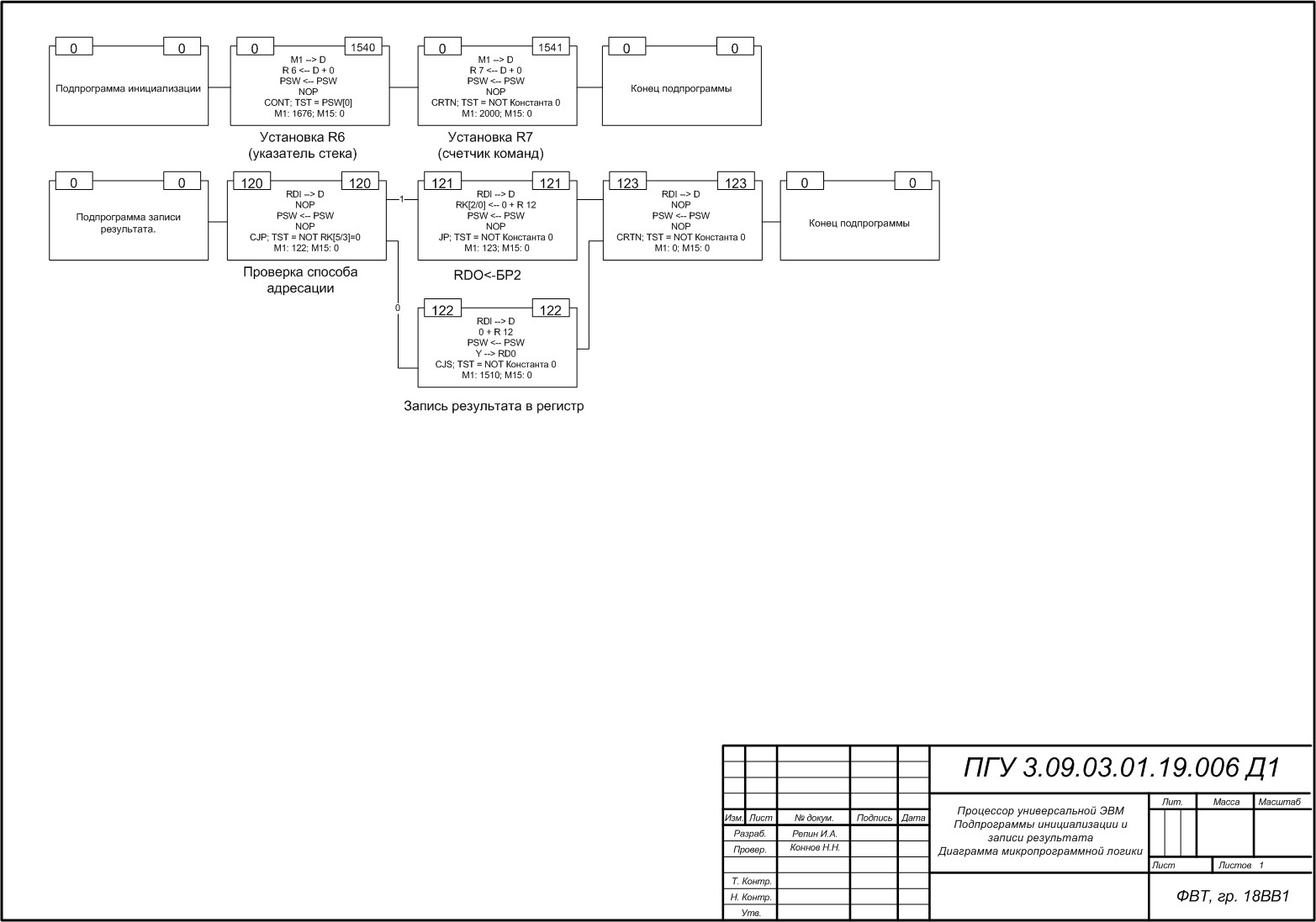

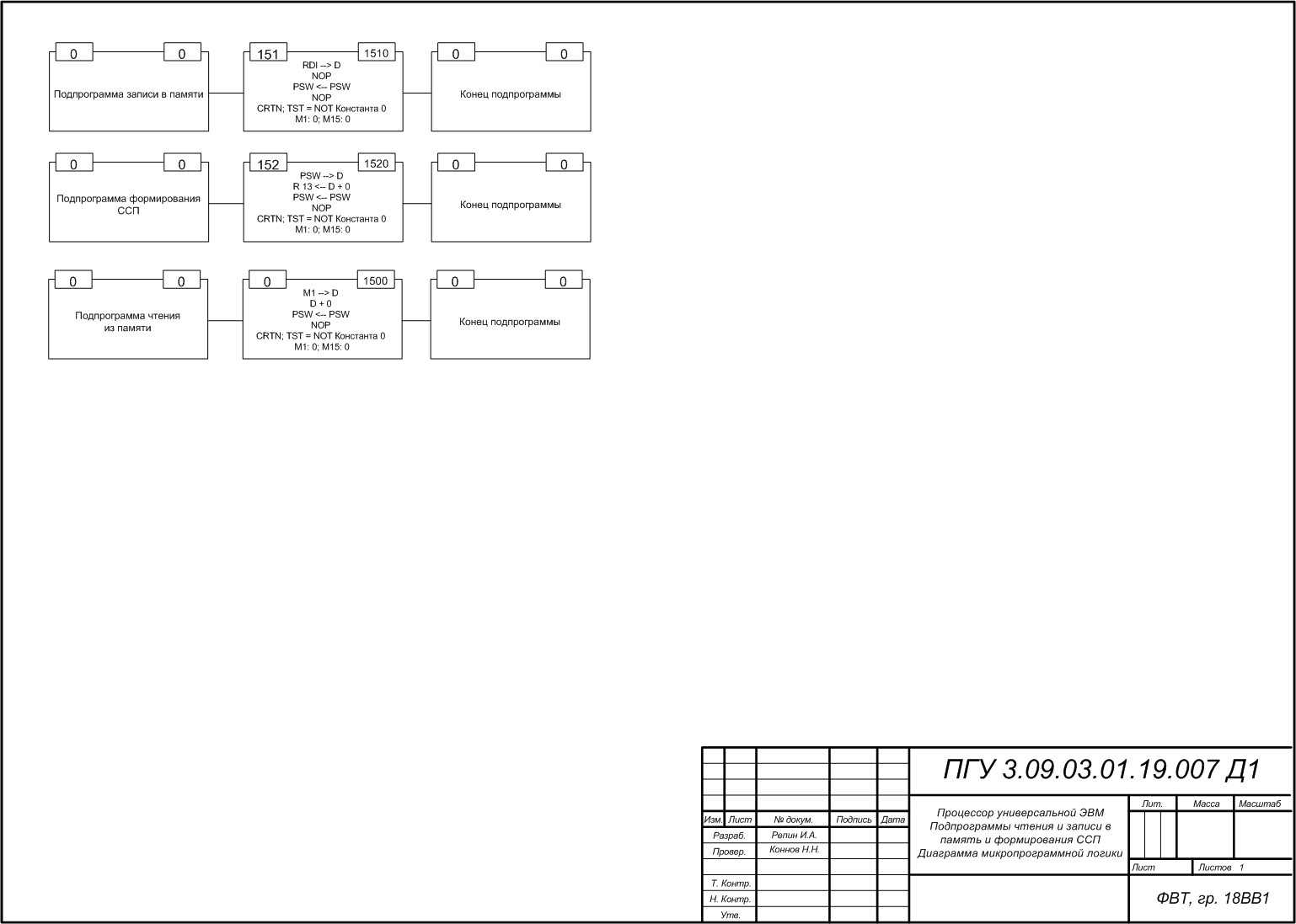

ПриложениеА.8СхемаДМЛ

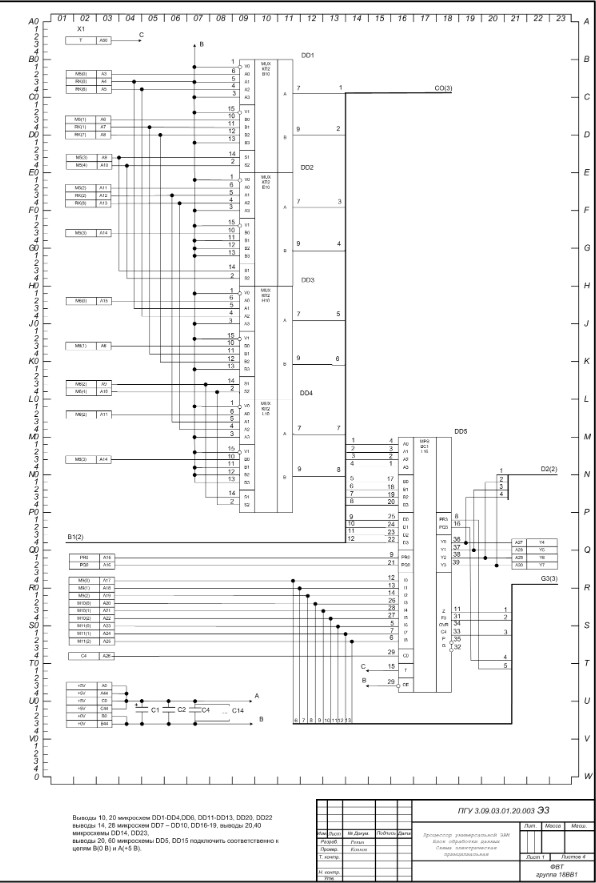

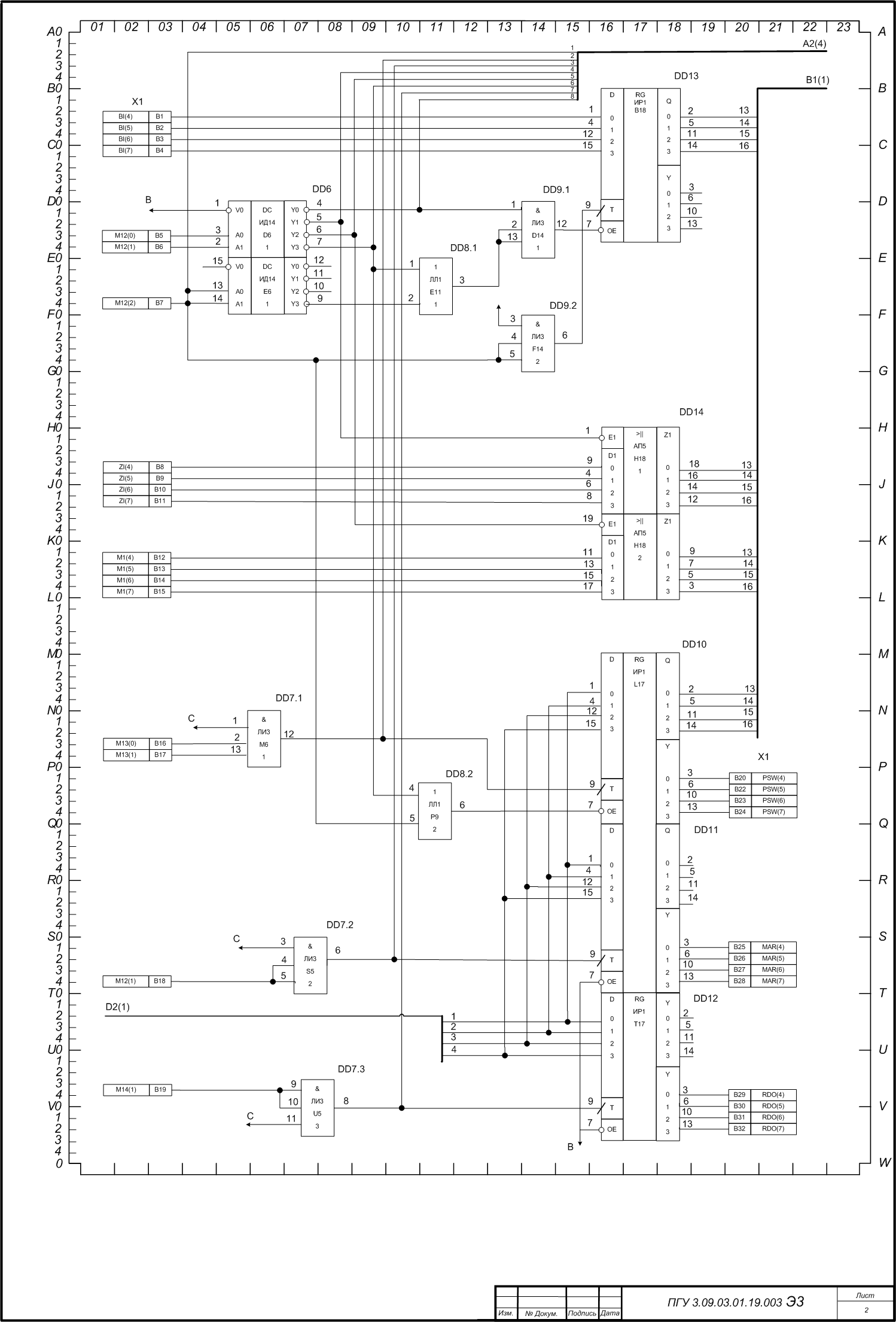

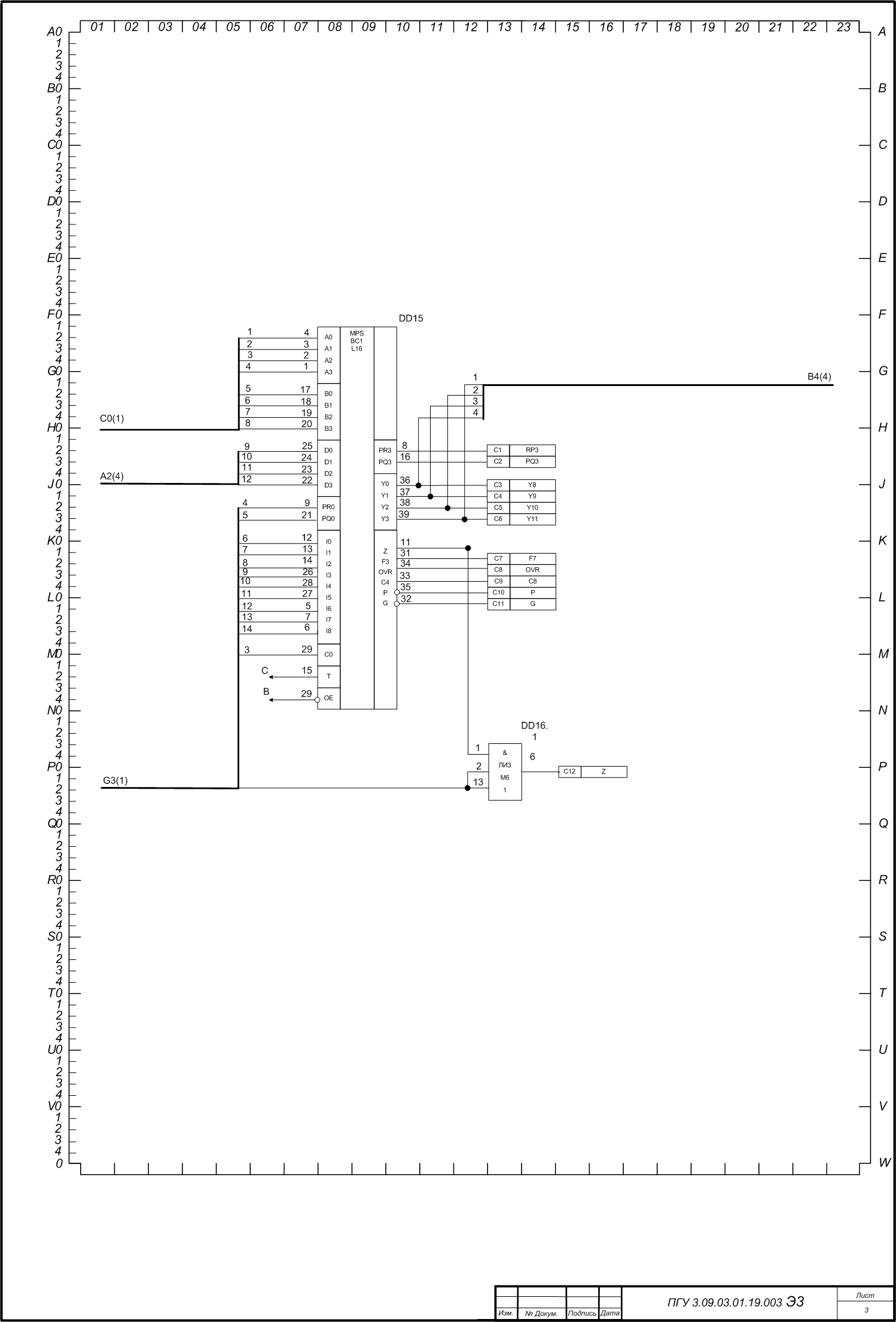

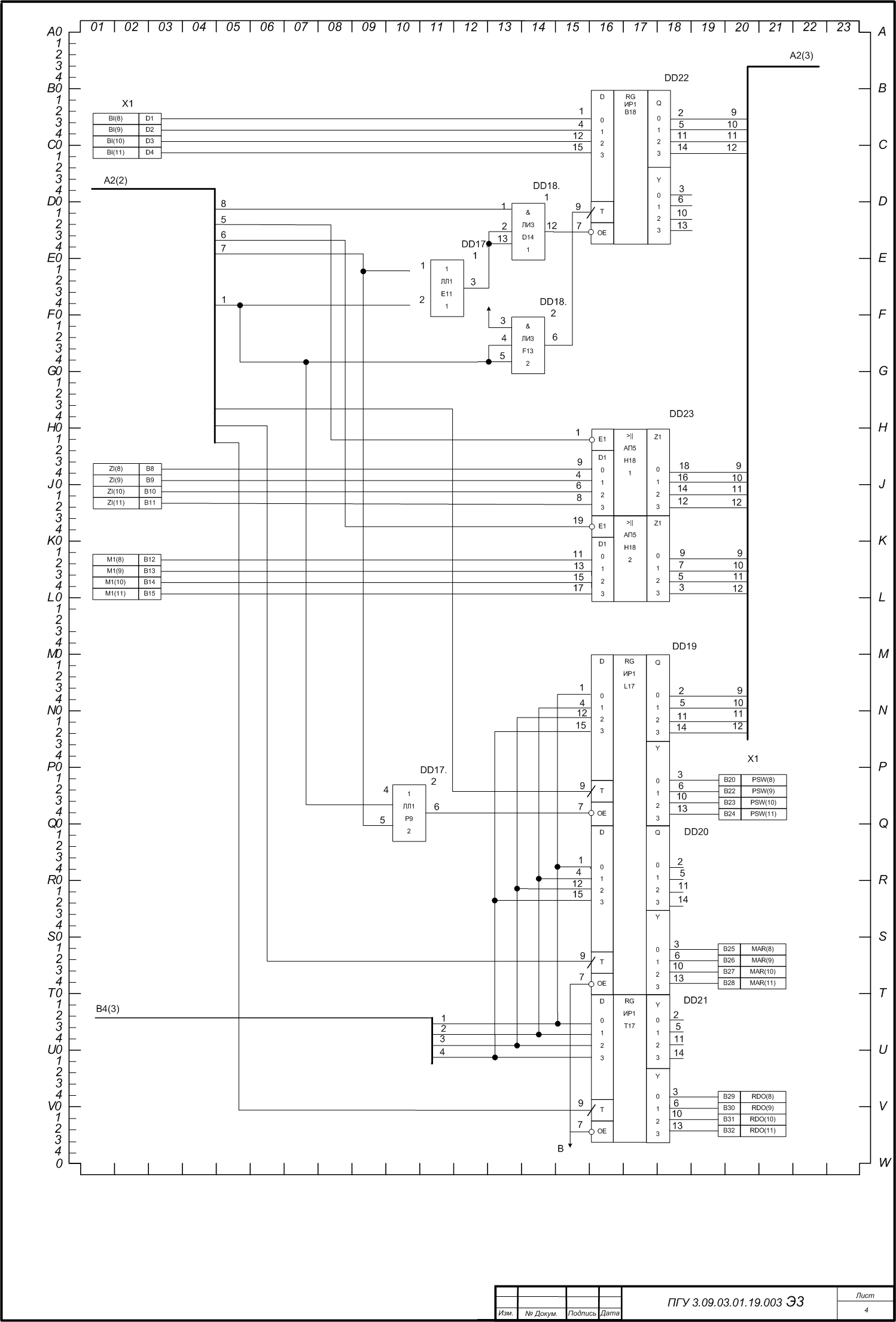

Приложение А.10 Принципиальная схема

3

4 |

|

|

Скачать 2.21 Mb.

Скачать 2.21 Mb.