Расчетно-графическая работа ЭВМ. Разработка специализированной микроэвм с микропрограммный управлением

Скачать 1.41 Mb. Скачать 1.41 Mb.

|

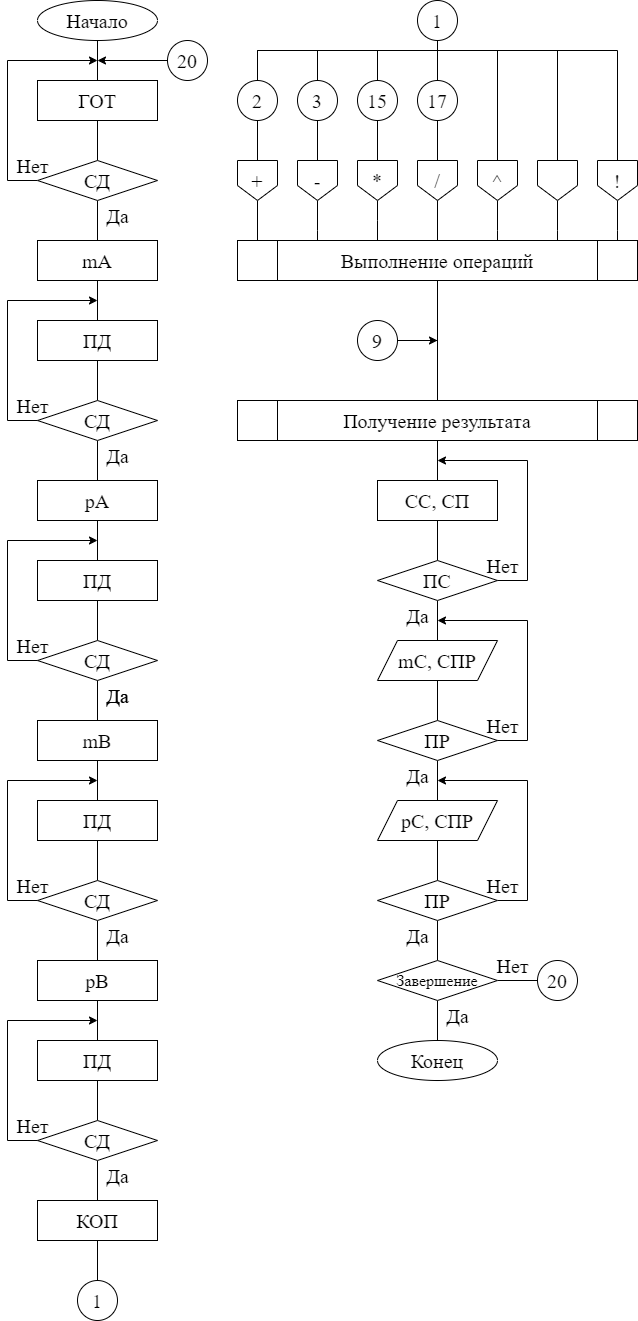

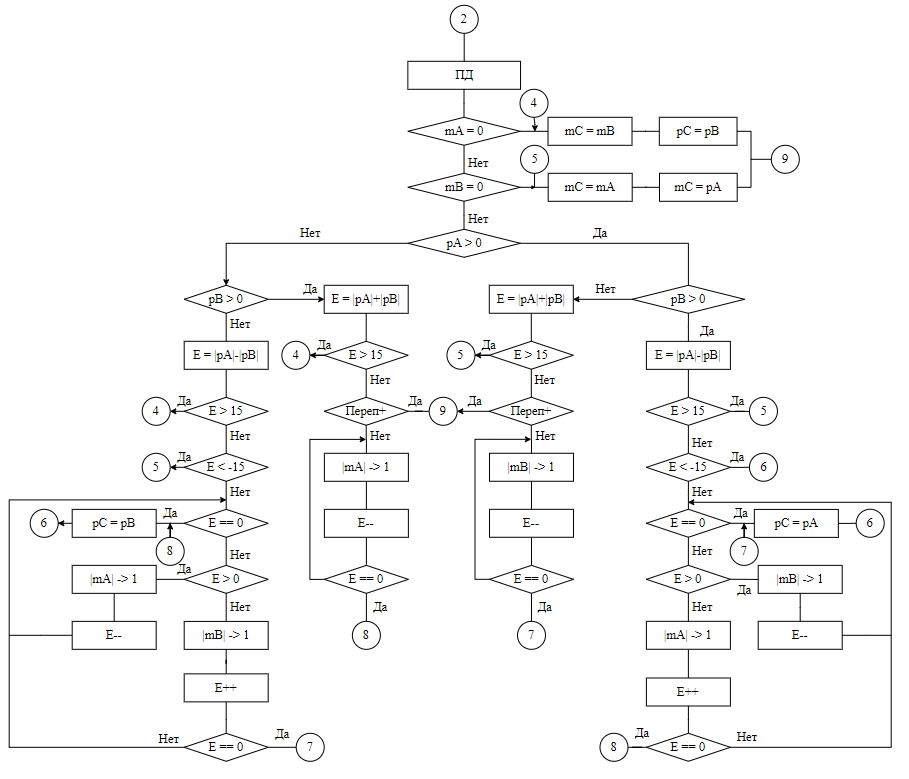

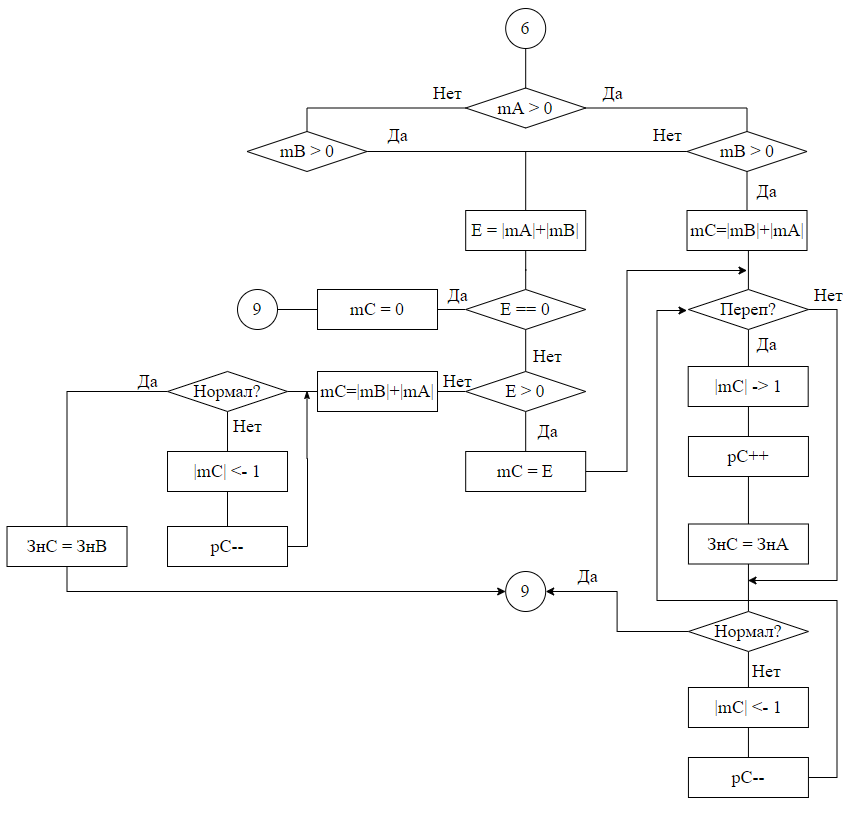

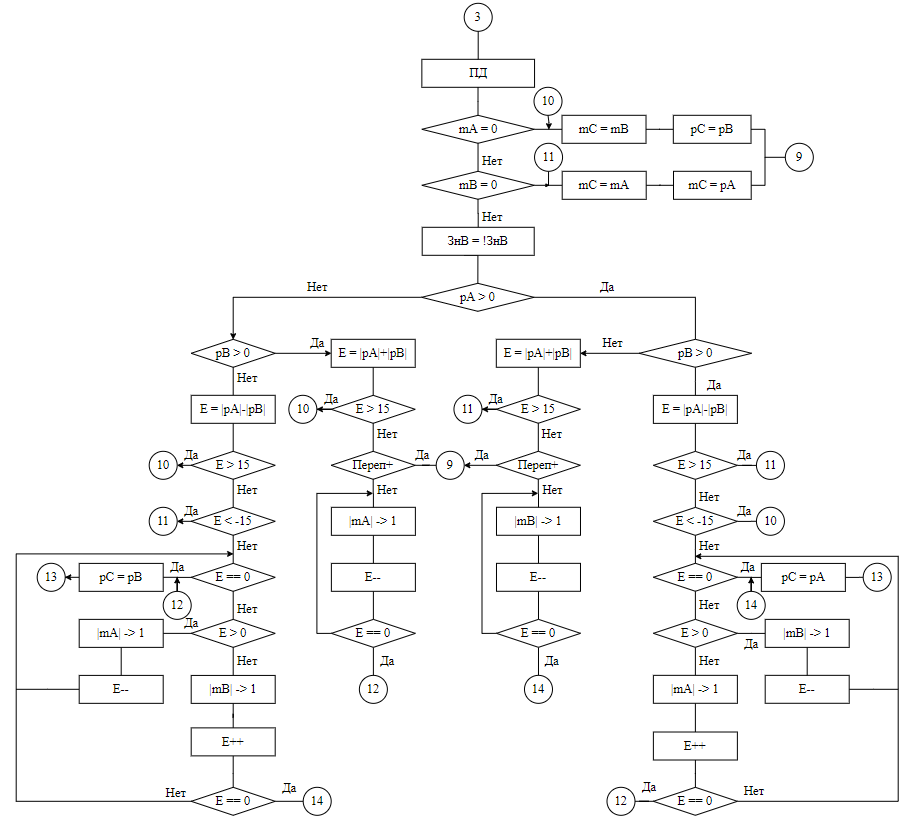

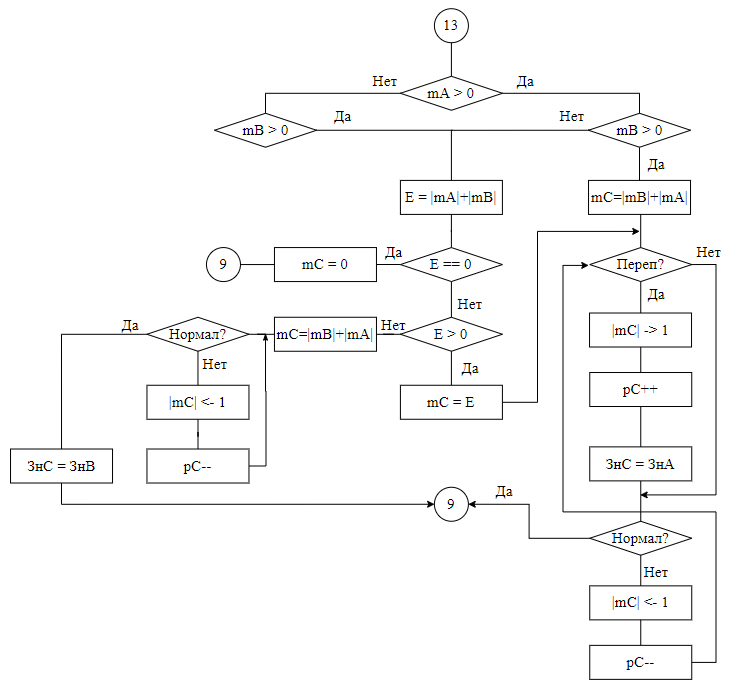

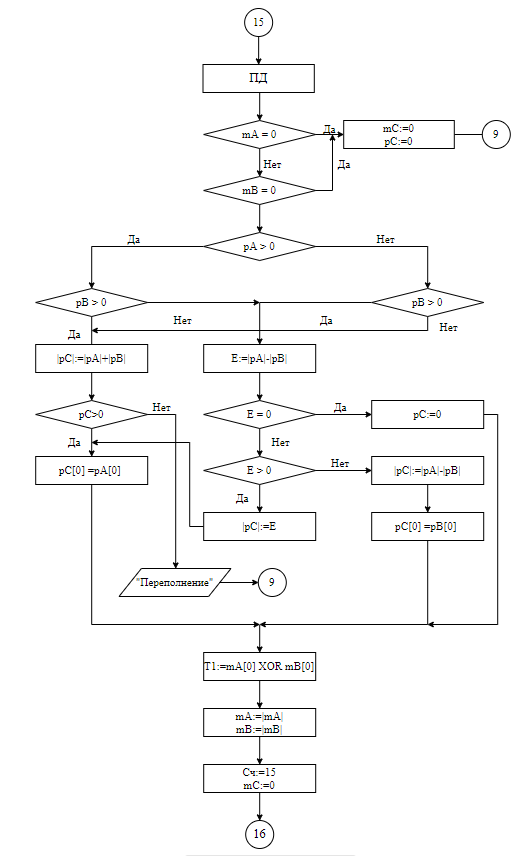

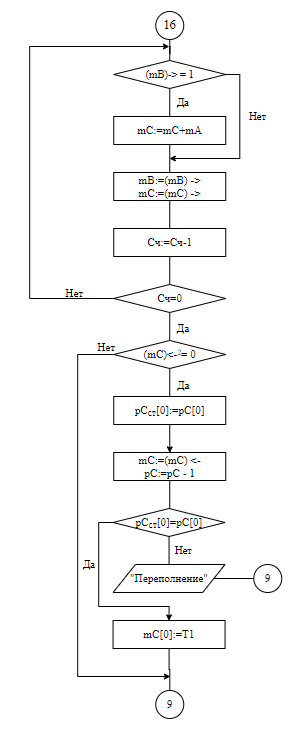

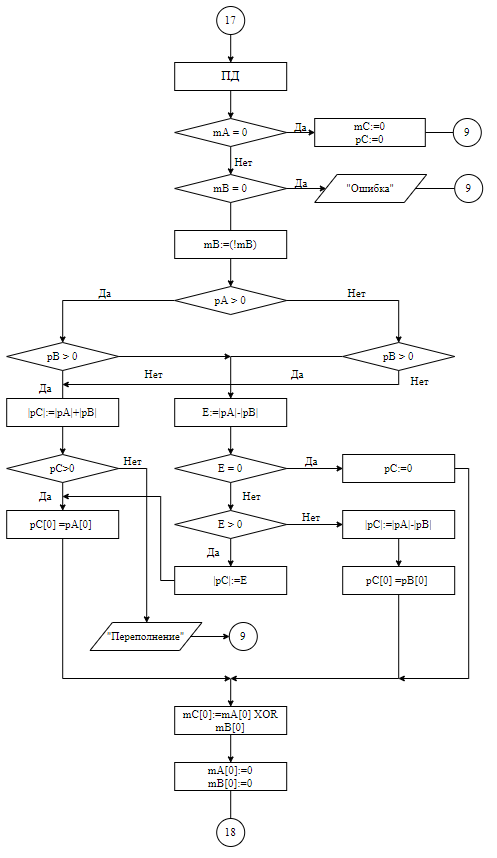

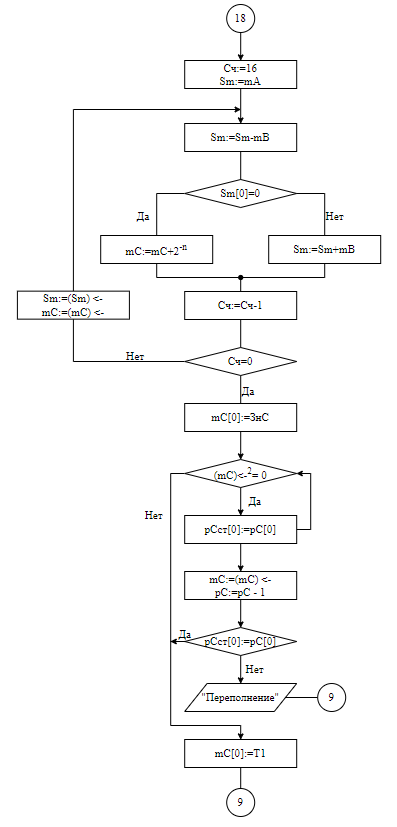

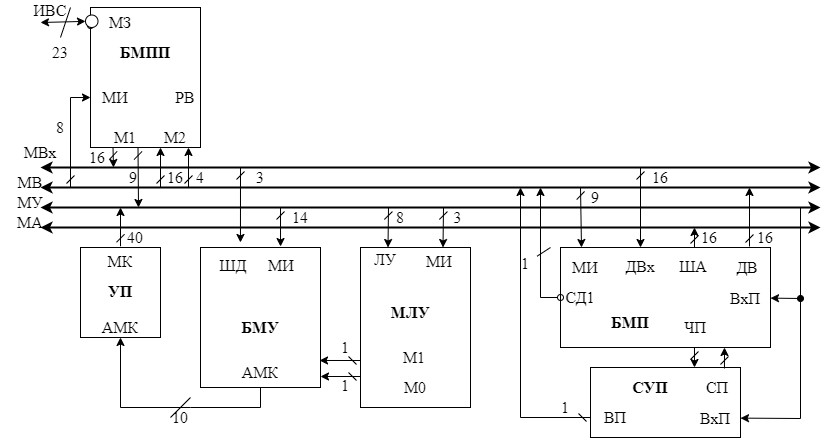

Формулировка задания Формулировка задания1. Тема: «Разработка специализированной микроЭВМ с микропрограммный управлением». 2. Технические условия: - длина разрядной сетки – 16 разрядов; - способ реализации – программный; - операции: деление, умножение младшими разрядами вперёд, сложение, вычитание, AND, OR, NOT в прямом коде с плавающей точкой. 3. Элементная база: микропроцессорный комплект серии К584 и совместимые с ним интегральные микросхемы других серий. 4. Рассчитать технические параметры микроЭВМ. 5. Содержание графической части работы: - структурная схема алгоритма; - структурная схема микроЭВМ; - функциональная схема микроЭВМ; - микропрограмма работы микроЭВМ; - графики временных диаграмм работы микроЭВМ; - блок синхронизации микроЭВМ. Структура внешнего интерфейса  Рисунок 1 – Асинхронный специальный интерфейс Пояснения к схеме: ВС – внешняя среда; МЭВМ – микроЭВМ; ГОТ – готовность; ШД – шина данных; СС – слово сообщение; КОП– код операции в битах; СД – сопровождение данных; ПД – принятие данных; СП – сообщение передано; ПС – принятие сообщения; СПР – сопровождение результата; ПР – подтверждение результата. Разработка алгоритма функционирования микроЭВМ Алгоритм арифметических и логических операций  Рисунок 2 – Общая схема алгоритма   Рисунок 3 – Алгоритм суммирования   Рисунок 4 – Алгоритм вычитания   Рисунок 5 – Алгоритм умножения   Рисунок 6 – Алгоритм деления Структурная схема МЭВМ (микро-ЭВМ)  Рисунок 7 – Структурная схема микро-ЭВМ Рисунок 7 – Структурная схема микро-ЭВМПояснения к схеме: ИВС – интерфейс внешней системы; МВх – магистраль входа; МВ – магистраль выхода; МУ – магистраль управления; МА –магистраль адреса; БМП – блок микропроцессора; МИ – микроинструкция; ВхП – вход переноса; ЧП – частичный перенос; СД1 – сдвиг одинарного слова; ДВх–данные входные; ША –шина адреса; ДВ –данные выходные; СУП – схема ускоренного переноса; ВП – вход переноса; СП – секционный перенос; БМУ – блок микропрограммного управления; МЛУ – мультиплексор логических условий; ЛУ – логические условия; МК – микрокоманды; АМК – адрес микрокоманды; БМПП – блок магистральный приёмо-передатчиков; РВ – разрешение выдаче М3; Операционная часть (ОЧ) включает блок микропроцессоров БМП со схемой ускоренного переноса СУП. Управляющая часть (УЧ) содержит блок микропрограммного управления БМУ, мультиплексор логических условий МЛУ и управляющую память УП. Интерфейсная часть выполнена на базе блока магистральных приёмопередатчиков БМПП, который обеспечивает обмен между интерфейсом внешней системы ИВС и внутренним четырёхмагистральным техническим интерфейсом. ИВС подключён к двунаправленной магистрали М3 БМПП. Выходная внутренняя магистраль М1 БМПП соединена с магистралями МВх и МУ, по ней осуществляется ввод данных, кода операции и сигнала сопровождения данных СД. Входная внутренняя магистраль М2 БМПП подключена к магистралям МВ и МУ и предназначена для вывода данных, сигналов готовности ГТ и подтверждения данных ПД. БМП связан своими шинами входных данных ДВх, выходных данных ДВ, адреса ША, входа микроинструкции МИ с соответствующими магистралями МВх, МВ, МА и МУ. К магистрали МУ также подключены выход инверсного сигнала сдвига одинарного слова !СД1 в качестве логического условия и вход переноса ВхП арифметико-логического устройства (АЛУ), который соединён и с аналогичным входом СУП. Выходной перенос ВП формируется на соответствующей выходной шине СУП и подключается в качестве второго логического условия к МУ. ВП вырабатывается на основе частичных переносов ЧП, поступающих с процессорных секций БМП. Одновременно с ВП в СУП формируются и межсекционные переносы СП, ускоряющие процесс суммирования в БМП. Функционирование УЧ в микрокомандном цикле работы микроЭВМ осуществляется следующим образом. БМУ на выходной шине адреса микрокоманды АМК формирует код адреса текущей микрокоманды, который поступает на одноимённый вход УП. На выходную шину МК УП считывается соответствующая микрокоманда. Микрокоманда содержит микроинструкции всех функциональных устройств и блоков, а также сигналы взаимодействия с внешней средой при обмене через ИВС. Поля микроинструкций Пример формата микрокоманды для рассматриваемой микроЭВМ приведён ниже.

Нумерация шин магистрали управления Таблица 1

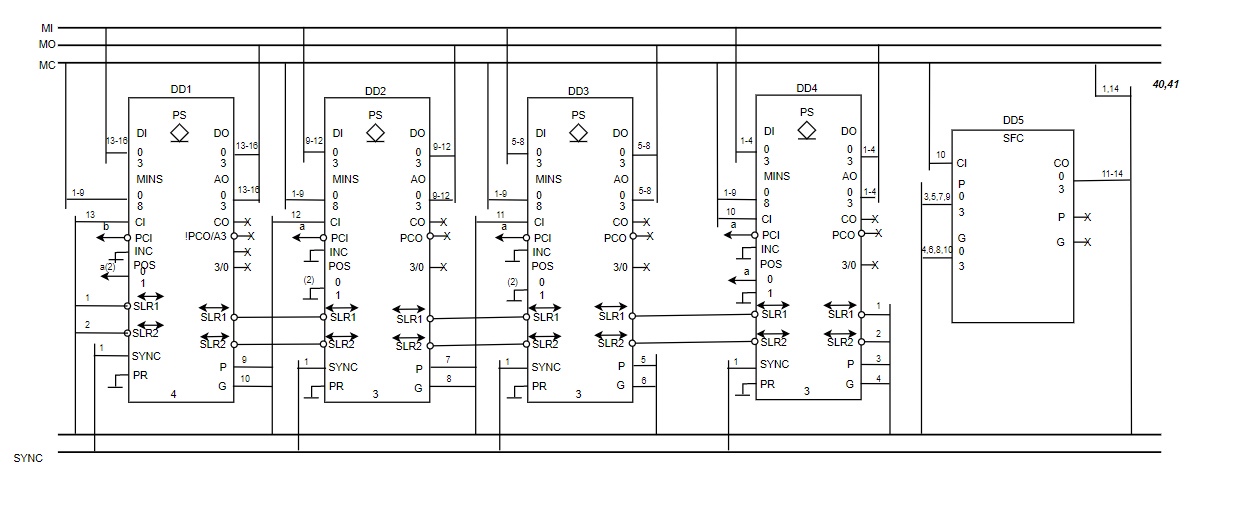

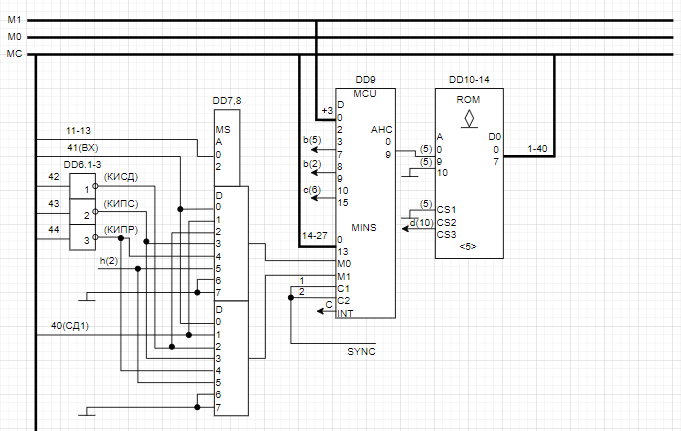

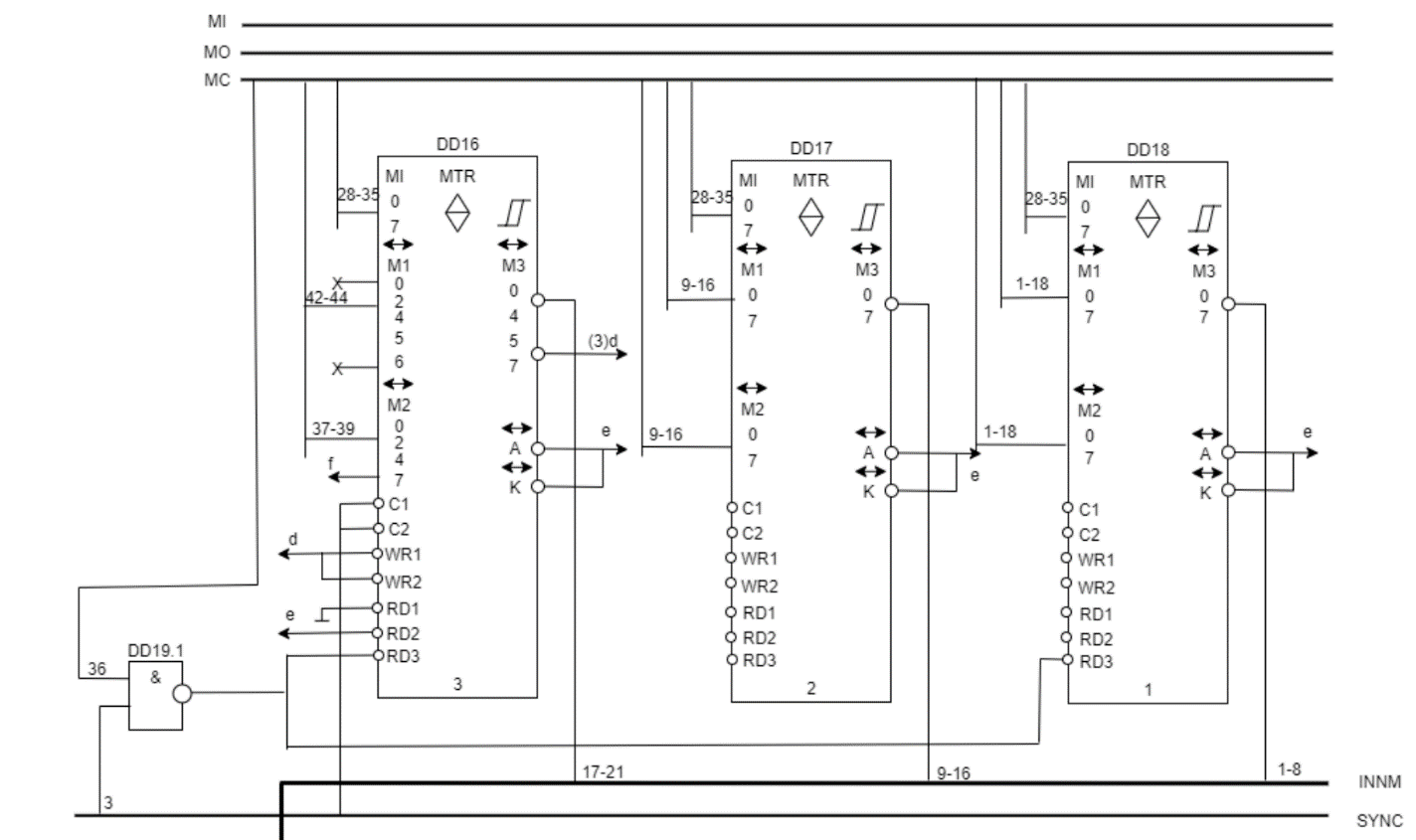

Функциональная схема АЛУ БМП  Рисунок 8 – Функциональная схема АЛУ БМП Функциональная схема управляющей части  Рисунок 9 – Функциональная схема БМУ Микроинструкции МЛУ

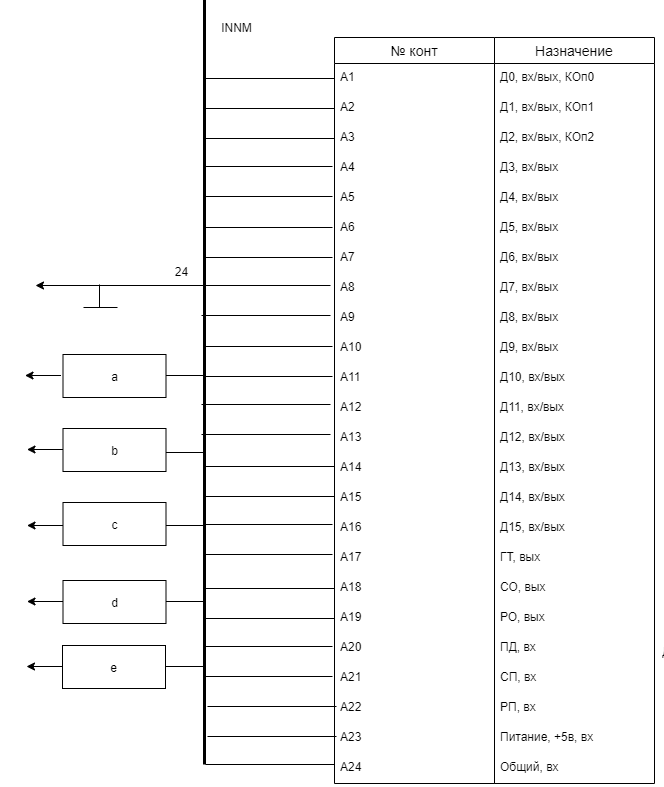

Функциональная схема интерфейсного блока БМПП   Рисунок 10 – Функциональная схема БМПП Построение временных диаграмм БМУ-К584ВУ1 без скобок Таблица 2

БМП-К584ВМ1А без скобок Таблица 3

БМПП-К584ВВ1безрегистровый без PCU Таблица 4

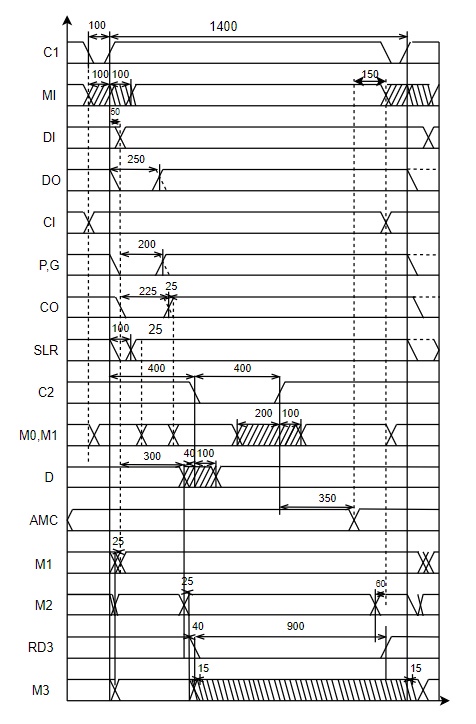

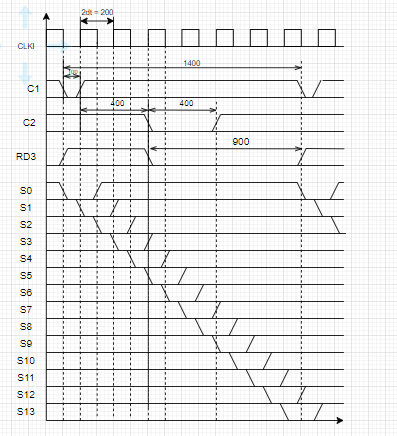

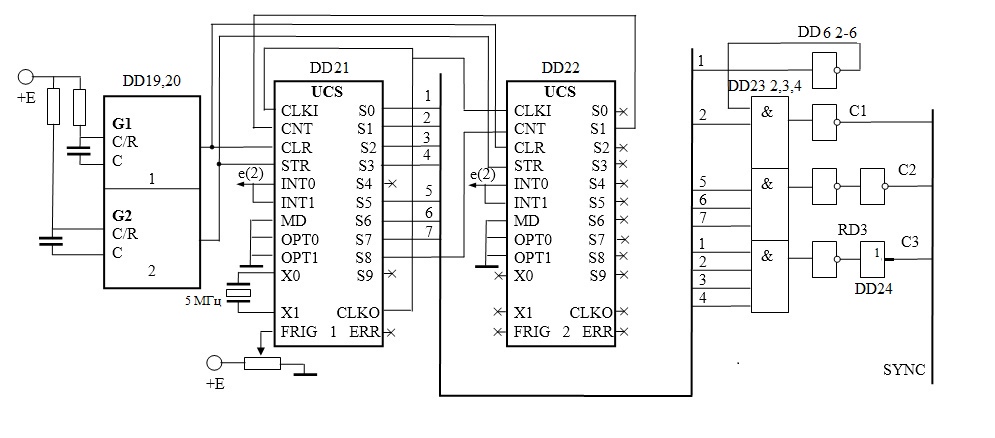

Рисунок 11 – Временная диаграмма Диаграмма синхроимпульсов  Рисунок 12 – Диаграмма синхроимпульсов Блок синхронизации  Рисунок 13 – Блок синхронизации Таблица 5

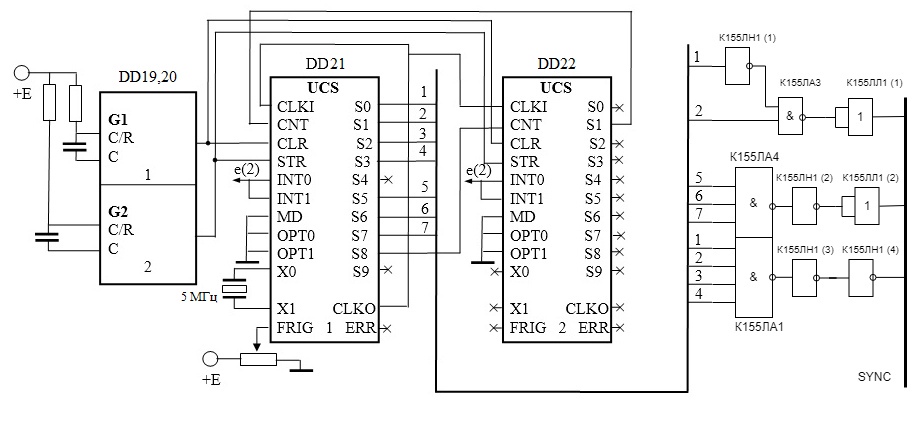

Использование микросхем, перечисленных в таблице 5, в устройстве блока синхронизации можно увидеть на рисунке 14.  Рисунок 14 – Блок синхронизации | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||