симс. Реферат_Зайнуллин. Реферат по дисциплине Схемотехника и микропроцессорные системы на тему Базовые логические элементы. Лэ с открытым коллектором. Лэ с тремя состояниями

Скачать 166.28 Kb. Скачать 166.28 Kb.

|

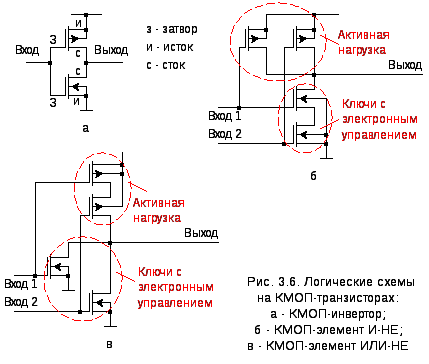

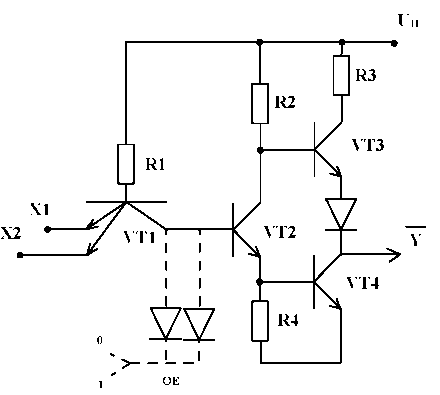

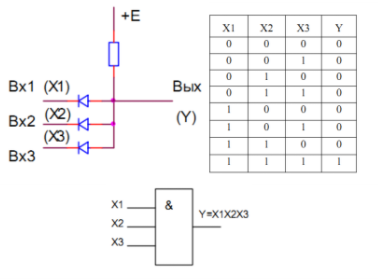

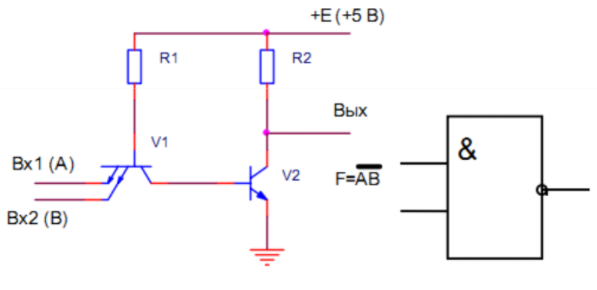

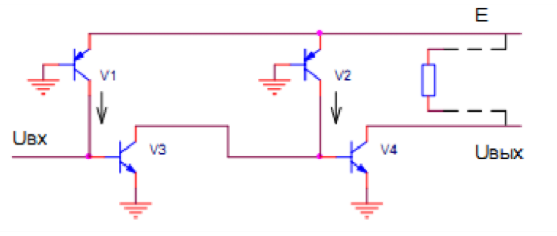

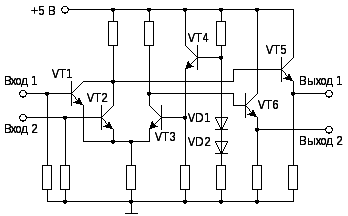

0.1 В.Министерство науки и высшего образования Российской Федерации Федеральное государственное автономное образовательное учреждение высшего образования «КАЗАНСКИЙ (ПРИВОЛЖСКИЙ) ФЕДЕРАЛЬНЫЙ УНИВЕРСИТЕТ» Набережночелнинский институт (филиал) Кафедра автоматизации и управления Направление подготовки (специальность): 15.03.04 - Автоматизация технологических процессов и производств РЕФЕРАТ по дисциплине: «Схемотехника и микропроцессорные системы» на тему: «Базовые логические элементы. ЛЭ с открытым коллектором. ЛЭ с тремя состояниями. Вариант №4» студент 3 курса группа 2192213 Зайнуллин Р.Р. Набережные Челны – 2022 Содержание Базовые логические элементы Логические элементы с открытым коллектором Логические элементы с тремя состояниями Базовые логические элементы В начале развития цифровой аппаратуры было получено большое количество различных схемотехнических решений, выполняющих базовые логические операции. При этом широкое практическое применение получили только некоторые из них. Данные элементы наилучшим образом включают ряд важных как для потребителя, так и для производителя параметров. В данный момент при проектировании и конструировании интегральных схем наибольшее распространение получили следующие базовые логические элементы: - диодно-транзисторная логика (ДТЛ); - транзисторно-транзисторная логика (ТТЛ, ТТЛШ); - эмиттерно-связанная логика (ЭСЛ); - интегрально-инжекционная логика (И2Л); - логика на однотипных полевых транзисторах (n-МОП и p-МОП); - логика на комплементарных полевых транзисторах (КМОП). Первые три типа логики используют биполярные транзисторы, последние два – полевые. Распространение нескольких из вышеописанных типов логики, выполняющих схожие логические функции, объясняется различием их основных параметров, что в зависимости от технических требований и условий эксплуатации позволяет конструировать электронные средства с необходимыми характеристиками. Самыми распространенными в настоящий момент являются интегральные схемы, реализующие ТТЛ и её разновидности (ДТЛ, ТТЛШ). Данный тип интегральных схем, в соответствии с прогнозами специалистов, останется наиболее востребованным и в ближайшем будущем. Интегральные схемы этого типа обладают средним быстродействием (Fmах = 20...50 МГц) и средней потребляемой мощностью. Интегральные схемы, реализующие ЭСЛ, являются наиболее быстродействующими, но мощность, потребляемая этими элементами, превышает мощность элементов ТТЛ. Но гибкость схемотехнических решений позволяет достаточно легко реализовывать сложные логические функции. Типовые элементы И2Л разрабатывались исключительно для использования в больших интегральных схемах. Их отличием является высокая, недостижимая для ТТЛ и ЭСЛ,степень интеграции, пониженное напряжение питания, простота согласования с элементами ТТЛ и возможность регулировать в широком диапазоне быстродействие изменением потребляемой мощности. Особенностью интегральных схем, реализованных на полевых транзисторах, является малая потребляемая мощность. Но по быстродействию эти элементы будут уступать логике на биполярных транзисторах. Этот тип логики также обладает высокой помехоустойчивостью. По сравнению с биполярными, полевые транзисторы обладают меньшими размерами и проще в изготовлении, что позволяет расположить на единице площади кристалла большее количество элементов. Принимая во внимание эти особенности, область их применения ограничивается функционально сложными устройствами низкого быстродействия и малого токопотребления. Прогнозы показывают, что по мере улучшения технологии, направленной на повышение их быстродействия, этот класс интегральных схем постепенно станет самым массовым. В первую очередь это касается интегральных схем КМОП. Диодно-транзисторная логика Диодные логические элементы широко используются в конструкциях ПЛИС (программируемых логических интегральных схем). Диодная схема логического элемента И, таблица истинности и условное графическое обозначение показаны на рис. 3.1  Рис. 3.1. Диодная схема логического элемента И При условии присутствия хотя бы на одном из входов схемы логического нуля (уровень 0 В) Uвых= 0,7 В (т.е. логический ноль). Если же на все входы подается логическая единица, то все диоды будут закрыты и Uвых=Епит (т.е.логическая единица). Транзисторно-транзисторная логика На рис. 3.3 показана схема ТТЛ с простым инвертором, выполняющая логическую функцию И-НЕ, и её условное графическое обозначение.  Рис. 3.3. Схема ТТЛ с простым инвертором Если в схеме на рис. 3.3 на входы А и В подается логический ноль, то транзистор V1переходит в режим насыщения, так как Rк = ∞. Напряжение на коллекторе транзистораV1приблизительно соответствует нулю, поэтому транзистор V2 закрывается и на его выходе устанавливается напряжение, равное +Еп, т.е. логическая единица. Логическая единица сохраняется и при наличии только на одном из входов А или В логического нуля. При подаче на оба входа логической единицы, т.е. напряжения +5 В, эмиттерно-базовые переходы транзистора V1 закрываются, и электрический ток через резистор R1проходит в базу транзистораV2. На выходе транзистора V2 устанавливается логический ноль, так как транзистор V2 открывается и насыщается. При отсутствии в данной схеме резистора R2 она является схемой с открытым коллектором Интегральная инжекционная логика Интегральная инжекционная логика применяется в конструкциях СБИС (сверхбольших интегральных схем). Последовательность из двух инверторов И2Л имеет вид, представленный на рис. 3.11.  Рис. 3.11. Последовательность из двух инверторов И2Л В схеме на рис. 3.11 через транзисторы V1и V2 (называемыми инжекторами) протекает постоянный электрический ток, определяемый смещением напряжения питания Е. Этот ток устанавливается равным от 1нА до 30 мкА. При этом напряжение питания равно0,5–0,6 В. Направление протекания этого тока зависит от входного сигнала. Если UВХ=0, то ток IV1 втекает в источник входного сигнала. Транзистор V3является закрытым, поэтому ток IV2 втекает в базу транзистора V4. При этомUкV3 = 0,7В, аUкV4=0 В. Эмиттерно-связанная логика Микросхемы эмиттерно-связанной логики (ЭСЛ) являются самыми быстродействующими из всех типов логик, и обеспечивается это за счет целого ряда особенностей этой логики. Главная особенность эмиттерно-связанной логики (ЭСЛ), повышающая ее быстродействие, заключается в том, что схема ее логического элемента основана на дифференциальном усилителе (балансном каскаде), дифференциальном переключателе тока, два транзистора которого переключают ток и не попадают в режим насыщения. Благодаря этому значительно сокращается время выхода транзисторов логического элемента из открытого состояния и существенно повышается общее быстродействие. На рис. 3.5 приведена принципиальная схема базового логического элемента ЭСЛ, выполняющий функцию ИЛИ-НЕ. На транзисторах VT1, VT2 и VT3 выполнен токовый переключатель, обеспечивающий получение логических функций ИЛИ-НЕ на коллекторе VT2 и ИЛИ на коллекторе VT3. В качестве источника тока в эмитторной цепи транзисторов VT1, VT2 и VT3 используется высокоомный резистор R5. Величина тока, задаваемая этим источником, и сопротивления резисторов R3 и R4 подбираются такими, чтобы исключить режим насыщения транзисторов в открытом состоянии независимо от разброса усиления этих транзисторов, что невозможно обеспечить в обычных ТТЛ сериях (а также в рассматриваемых ниже элементах на КМОП транзисторах). На транзисторе VT4 и диодах VD1 и VD2 выполнен источник опорного напряжения. Это напряжение, уровень которого находится примерно посередине между уровнями, соответствующими логическим 0 и 1, подается на базу транзистора VT3. Поэтому транзистор VT3 будет закрыт, если хотя бы на один из входов подано напряжение более высокого уровня (лог. 1) и открыт, если на всех входах имеется напряжение низкого уровня (лог. 0). Логическая информация с коллекторов VT2 и VT3 с целью увеличения нагрузочной способности логического элемента поступает на базы выходных эмиттерных повторителей, выполненных на транзисторах VT5 и VT6. Эмиттерные повторители также осуществляют смещения уровней выходных напряжений для совместимости логических элементов этой серии по входу и выходу.  Схема элемента ИЛИ-НЕ эмиттерно-связанной логики Интегрально-инжекционная логика Структуры интегрально-инжекционной логики (И2Л структуры) широко используются в маломощных запоминающих устройствах, микропроцессорах и ИС с высокой степенью интеграции. Простейшая схема инвертора на биполярном транзисторе приведена на рис.  Логическому нулю напряжения на входе транзистора соответствует логическая единица на выходе и наоборот. В И2Л структуре входной резистор заменяется генератором тока (транзистор Т1), поставляющим носители в базу выходного транзистора Т2. Коллекторы выходного транзистора разведены для выполнения логических функций. Принципиальная схема инвертора (вентиля) приведена на рис.  Поперечное сечение вентиля И2Л на заключительном этапе технологического процесса показано на рис.  Основной логический элемент сформирован путем объединения горизонтального транзистора Т1 p-n-p типа с вертикальным транзистором n-p-n типа, который имеет несколько коллекторов, предназначенных для выполнения независимых логических операций в различных частях схемы. Коллектор транзистора Т1 служит базой транзистора Т2, а скрытый n+ слой Т2 используется как база Т1. Легко видеть, что эти конструктивные особенности совместно с ликвидацией резистора существенно повышают степень интеграции схем. Выходной транзистор работает в инверсном режиме. При Uвх= 0 носители в базу транзистора Т2 не поступают и на его выходе наблюдается высокий уровень сигнала. В случае высокого уровня входного сигнала Uвх |