лаба. ЦС лаб8. Схема счетчика на гарвардском архитектуре процессора

Скачать 43.24 Kb. Скачать 43.24 Kb.

|

|

Некоммерческое акционерное общество Алматинский университет энергетики и связи имени Гумарбека Даукеева Институт информационных технологий Кафедра Информационных систем и кибербезопасности Лабораторная работа №8 Дисциплина: Цифровая Схемотехника Тема: Схема счетчика на гарвардском архитектуре процессора Образовательная программа: 6B06301 – “Системы информационной безопасности” Выполнила: М.Нуртас Группа: СИБ-20-4 Принял: Камбаров Д. _______ ________________ «____» ________________2022г. (оценка) (подпись) (дата) Алматы 2022 Содержание:

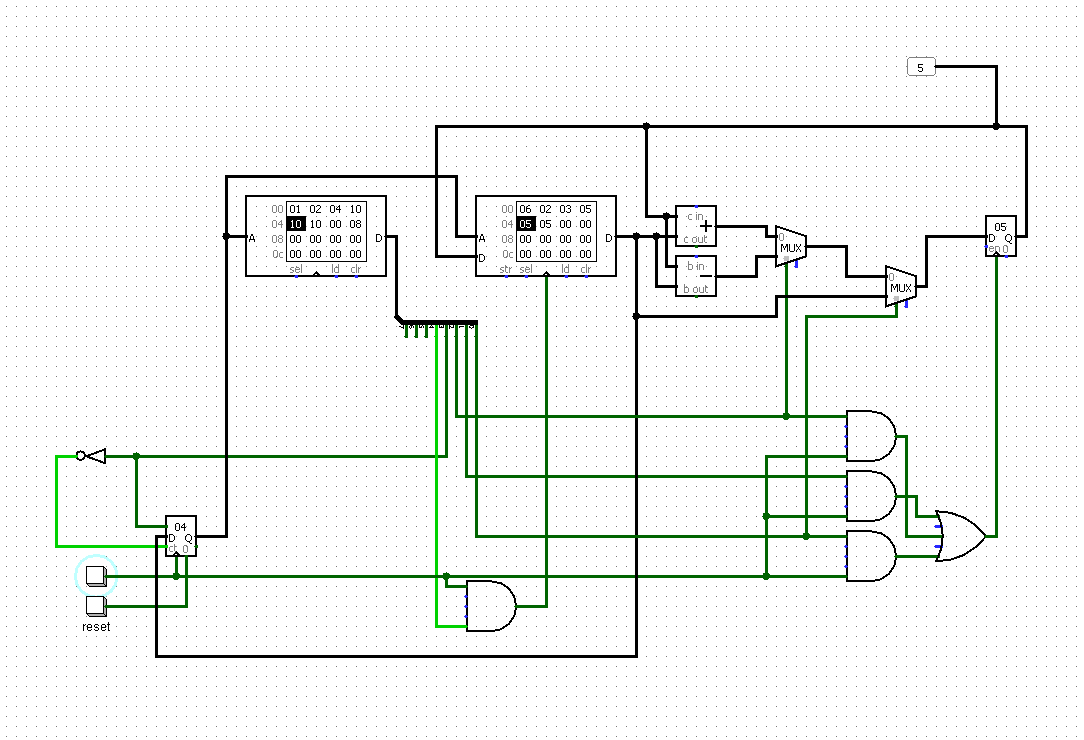

Введение Гарвардская архитектура была разработана Говардом Эйкеном в конце 1930-х годов в Гарвардском университете с целью увеличить скорость выполнения вычислительных операций и оптимизировать работу памяти. Она характеризуется физическим разделением памяти команд (программ) и памяти данных. В ее оригинальном варианте использовался также отдельный стек для хранения содержимого программного счетчика, который обеспечивал возможности выполнения вложенных подпрограмм. Каждая память соединяется с процессором отдельной шиной, что позволяет одновременно с чтением-записью данных при выполнении текущей команды производить выборку и декодирование следующей команды. Благодаря такому разделению потоков команд и данных и совмещению операций их выборки реализуется более высокая производительность, чем при использовании Принстонской архитектуры. Задание На программе Logisim постройте схему счетчика на гарвардском архитектуре процессора. Сделайте скрины и подготовьте отчет по стандарту АУЭС.  Рисунок №1 – Построение схемы счетчика на гарвардском архитектуре процессора Вывод После выполнения лабораторной работы №8 я исследовал принцип работы гарвардской архитектуры процессора, а также смог построить схему счетчика на гарвардской архитектуре процессора в программе Logisim. |