Инд вопр 5. Шурубей Анастасия авт907

Скачать 30.71 Kb. Скачать 30.71 Kb.

|

|

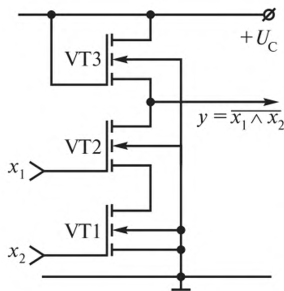

Шурубей Анастасия АВТ-907 Индивидуальный вопрос № 15 к л/р Интегральные логические схемы Базовый логический элемент 2И -НЕ на МОП транзисторах.  Рис.1 Схема логического элемента 2И-НЕ на МОП транзисторах Для реализации схемотехнического решения логического элемента И-НЕ в схему добавляют ключевые транзисторы, соединяя их последовательно между собой и с нагрузочным транзистором. Нагрузочный транзистор VT3 является общим для всех ключевых транзисторов. Такое соединение образует так называемое ярусное включение транзисторов. В схеме логического элемента И-НЕ только при подаче высоких потенциалов U1 на оба входа х1 и х2 в транзисторах VT1 и VT2 создаются каналы, и транзисторы открываются, и на стоке транзистора VT2 образуется низкий потенциал (лог.О), равный удвоенному остаточному напряжению стока-истока транзисторов VT1 и VT2. Остаточное напряжение создается от небольшого падения напряжения на каналах транзисторов при протекании через канал тока. Если же хотя бы на одном из входов, например, х потенциал будет низким U0>? /пор (Uuoр — пороговое напряжение, т.е. напряжение между затвором и подложкой, при котором возникает канал), то транзистор VT1 закрывается и ток в цепи VT1—VT3 отсутствует. Выходное напряжение при этом определяется соотношением сопротивления утечки транзисторов и достаточно близко к напряжению питания (+UC), а на выходе схемы — сигнал лог.1, т.е. Анализ работы схемы позволяет сделать вывод о том, что на сигналах лог. 1 выполняется логическая операция И-НЕ, а на сигналах лог.О — операция ИЛИ-HE. Это еще раз подтверждает то, что схемотехническое решение соответствует логическому элементу И-НЕ. |