СОЗДАНИЕ ПРОСТЕЙШЕЙ СХЕМЫ С ПОМОЩЬЮ QUARTUS 2. CХЦУ_ЛР1. Создание простейшей схемы с помощью Quartus 2

Скачать 130.51 Kb. Скачать 130.51 Kb.

|

|

МИНОБРНАУКИ РОССИИ Санкт-Петербургский государственный электротехнический университет «ЛЭТИ» им. В.И. Ульянова (Ленина) Кафедра РС отчет по лабораторной работе №1 по дисциплине «Цифровая электроника» Тема: «Создание простейшей схемы с помощью Quartus 2» Вариант 15

Санкт-Петербург 2022 Цель работы. Познакомиться с пакетом Quartus 2. Изучить основы построения и написания кода для логических схем. Задание. Вариант 15. Исследование работы цифрового устройства, описываемого следующим логическим выражением:   Ход работы. Построим таблицу истинности для заданного выражения:

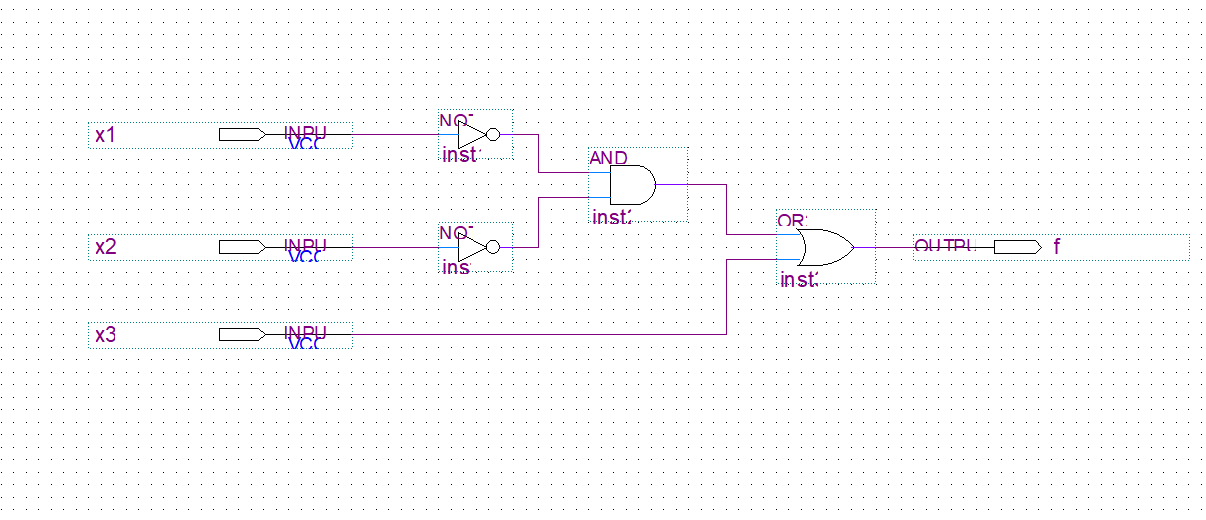

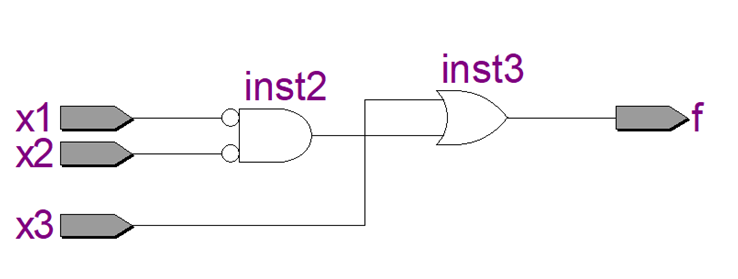

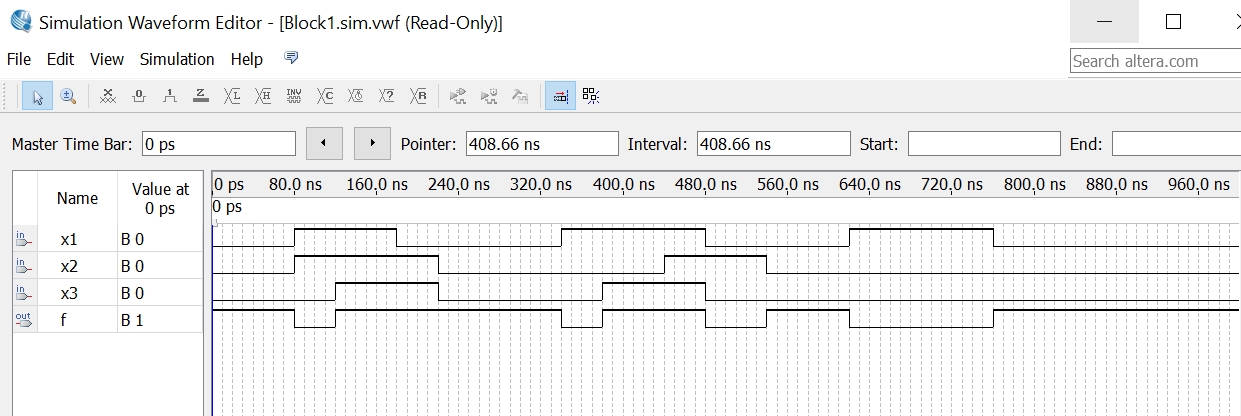

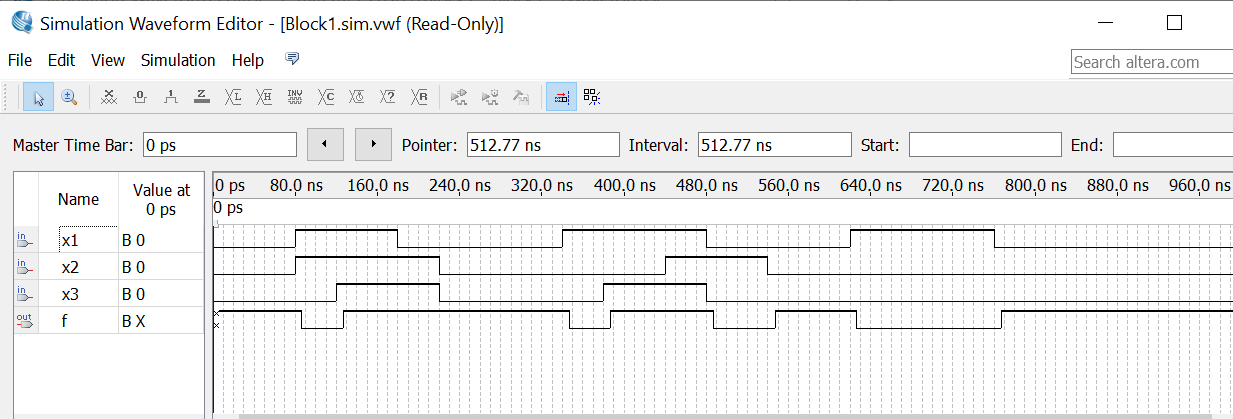

Изобразим схему в графическом редакторе в соответствии с заданным выражением. В схеме мы имеем 3 входа и 1 выход.  Рисунок 1. Схема в графическом редакторе. Убедимся в том, что пакет правильно интерпретирует схему. Для этого перейдем в RTL Viewer и заметим, что у нас имеется 3 входа и 1 выход, следовательно программой было все верно воспринято.  Рисунок 2. Схема устройства в RTL Viewer. На рисунке 2, кружочки находящиеся до операции &- логическое «и», обозначают то, что первым действием мы учитываем операцию  -«инверсия» (not) , и только потом выполняем последующие операции, в нашем случае операцию -«инверсия» (not) , и только потом выполняем последующие операции, в нашем случае операцию  (or) логическое «или». (or) логическое «или».Построим временную диаграмму без учета задержек .  Рисунок 3. Осциллограмма собранной схемы На рисунке 3, в построенной временной диаграмме, задержки между входным и выходным сигналами отсутствуют. Построим временную диаграмму без учета задержек. Для этого, предварительно выполним полную компиляцию. В результате чего, получим временную диаграмму с учетом задержек:  Рисунок 4. Осциллограмма собранной схемы с учетом задержек На рисунке 4, мы можем наблюдать задержки между входными и выходным сигналами. Вывод: в ходе лабораторной работы были получены базовые навыки владения программой Quartus II. Была создана схема заданной функции в графическом редакторе, построены осциллограммы работы схемы с учётом задержки и без неё. Полученный результат проверен с помощью построения таблицы истинности. |