шпоры эпиу. Усилители. Параметры и характеристики усилителей

Скачать 5.58 Mb. Скачать 5.58 Mb.

|

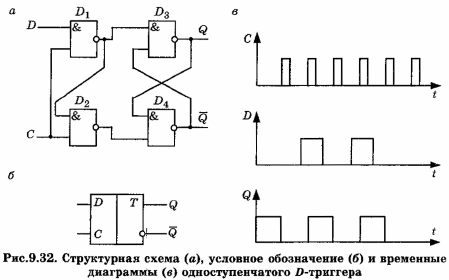

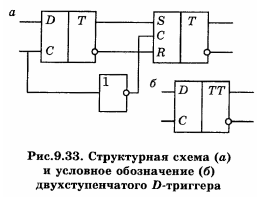

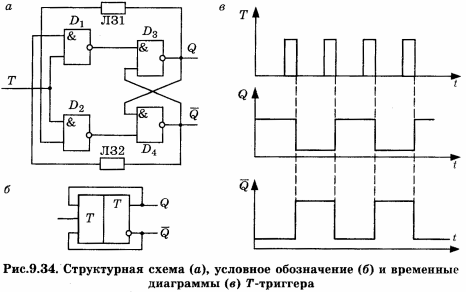

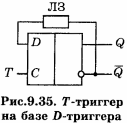

44. D-триггерТриггером называется устройство, имеющее два устойчивых состояния и способное под действием управляющих сигналов скачкообразно переходить из одного состояния в другое. Триггер имеет два устойчивых состояния 0 и 1 и два выхода: прямой Q и инверсный Q. Когда Q = 0, Q = 1 триггер находится в нулевом состоянии, при Q = 1, Q = 0 триггер – в единичном состоянии. D–ТРИГГЕРЫ. D–триггером называется триггер с одним информационным входом, работающий так, что сигнал на выходе после переключения равен сигналу на входе D до переключения (Qn+1=Dn). Основное назначение D–триггера – задержка сигнала, поданного на вход D. Информационный сигнал (0 или 1), поступающий на вход D, задерживается в триггере на время, равное одному периоду следования синхроимпульсов, прежде чем появится на прямом выходе Q. На практике наибольшее применение получили тактируемые (однотактные и двухтактные) D–триггеры. Они имеют информационный вход D (вход данных) и вход синхронизации С. Вход синхронизации C может быть статическим (потенциальным) и динамическим. У триггеров со статическим входом C информация записывается в течение времени, при котором уровень сигнала С = 1. В триггерах с динамическим входом С информация записывается только в течение перепада напряжения на входе С. Динамический вход изображают на схемах треугольником. Если триггер срабатывает по фронту входного сигнала, то вершина треугольника обращена в сторону микросхемы (прямой динамический вход). Если триггер срабатывает по срезу импульса, то вершина треугольника обращена от микросхемы (инверсный динамический вход).  На рис. 9.32 приведена структурная схема, условное обозначение и временные иаграммы одноступенчатого (однотактового) D–триггера на элементах И–НЕ. На элементах D1 и D2 выполнена схема управления, а на элементах D3, и D4 – асинхронный RS–триггер. Если уровень сигнала на синхровходе С = 0, то состояние триггера устойчиво и не зависит от уровня сигнала на информационном D–входе. Предположим, что Q = 1; = 0; D = 0; C = 1. При подаче на синхровход логической единицы на обоих входах логического элемента D2 будут действовать единичные сигналы. Элемент D2 открывается, а элемент D4 закрывается и Q= 1. На обоих входах логического элемента D3 действуют единичные сигналы, которые открывают его, т.е. Q=0. Итак, после переключения триггера сигнал на выходе Q стал равен сигналу на входе D до переключения. При снятии единичный сигнал с С–входа состояние триггера не изменяется. При С = 0 и при воздействии единичного сигнала на информационный вход D = 1 состояние логических элементов D1 и D2 не изменяется, триггер сохраняет предыдущее состояние. При одновременной подаче единичных сигналов на оба входа D = С = 1 элемент D1 открывается, а элемент D3 закрывается Q = 1. Элемент D4 открывается Q= 0, состояние элемента D2 не изменяется и триггер переключается. Таким образом, в триггер записывается та информация, которая была на входе D до синхронизирующего импульса. Для четкой работы триггеров необходимо, чтобы к приходу следующего импульса синхронизации потенциалы выходов логических элементов приняли значения, исключающие ложные срабатывания. Минимальный интервал между импульсами синхронизации у таких триггеров должен быть равен tмин =4tздср , а максимальная частота включения fмакс =1 tмин ; tзд ср – среднее время задержки распространения сигнала одним логическим элементом. Работа триггера поясняется временными диаграммами, представленными на рис. 9.32,в. Структура триггера не изменится, если в нем логические элементы И–НЕ заменить на элементы ИЛИ–НЕ. При этом прямой выход станет инверсным, а инверсный – прямым. Функциональная схема и условное обозначение двухступенчатого D–триггера показано на рис. 9.33. Он состоит из двух последовательно включенных синхронных RS–триггеров, первый из которых называется ведущим (master) или M–триггером, а второй ведомым (slaver) или S–триггером. За счет наличия общего синхросигнала С вся схема работает как единое целое. В связи с этим схема называется двухступенчатой или MS–триггером. При C = 1 происходит переключение M–триггера согласно сигналу на входе D. S–триггер в это время заблокирован, так как у него на входе C = 0. Если на С–входе действует нулевой потенциал, то C–триггер переключается и устанавливается в то же со- стояние, что и M -триггер.  45. Т-триггерТриггером называется устройство, имеющее два устойчивых состояния и способное под действием управляющих сигналов скачкообразно переходить из одного состояния в другое. Триггер имеет два устойчивых состояния 0 и 1 и два выхода: прямой Q и инверсный Q. Когда Q = 0, Q = 1 триггер находится в нулевом состоянии, при Q = 1, Q = 0 триггер – в единичном состоянии. Т–ТРИГГЕР. Триггером T––типа (счетным триггером) называют логическое устройство с двумя устойчивыми состояниями и одним входом T, которое остается в исходном состоянии при Т = 0 и инвертирует свое исходное состояние при Т = 1. Основным способом построения счетных триггеров является введение соответствующих обратных связей в синхронизируемые RS– и D–триггеры. На рис. 9.34 показана структурная схема, условное обозначение и временные диаграммы T–триггера, собранного на базе синхронного RS–триггера, у которого прямой выход Q соединяется с S–входом, а инверсный выход Q соединяется со входом R. В T–триггере имеются дополнительные обратные связи на входы вентилей D1 и D2, подключенные через линии задержки ЛЗ1 и ЛЗ2. Назначение этих линий – задержка поступления сигналов обратной связи на вход инверторов до окончания входного сигнала. В качестве линии задержки используется один или два логических элемента. Их задержки распространения сигнала бывает достаточно для четкой работы T–триггеров, выполненных на микросхемах любых типов.  Для реализации T–триггера часто используют схему D–триггера с динамической синхронизацией, у которого инверсный выход Q соединяется с D–входом. Информационный сигнал подают на С–вход (рис. 9.35). Пусть на D–входе действует сигнал логической единицы, при переключении С–входа с уровня логического нуля до уровня логической единицы триггер переходит в единичное состояние Q = 1. Потенциалы на выходе Q и на D–входе равны логическому нулю. Последующий перепад напряжения с нуля до единицы на C–входе установит триггер в нулевое состояние. Потенциал на D–входе станет равным логической единице. Состояние триггера меняется на противоположное при каждом перепаде импульса напряжения на C–входе, триггер как бы считает проходящие импульсы. В сериях выпускаемых микросхем T–триггеров нет. Они строятся на базе синхронизируемых RS– и D–триггеров. Для реализации T–триггера часто используют схему D–триггера с динамической синхронизацией, у которого инверсный выход Q соединяется с D–входом. Информационный сигнал подают на С–вход (рис. 9.35). Пусть на D–входе действует сигнал логической единицы, при переключении С–входа с уровня логического нуля до уровня логической единицы триггер переходит в единичное состояние Q = 1. Потенциалы на выходе Q и на D–входе равны логическому нулю. Последующий перепад напряжения с нуля до единицы на C–входе установит триггер в нулевое состояние. Потенциал на D–входе станет равным логической единице. Состояние триггера меняется на противоположное при каждом перепаде импульса напряжения на C–входе, триггер как бы считает проходящие импульсы. В сериях выпускаемых микросхем T–триггеров нет. Они строятся на базе синхронизируемых RS– и D–триггеров. 46.JK-триггерТриггером называется устройство, имеющее два устойчивых состояния и способное под действием управляющих сигналов скачкообразно переходить из одного состояния в другое. Триггер имеет два устойчивых состояния 0 и 1 и два выхода: прямой Q и инверсный Q. Когда Q = 0, Q = 1 триггер находится в нулевом состоянии, при Q = 1, Q = 0 триггер – в единичном состоянии. JK–ТРИГГЕРЫ. JK–триггер имеет два информационных входа J и K. По входу J триггер устанавливается в состояние Q = 1, Q= 0, а по входу K – в состояние Q = 0, Q = 1. JK–триггеры подразделяются на универсальные и комбинированные. Универсальность JK–триггера состоит в том, что при соответствующем подключении информационных входов он может выполнять функции RS–, D–, T–триггеров. Комбинированный JK–триггер отличается от универсального наличием дополнительных асинхронных входов S и R, предназначенных для предварительной установки триггера в определенное состояние (логической единицы или нуля). Простейший JK–триггер можно получить из синхронного RS–триггера, введя дополнительные обратные связи с выходов триггера на входы (рис. 9.36). Такой триггер не имеет запрещенных комбинаций входных сигналов, и при J = K = 1 осуществляется инверсия предыдущего состояния (табл. 9.6). При J = K = 0 и при наличии синхросигнала на входе С состояние триггера не изменяется, так как сигнал логического нуля на одном входе элемента И–НЕ отменяет прохождение сигналов от других входов, и на выходе имеется сигнал логической единицы. Для перевода триггера в единичное состояние необходимо одновременное присутствие сигналов на C– и J– входах. При подаче на входы J и K одновременно напряжений логической единицы и наличии синхросигнала триггер переключается в состояние, противоположное предыдущему. Если соединить вместе J– и K–входы, то триггер станет счетным и превратится в T–триггер. Если ввести инвертор в цепь входа K, то JK–триггер превращается в D–триггер.  |