шпоры эпиу. Усилители. Параметры и характеристики усилителей

Скачать 5.58 Mb. Скачать 5.58 Mb.

|

|

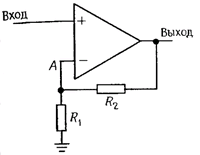

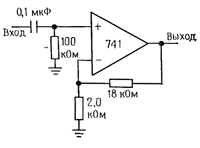

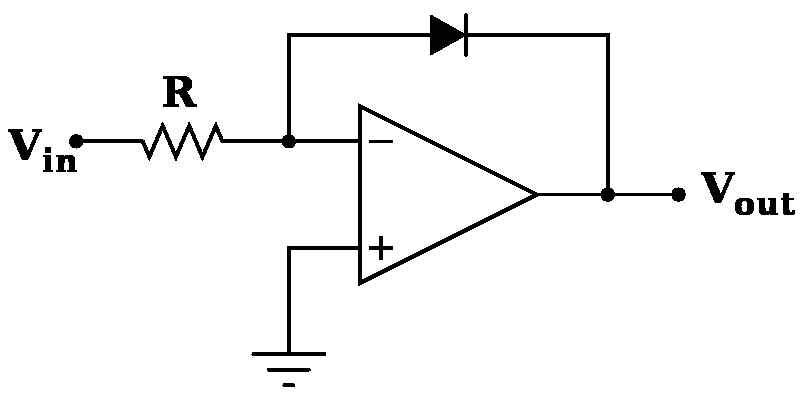

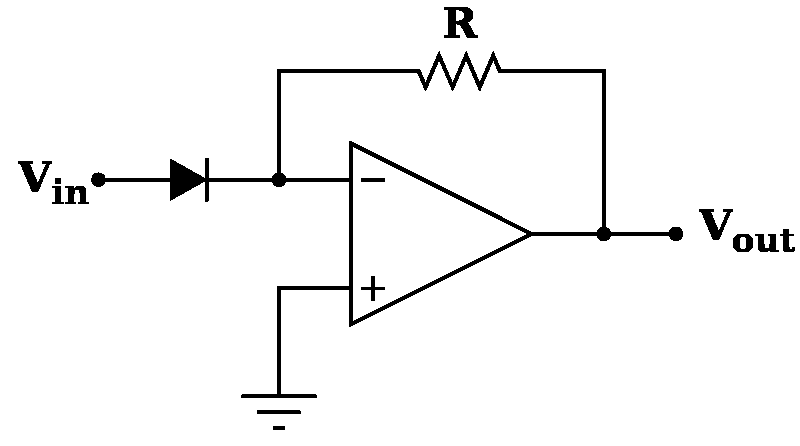

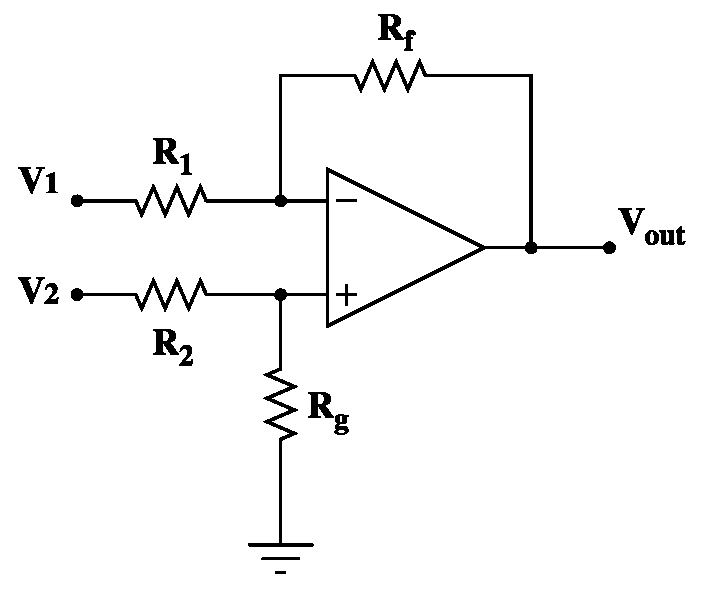

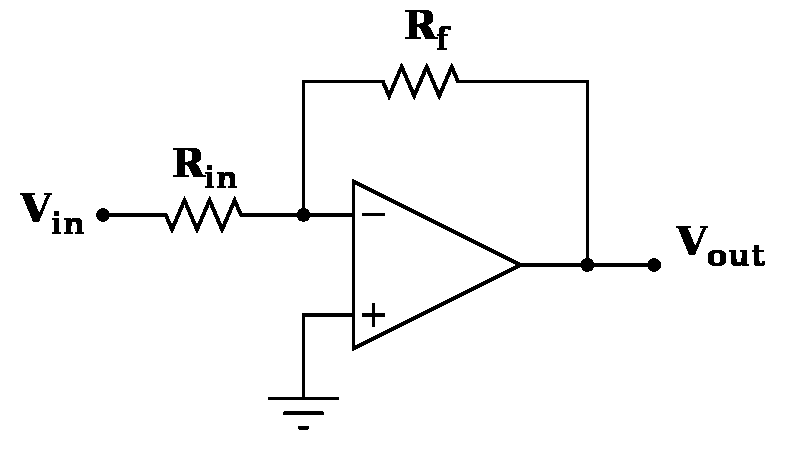

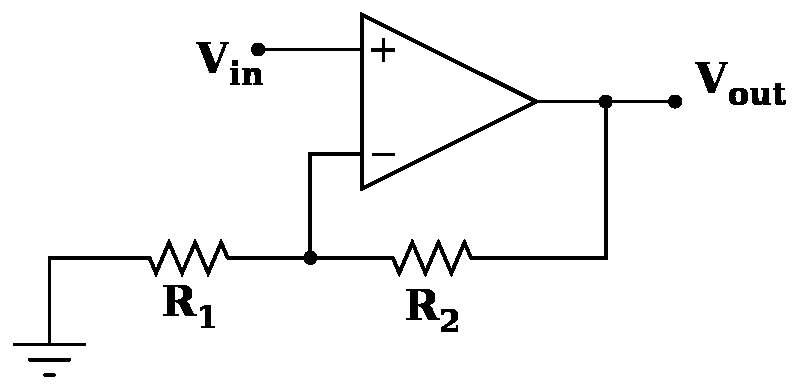

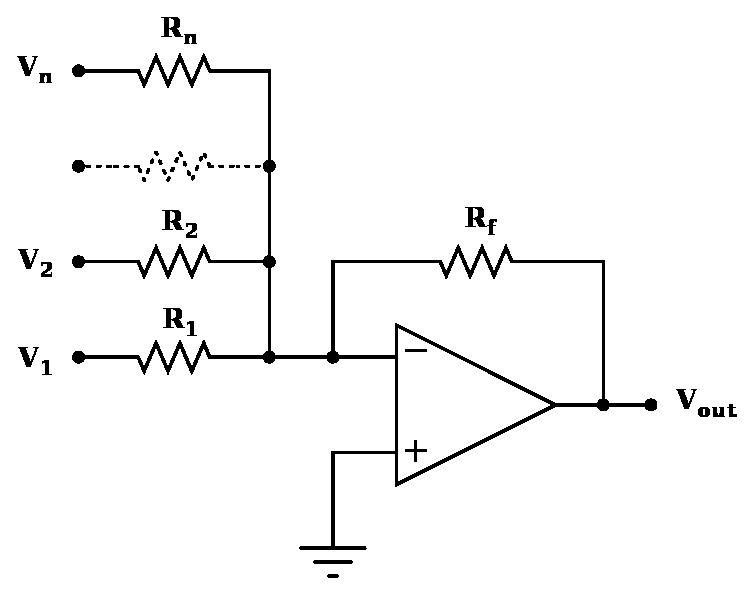

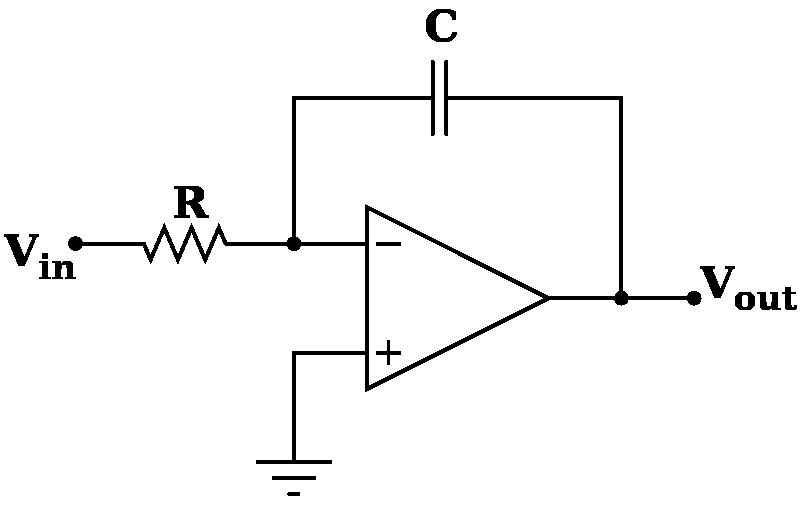

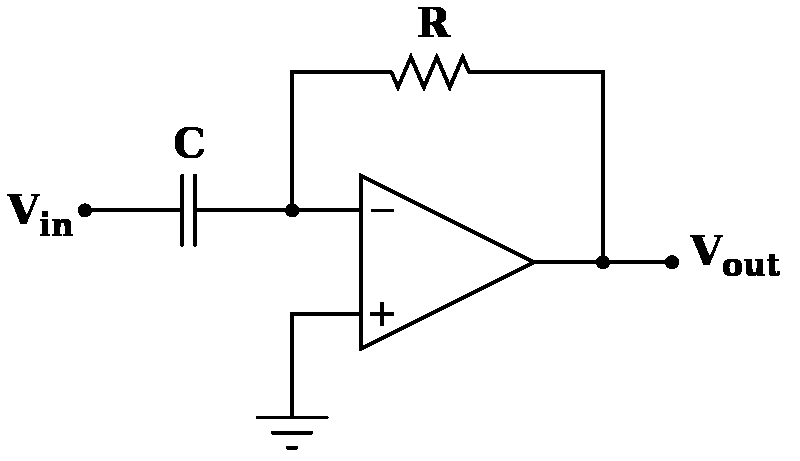

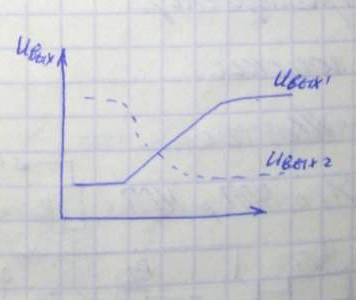

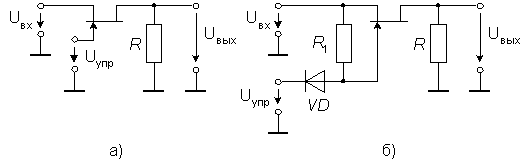

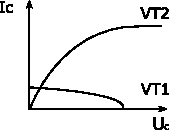

75. Неинвертирующий усилитель Рассмотрим схему на рис. 4.5. Анализ ее крайне прост: UA = Uвх. Напряжение UA снимается с делителя напряжения: UA = UвыхR1/(R1 + R2). Если UA = Uвх, то коэффициент усиления = Uвых/Uвх = 1 + R2/R1. Это неинвертирующий усилитель. В приближении, которым мы воспользуемся, входной импеданс этого усилителя бесконечен (для ОУ типа 411 он составляет 10^12 Ом и больше, для ОУ на биполярных транзисторах обычно превышает 10^8 Ом). Выходной импеданс, как и в предыдущем случае, равен долям ома. Если, как в случае с инвертирующим усилителем, мы внимательно рассмотрим поведение схемы при изменении напряжения на входах, то увидим, что она работает, как обещано.  Рис. 4.5. Эта схема также представляет собой усилитель постоянного тока. Если источник сигнала и усилитель связаны между собой по переменному току, то для входного тока (очень небольшого по величине) нужно предусмотреть заземление, как показано на рис. 4.6. Для представленных на схеме величин компонентов коэффициент усиления по напряжению равен 10, а точке - 3 дБ соответствует частота 16 Гц.  Рис. 4.6. 76. Применение ОУ для выполнения нелинейных операций Логарифмический усилитель  Отношение между входным и выходным напряжениями представлено следующей формулой: где - ток насыщения. Предположив, что операционный усилитель идеальный и инвертирующий вход виртуально заземлен, то ток, протекающий через резистор от источника (и далее через диод на выход, таким образом, через входы операционного усилителя ток не протекает) описывается следующей формулой: где - ток, протекающий через диод. Как известно, отношение между током и напряжением для диода: Когда напряжение больше нуля, эта формула может быть преобразована в: Рассмотрение этих двух формул вместе и предположение, что выходное напряжение является обратным по отношению к напряжению на диоде, является доказательством формулы. Расчеты не учитывают температурную стабильность и другие эффекты, присущие реальным устройствам. Антилогарифмический усилитель Антилогарифмический (экспоненциальный) усилитель имеет обратную логарифмическую передаточную характеристику. Для получения таких схем достаточно в приведенной схеме логарифмического усилителя поменять местами диод и резистор:  Зависимость выходного напряжения от входного: 77. Применение ОУ для выполнения математических операций Дифференциальный усилитель (вычитатель)  Данная схема предназначена для получения разности двух напряжений, при этом каждое из них предварительно умножается на некоторую константу (константы определяются резисторами). Инвертирующий усилитель  Инвертирует и усиливает напряжение (то есть умножает напряжение на отрицательную константу). Неинвертирующий усилитель  Усиливает напряжение (умножает напряжение на константу, большую единицы) Инвертирующий суммирующий усилитель (инвертирующий сумматор)  Суммирует (с весом) несколько напряжений. Сумма на выходе инвертирована, то есть все веса отрицательны. Интегратор  Интегрирует (инвертированный) входной сигнал по времени. Дифференциатор  Дифференцирует (инвертированный) входной сигнал по времени. где и — функции времени. 78. Электронные ключи. Параметры и характеристики Электронными ключами называют устройства, предназначенные для замыкания или размыкания электрических цепей под действием внешних управляющих сигналов. В бесконтакгных электронных ключах используются нелинейные элементы: полупроводниковые диоды. биполярные и полевые транзисторы, гиристоры. В отличие от механических переключателей электронные ключи обладают большим быстродействием и надежностью. В зависимости от назначения ключевые схемы бывают: цифровые и аналоговые. Цифровые ключи используются в устройствах вычислительной техники, цифровой связи. дискретной автоматики. Аналоговые ключи используются в аналого-цифровых и цифроаналоговых преобразователях. в устройствах измерения и управления. в многоканальных коммутаторах, Различают статический режим работы ключа, когда он находится в закрытом или открытом состоянии, и динамический режим, соответствующий переключению из закрытого состояния в открытое и наоборот. Каждый из режимов работы описывается определенным набором характеристик и параметров. Параметры статического режима электронного ключа определяются его передаточной характеристикой, которая устанавливает зависимость выходного напряжения от входного Основными параметрами статического режима являются (см. рис.8.2): пороговое напряжение нуля   Динамический режим ключа описывается параметрами быстродействия, которые определяются скоростью переходных процессов, возникающих в устройстве при подаче на вход прямоугольного импульса (рис. 8.5). Быстродействие ключа определяется параметрами используемого активного элемента – транзистора, номинальных значений элементов схемы, характера и параметров нагрузки. Различают следующие параметры быстродействия: время задержки д время включения – г  время рассасывания длительность спада – интервал времени, в течение которого ток коллектора уменьшается от уровня  время выключения – г 79. Ключ на биполярном транзисторе   Имеются три характерные области работы транзистора: область выключения (отсечки) I, область активного режима II и область включения (насыщения) III. В ключевых схемах транзистор находится в активном режиме лишь в переходном состоянии. Статические параметры ключа: остаточное напряжение U во включенном состоянии (точка В) и остаточный ток в выключенном (запертом) состоянии (точка А). В точке А напряжение на электродах практически совпадает с эдс источника питания. В точке В токи электродов определяются параметрами внешних цепей: Процесс выключения транзистора начинается, когда на базу подаётся запирающее напряжение. В момент переключения на обоих p-n – переходах сохраняются прямые смещения, близкие к U*. При этом коллекторный ток не меняется и остаётся равным Iкн . Базовый ток принимает значение: Общая инерционность транзисторного ключа характеризуется временами включения tвкл и выключения tвыкл : Усовершенствованные ключи на биполярном транзисторе. Схема с дополнительным источником смещения.   Схема с ускоряющей емкостью   Схема с нелинейной обратной связью   80. Ключ на переключателе тока   81. Ключи на полевых транзисторах. Полевой транзистор в области малых напряжений сток-исток ведет себя как резистор, сопротивление которого может изменяться во много раз при изменении управляющего напряжения затвор-исток Uзи. На рис изображена упрощенная схема последовательного ключа на полевом транзисторе с управляющим pn-переходом.  Если в этой схеме управляющее напряжение Uупр установить меньшим, чем минимально-возможное входное напряжение, по крайней мере на величину порогового напряжения транзистора, транзистор закроется и выходное напряжение станет равным нулю. Для того, чтобы транзистор был открыт, напряжение затвор-исток Uзи следует поддерживать равным нулю, что обеспечивает минимальное сопротивление канала. Если же это напряжение станет больше нуля, управляющий pn-переход откроется, и выход ключа окажется соединенным с цепью управления. Если напряжение Uупр установить большим, чем максимально-возможное входное напряжение ключа, диод VD закроется и напряжение Uзи будет, как это и требуется, равно нулю. При достаточно большом отрицательном управляющем напряжении диод будет открыт, а полевой транзистор закрыт. В таком режиме работы через резистор R1 течет ток от источника входного сигнала в цепь управляющего сигнала. Это не мешает нормальной работе схемы, так как выходное напряжение ключа в этом режиме равно нулю. Нарушение нормального режима работы такой схемы может произойти лишь в случае, если цепь входного сигнала содержит разделительный конденсатор, который при закрытом транзисторе ключа зарядится до отрицательного уровня управляющего напряжения. 82. Комплементарный ключ (КМДП) В схеме отсутствуют пассивные сопротивления.  На входах всех микросхем устанавливаются защитные цепочки. Их функции:

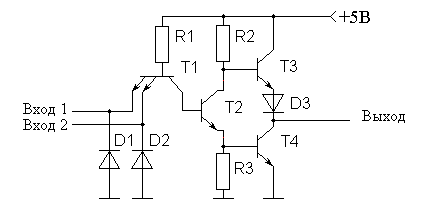

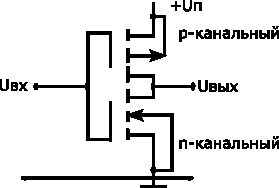

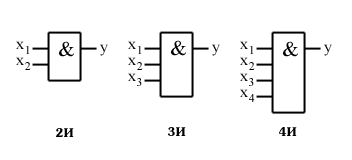

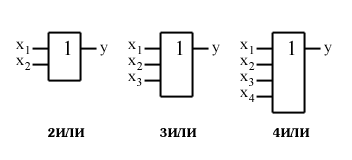

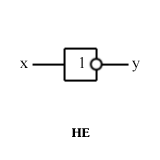

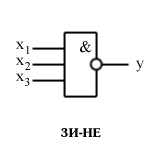

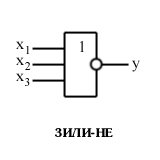

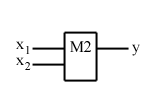

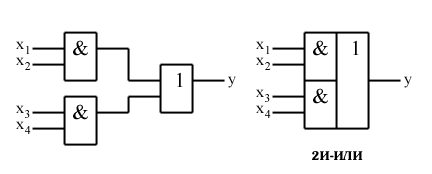

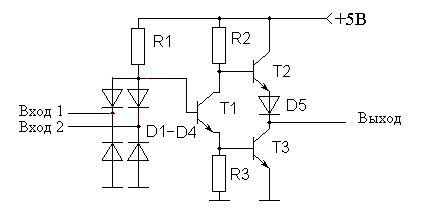

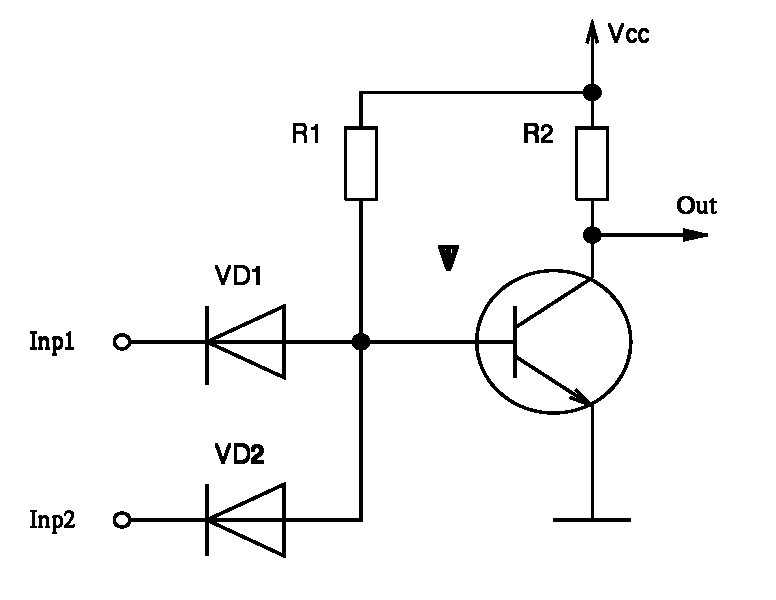

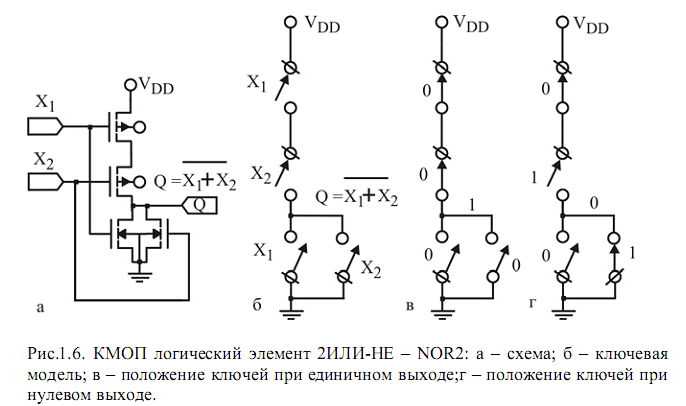

Принцип действия КМДП ключа    На входе высокий уровень. Uвх = Uвх1. VT2 открыт, VT1 закрыт. На выходе низкий уровень. Uвых практически равно нулю I ≈ 10 пА. Uвых ≈ 10мкВ. Uвх = Uвх0. На входе низкий уровень. VT2 закрыт. Транзистор отсчитывает напряжение на затворе относительно потенциала подложки. На затворе Uзvt - Uп = -5 В. Поэтому VT1 открыт. Его характеристики в этом режиме симметричны. Uвых = +5. U ≈ 10 мкВ (из-за токов утечки). КМДП ключ обеспечивает близкие к идеальному статические уровни на выходе. 83. Логические элементы. Основные параметры и особенности Логическим элементом называется электрическая схема, выполняющая какую-либо логическую операцию (операции) над входными данными и возвращающая результат операции в виде выходного уровня напряжения. Логический элемент воспринимает входные данные в виде высокого (напряжение логической 1) и низкого (напряжение логического 0) уровней напряжения на своих входах. Обычно, логические элементы собираются как отдельная интегральная микросхема. Логические операции: конъюнкция (логическое умножение, И), дизъюнкция (логическое сложение, ИЛИ), отрицание (НЕ) и сложение по модулю 2 (исключающее ИЛИ). Рассмотрим основные типы логических элементов. Параметры: - коэф-т объединения по входу - коэф разветвления по выходу Основные параметры: напряжение источника питания, уровни напряжений логического 0 и логической 1, нагрузочная способность, помехоустойчивость и быстродействие, потребляемая мощность. Элемент И Л  огический элемент И выполняет операцию логического умножения (конъюнкция) над своими входными данными и имеет от 2 до 8 входов и один выход (как правило, выпускаются элементы с двумя, тремя, четырьмя и восемью входами). На рис. 1. изображены условные графические обозначения (УГО) логических элементов И с двумя, тремя и четырьмя входами соответственно. Элементы И обозначаются как NИ, где N - количество входов логического элемента (например, 2И, 3И, 8И и т.д.). огический элемент И выполняет операцию логического умножения (конъюнкция) над своими входными данными и имеет от 2 до 8 входов и один выход (как правило, выпускаются элементы с двумя, тремя, четырьмя и восемью входами). На рис. 1. изображены условные графические обозначения (УГО) логических элементов И с двумя, тремя и четырьмя входами соответственно. Элементы И обозначаются как NИ, где N - количество входов логического элемента (например, 2И, 3И, 8И и т.д.).Э  лемент ИЛИ лемент ИЛИЛогический элемент ИЛИ выполняет операцию логического сложения (дизъюнкция) над своими входными данными и, также как и логический элемент И, имеет от 2 до 8 входов и один выход. На рис. 2. изображены УГО логических элементов ИЛИ с двумя, тремя и четырьмя входами соответственно. Элементы ИЛИ обозначаются также, как и элементы И (2ИЛИ, 4ИЛИ и т.д.). Элемент НЕ (инвертор) Л  огический элемент НЕ выполняет операцию логического отрицания над своими входными данными и имеет один вход и один выход. Иногда его называют инвертор, так как он инвертирует входной сигнал. На рис. 3 изображено УГО элемента НЕ. огический элемент НЕ выполняет операцию логического отрицания над своими входными данными и имеет один вход и один выход. Иногда его называют инвертор, так как он инвертирует входной сигнал. На рис. 3 изображено УГО элемента НЕ.Элемент И-НЕ Л  огический элемент И-НЕ выполняет операцию логического умножения над своими входными данными, а затем инвертирует (отрицает) полученный результат и выдаёт его на выход. Таким образом, можно сказать, что логический элемент И-НЕ - это элемент И с инвертором на выходе. УГО элемента 3И-НЕ приведено на рис.. огический элемент И-НЕ выполняет операцию логического умножения над своими входными данными, а затем инвертирует (отрицает) полученный результат и выдаёт его на выход. Таким образом, можно сказать, что логический элемент И-НЕ - это элемент И с инвертором на выходе. УГО элемента 3И-НЕ приведено на рис..Элемент ИЛИ-НЕ Л  огический элемент ИЛИ-НЕ выполняет операцию логического сложения над своими входными данными, а затем инвертирует (отрицает) полученный результат и выдаёт его на выход. Таким образом, можно сказать, что логический элемент ИЛИ-НЕ - это элемент ИЛИ с инвертором на выходе. УГО элемента 3ИЛИ-НЕ приведено на рис. огический элемент ИЛИ-НЕ выполняет операцию логического сложения над своими входными данными, а затем инвертирует (отрицает) полученный результат и выдаёт его на выход. Таким образом, можно сказать, что логический элемент ИЛИ-НЕ - это элемент ИЛИ с инвертором на выходе. УГО элемента 3ИЛИ-НЕ приведено на рис.Элемент сложения по модулю 2 Э  тот логический элемент выполняет логическую операцию сложения по модулю 2 и, как правило, имеет 2 входа и один выход. Такой элемент, в основном, используется в схемах аппаратного контроля. УГО элемента приведено на рис. тот логический элемент выполняет логическую операцию сложения по модулю 2 и, как правило, имеет 2 входа и один выход. Такой элемент, в основном, используется в схемах аппаратного контроля. УГО элемента приведено на рис. Комбинационные логические элементы Существуют и более сложные логические элементы, выполняющие несколько логических операций над своими входными данными. Например, элемент 2И-ИЛИ, УГО и схема которого приведено на рис., сначала выполняет операцию логического умножения над парами операндов x1, x2 и x3, x4, а затем выполняет операцию логического сложения над полученными результатами, т.е. y = x1x2 + x3x4.  Простейшие логические элементы на биполярных транзисторах. Принципиальная схема типового элемента 2И-НЕ диодно-транзисторной логики (ДТЛ) приведена на рис. 2. Если хотя бы на одном из входов (число которых может быть более двух) появляется уровень 0 (низкое напряжение), то соответствующий входной диод открывается и сигнал низкого напряжения практически закрывает транзистор Т1. При этом Т3 будет закрыт, а Т2 открыт и на выходе установится уровень 1 (высокий уровень). Для получения на выходе уровня 0 нужно, чтобы все входные диоды были закрыты, т.е. на входах должны быть уровни 1.  Рис. 2. Принципиальная схема ДТЛ Принципиальная схема типового элемента 2И-НЕ транзисторно-транзисторной логики (ТТЛ) приведена на рис. 3. В отличие от схемы ДТЛ роль входных диодов выполняют эмиттерные переходы многоэмиттерного транзистора Т1.

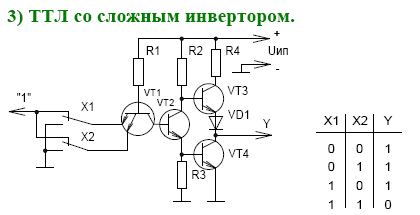

Рис. 3. Принципиальная схема ТТЛ 84. Элемент ТТЛ со сложным инвертором. Е  сли хотя бы на одном из входов будет действовать логический ноль, соответствующий эмиттерный переход будет открыт. В цепи коллектора, а следовательно, и в цепи базы ток будет отсутствовать, будет находиться в режиме отсечки, ток через транзистор, а значит, ток базы будут близки к нулю. Транзистор также будет находиться в режиме отсечки, и на выходе будет высокий уровень напряжения логической единицы. При этом напряжение на коллекторе и на базе будет максимальным, и будет находиться в полностью открытом состоянии.При подаче на оба входа логических единиц оба эмиттерных перехода закрываются, и ток будет протекать по цепи от плюса, через R1, переход база-коллектор на базу. Транзистор VT2 перейдёт в режим насыщения. Ток через него, а следовательно, и ток базы будет максимальным, и транзистор VT4 перейдёт в режим насыщения. На выходе будет низкий уровень логического нуля. При этом напряжение на коллекторе VT2 и на базе будет близко к нулю и перейдёт в полностью закрытое состояние. Диод VD1 применяется для более надёжного запирания транзистора VT3 сли хотя бы на одном из входов будет действовать логический ноль, соответствующий эмиттерный переход будет открыт. В цепи коллектора, а следовательно, и в цепи базы ток будет отсутствовать, будет находиться в режиме отсечки, ток через транзистор, а значит, ток базы будут близки к нулю. Транзистор также будет находиться в режиме отсечки, и на выходе будет высокий уровень напряжения логической единицы. При этом напряжение на коллекторе и на базе будет максимальным, и будет находиться в полностью открытом состоянии.При подаче на оба входа логических единиц оба эмиттерных перехода закрываются, и ток будет протекать по цепи от плюса, через R1, переход база-коллектор на базу. Транзистор VT2 перейдёт в режим насыщения. Ток через него, а следовательно, и ток базы будет максимальным, и транзистор VT4 перейдёт в режим насыщения. На выходе будет низкий уровень логического нуля. При этом напряжение на коллекторе VT2 и на базе будет близко к нулю и перейдёт в полностью закрытое состояние. Диод VD1 применяется для более надёжного запирания транзистора VT385. ДТЛ-логика Диодно-транзисторная логика (ДТЛ), англ. Diode–transistor logic (DTL) — технология построения цифровых схем на основе биполярных транзисторов, диодов и резисторов. Своё название технология получила благодаря реализации логических функций (например, 2И) с помощью диодных цепей, а усиления и инверсии сигнала — с помощью транзистора (для сравнения см. резисторно-транзисторная логика и транзисторно-транзисторная логика). Принцип работы  Показанная на рисунке схема представляет собой типичный элемент 2ИЛИ-НЕ. Если хотя бы на одном из входов уровень логического нуля, то ток течет через R1 и диод во входную цепь. На анодах диодов напряжение 0,7 В, которого недостаточно для открывания транзистора. Транзистор закрыт. На выходе формируется уровень логической единицы. Если на все входы поступает уровень логической единицы, ток течет через R1 на базу транзистора, образуя на анодах диодов напряжение 1,4 В. Поскольку напряжение уровня логической единицы больше этой величины, входы диодов обратносмещены и не участвуют в работе схемы. Транзистор открыт в режиме насыщения. В транзистор втекает ток нагрузки, по величине значительно больший тока нагрузки в состоянии логической единицы. Преимущества и недостатки Основное преимущество ДТЛ перед более ранней технологией РТЛ — возможность создания большого числа входов. Задержка прохождения сигнала по-прежнему достаточно высока, из-за медленного процесса утечки заряда с базы в режиме насыщения (когда все входы имеют высокий уровень) при подаче на один из входов низкого уровня. Эту задержку можно уменьшить подключением базы транзистора через резистор к общему проводу или к источнику отрицательного напряжения. В более современной и эффективной технологии ТТЛ данная проблема решена путём замены диодов на мультиэмиттерный транзистор. Это также уменьшает площадь кристалла (в случае реализации в виде интегральной схемы), и соответственно позволяет добиться более высокой плотности элементов. Однако в ещё более современных и эффективных микросхемах ТТЛ (74S, 74LS, 74AS, 74ALS, 74F) с диодами Шоттки (ТТЛШ, ТТЛ Шоттки), фактически произошёл возврат к ДТЛ, на основе новой технологии — диодах и транзисторах Шоттки. Эти серии многоэмиттерного транзистора не содержат, фактически являются ДТЛ, и носят название ТТЛ (ТТЛШ) лишь «по традиции», будучи развитием именно ДТЛ. Применение Логические элементы на основе ДТЛ являлись основой для многих ЭВМ второго поколения, например БЭСМ-6, IBM 1401, и др. 86. ЭТЛ-логика Эми́ттерно-свя́занная ло́гика (ЭСЛ, ECL) — семейство цифровых интегральных микросхем на основе дифференциальных транзисторных каскадов. ЭСЛ является самой быстродействующей из всех типов логики, построенной на биполярных транзисторах. Это объясняется тем, что транзисторы в ЭСЛ работают в линейном режиме, не переходя в режим насыщения, выход из которого замедлен. Низкие значения логических перепадов в ЭСЛ-логике способствуют снижению влияния на быстродействие паразитных ёмкостей. Основная деталь ЭСЛ-логики — схема потенциального сравнения, собранная не на диодах (как в ДТЛ), а на транзисторах. Схема представляет собой транзисторы, соединённые эмиттерами и подключенные к корпусу (или питанию) через резистор. При этом транзистор, у которого напряжение на базе выше, пропускает через себя основной ток. Как правило, один транзистор в схеме сравнения подключен к опорному уровню, равному напряжению логического порога, а остальные транзисторы являются входами. Выходные цепи схемы сравнения поступают на усилительные транзисторы, а с них — на выходные эмиттерные повторители. Эмиттерный повторитель — способ включения транзистора, когда коллектор подключен к шине питания, а эмиттер является выходом. Напряжение на выходе эмиттера практически соответствует напряжению на базе, куда подаётся входной сигнал. Поэтому он и называется повторителем. Повторитель усиливает ток, не усиливая напряжения. Используется в основном для согласования высокого выходного сопротивление источника сигнала с малым сопротивлением нагрузки. Особенностью ЭСЛ является повышенные скорость (150 МГц уже в первых образцах 60-х годов и 0,5…2 ГГц в 70—80-х) и энергопотребление по сравнению с ТТЛ и КМОП (на низких частотах, на высоких — примерно равное), низкая помехоустойчивость, низкая степень интеграции (ограниченная, в частности, большой потребляемой мощностью каждого элемента, что не позволяет разместить в одном корпусе много элементов, так как это приведёт к перегреву) и как следствие — высокая стоимость. 87. КМОП-логика В технологии КМОП используются полевые транзисторы с изолированным затвором с каналами разной проводимости. Отличительной особенностью схем КМОП по сравнению с биполярными технологиями (ТТЛ, ЭСЛ и др.) является очень малое энергопотребление в статическом режиме (в большинстве случаев можно считать, что энергия потребляется только во время переключения состояний). Отличительной особенностью структуры КМОП по сравнению с другими МОП-структурами (N-МОП, P-МОП) является наличие как n-, так и p-канальных полевых транзисторов; как следствие, КМОП-схемы обладают более высоким быстродействием и меньшим энергопотреблением КМОП-вентили достаточно просто реализуют функции ИЛИ-НЕ (NOR)и И-НЕ (NAND). Выход Q двухвходового логического элемента 2ИЛИ-НЕ зависит от входов X1 и X2 Q = X1 + X2 (сумма под черточкой) Рассмотрим КМОП-схему с двумя входами, в которой входные сигналы поступают на р-МОП, соединенные последовательно, и на n-МОП, соединенные параллельно  88. Триггерная ячейка. Основу триггеров составляют простейшие запоминающие ячейки, представляющие собой симметричную структуру из двух логических элементов ИЛИ-НЕ либо И-НЕ, охваченных перекрёстной обратной связью: /  / (В дальнейшем в шпоре Q c черточкой = Q1) / (В дальнейшем в шпоре Q c черточкой = Q1)Ячейки могут находиться в двух устойчивых состояниях: 1 и 0. Состоянию 1 соответствует единичный сигнал на выходе Q, состоянию 0 соответствует единичный сигнал на выходе Q1. Вход, по которому ячейка устанавливается в состояние 1, обозначается буквой S, а в состоянии 0 – буквой R. Когда на обоих информационных кодах существуют логические нули (S=R=0), сигналы на выходе могут иметь одно из двух сочетаний: Q=1, Q1=0 либо Q=0, Q1=1, так как каждый логический элемент ИЛИ-НЕ инвертирует входные сигналы, а переключающим сигналом служит единица. Допустим, что Q=1. Этот сигнал, действуя на входе нижнего элемента создаёт на его выходе Q1=0. В свою очередь, на входах верхнего элемента два нулевых сигнала – со входа R и с выхода Q1, обеспечивает Q=1. Состояние это устойчивое. Если на один из входов подать единичный сигнал, сохраняя нулевой на другом, триггер примет состояние, которое однозначно определяется входной информацией. При входных сигналах S=1, R=0 триггер принимает единичное состояние Q=1, Q1=0, а при S=0, R=1 – нулевое: Q=0, Q1=1. При появлении управляющего сигнала на одном из входов происходит либо опрокидывание триггера, либо подтверждение существующего состояния, если оно совпадает с требуемым. Если одновременно подать переключающие сигналы на оба входа (S=R=1), на обоих выходах появятся логические нули (Q=Q1=0) и устройство утратит свойства триггера. Поэтому комбинацию S=R=1 называют неопределённой (н/о). Переход от неопределённой комбинации к нейтральной (S=R=0) называют запрещенной комбинацией, так как состояние выходов при этом восстанавливается, но с равной вероятностью оно может стать единичным, так и нулевым, т.е. ведёт к непредсказуемому поведению триггера. Триггер, который переключается сигналами логической единицы, т.е. на логических элементах ИЛИ-НЕ, называют триггером с прямым управлением (RS-триггер). Триггер, который переключается сигналами логического нуля, т.е. на логических элементах И-НЕ, называют триггером с инверсными входами ( 89. Триггер с раздельными входами Этот триггер имеет два информационных входа: R и S и один выход - Q.  Условное обозначение и таблица переходов RS-триггера изображены на рисунке. (в данном случае изображен асинхронный триггер, у синхронного есть также вход С)

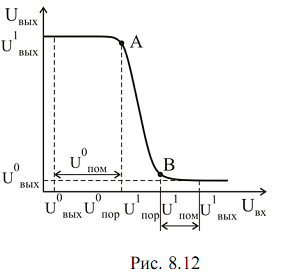

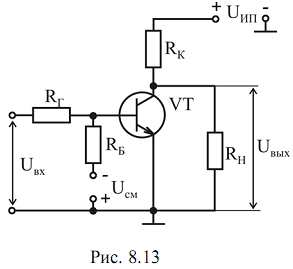

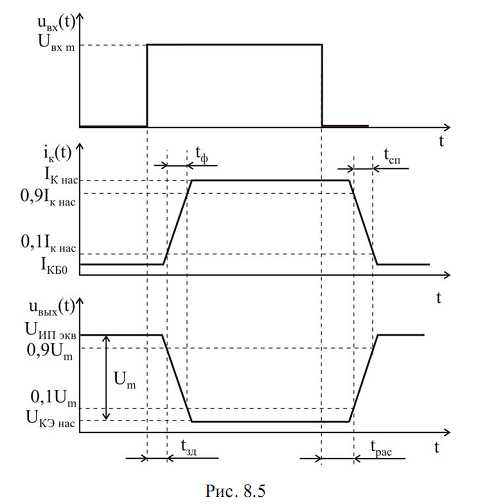

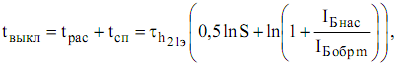

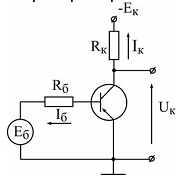

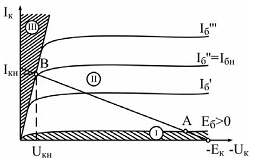

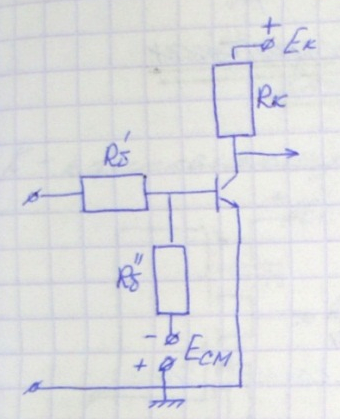

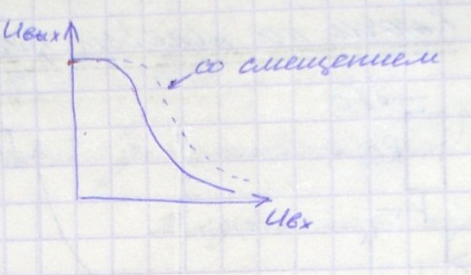

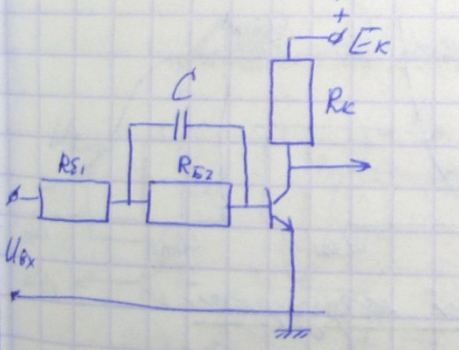

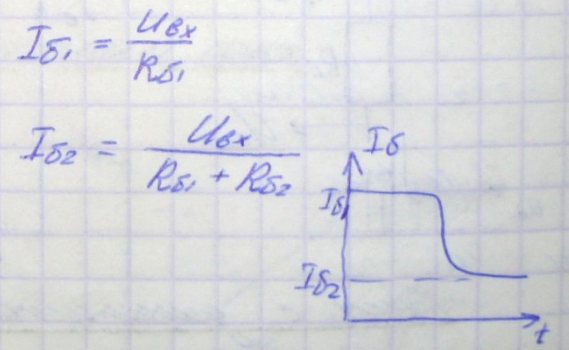

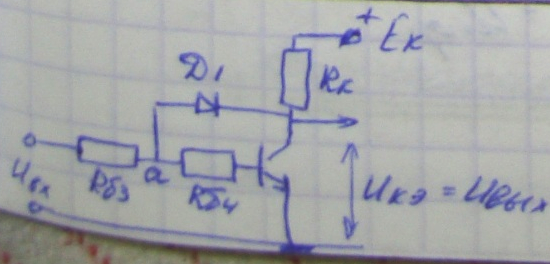

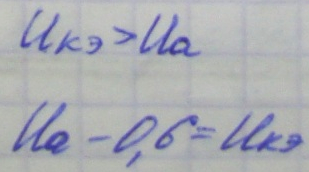

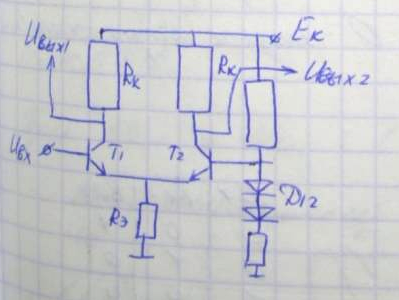

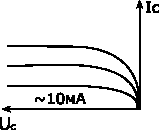

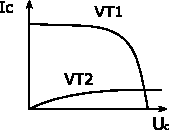

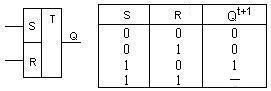

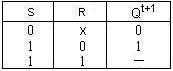

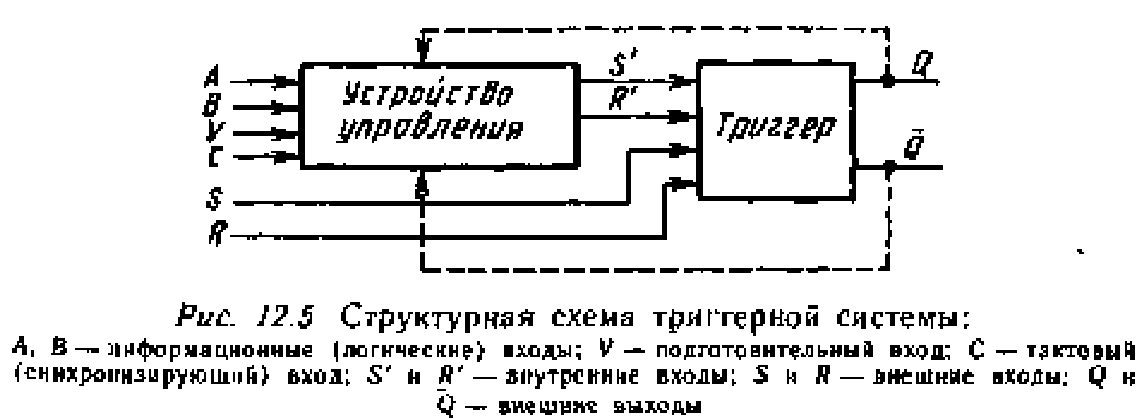

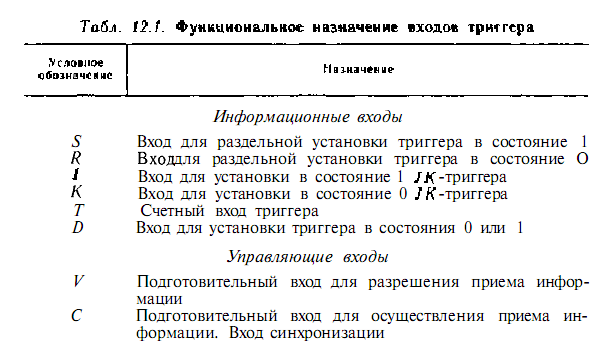

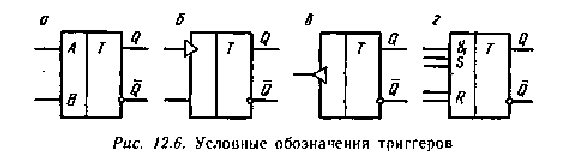

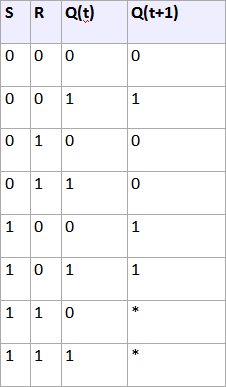

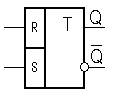

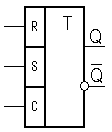

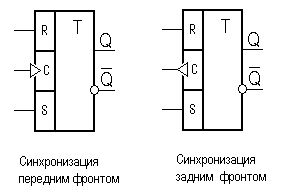

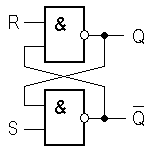

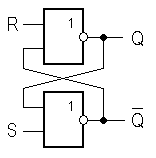

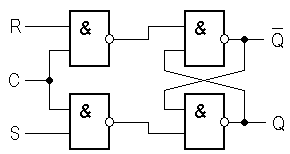

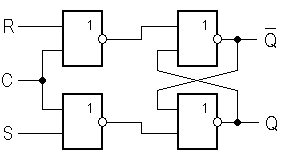

Анализируя таблицу переходов можно заметить, что переход триггера из 0 в 0 возможен при подаче комбинации R=0, S=0 или R=1, S=0, т.е. этот переход будет при R=X (безразличное состояние), S=0. Исходя из этого таблицу переходов можно изобразить в сокращенном виде:  При подаче комбинации S=R=1 состояние перехода Qt+1 не определено и эта комбинация сигналов является запрещенной для RS-триггера. 90. Интегральные триггеры Интегральные триггеры используются как самостоятельные устройства и, кроме того, входят в состав различных функциональных устройств: счетчиков, регистров, запоминающих устройств и т. п. Современные интегральные триггеры часто строятся на основе нескольких логических элементов, объединенных в одну микросхему. Они могут иметь несколько входов и различаться способами ввода входной информации. Для преобразования входной информации в требуемую комбинацию управляющих сигналов в триггере имеется устройство управления. Это устройство позволяет значительно расширить функциональные возможности триггера. Обобщенная структурная схема триггера с устройством управления показана на рис. 12.5. Входные сигналы  А, В, V, С, S, R в зависимости от выполняемой роли подразделяются на информационные (логические), подготовительные (разрешающие) и исполнительные (командные). Входы триггера, на которые подаются эти сигналы, соответственно носят названия: информационные (логические), предустановочные (подготовительные) и тактовые (синхронизирующие). В зависимости от назначения триггера предустановочные и тактовые входы могут отсутствовать, в то время как информационные входы имеются у каждого триггера. На схемах входы триггера обозначают буквами латинского алфавита в соответствии с табл. 12.1. По назва-  ниям информационных входов называют и триггеры: RS-триггер, D-триггер, //(-триггер и др. В зависимости от схемы управляющего устройства триггеры делятся на синхронные и асинхронные (от греч. а — не, сын — вместе, хронос — время). Асинхронные триггеры имеют только информационные (логические) входы, и в них запись информации осуществляется в момент ее поступления. Всинхронных триггерах запись информации, поступившей на информационные входы, происходит только при поступлении на синхронизирующий (тактирующий) вход дополнительного командного импульса. Синхронные триггеры могут иметь и асинхронные входы, которые обычно служат для установки триггера в нужное исходное состояние. Асинхронные триггеры используются в качестве коммутаторов, ключей, счетчиков импульсов, делителей частоты повторения импульсов и т. п. Синхронные триггеры применяются в вычислительной и цифровой технике. Работой триггеров можно управлять путем изменения уровней входных сигналов при достижении ими определенных порогов срабатывания, а также фронтами и срезами, возникающими при изменении этих уровней. Триггеры, переключающиеся по уровню входных сигналов, называют триггерами со статическим управлением, а по фронтам и срезам — триггерами с динамическим управлением. На схемах триггер изображают прямоугольником, разделенным вертикальной линией на две части (рис. 12.6): правая часть — основное поле, левая — дополнительное. В основном поле помещается буква Т, а в дополнительном у каждого входа пишется буква (метка), указывающая на его функциональное назначение в соответствии с табл. 12.1. Статические прямые входы и выходы отображают прямыми линиями без каких-либо индикаторов, а инверсные имеют дополнительный индикатор в виде маленького кружка на стороне прямоугольника (рис. 12.6, а). Динамические входы обозначают небольшими  треугольниками. У прямых динамических входов, вызывающих «опрокидывание» триггера при изменении уровня сигнала от 0 к 1, острие треугольника направлено внутрь поля (рис. 12.6, б), а у инверсных, вызывающих опрокидывание триггера при изменении уровня сигнала от 1 до 0,— наружу (рис. 12.6, в). У триггера может быть несколько информационных входов, связанных в группы операциями И либо ИЛИ. Группа входов, связанная операцией И, в дополнительном поле помечается символом логического умножения. Группа входов, связанная операцией логического сложения ИЛИ, дополнительных символов в условном обозначении не имеет (рис. 12.6, г). RS-триггеры_Триггер_с_раздельным_запуском_называют_RS-триггером'>91. RS-триггеры Триггер с раздельным запуском называют RS-триггером. RS-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы. RS-триггер имеет два входа и два выхода. Входы, на которые подают запускающие импульсы, называют установочными и обозначают R и S. Буква S означает раздельный вход установки в состояние 1, буква R -- раздельный вход установки в состояние 0. Выходы обозначают Q(t) и Q(t+1)  RS-триггеры могут быть асинхронными и синхронными, синхронизируемые уровнем либо фронтом синхросигнала. Асинхронным - называется такой триггер, который меняет свое состояние в момент подачи входного сигнала на входы S и R. Триггер называется синхронным, если у него помимо информационных входов S и R, существует управляющий вход С. Триггер будет менять свое состояние только при логической 1 на входе С Асинхронный RS-триггер:  Синхронный RS-триггер синхронизируемый уровнем:  Синхронный RS-триггер синхронизируемый фронтом:  Асинхронный RS-триггер на "И-НЕ":  Асинхронный RS-триггер на "ИЛИ-НЕ":  Синхронный RS-триггер на "И-НЕ"; "ИЛИ-НЕ":   |