Интерфейсы систем экзамен. АВ. Вопросы к экзамену по дисциплине Интерфейсы вычислительных систем

Скачать 1.07 Mb. Скачать 1.07 Mb.

|

|

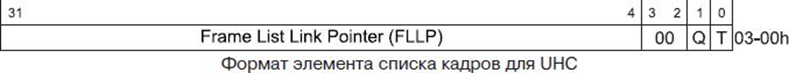

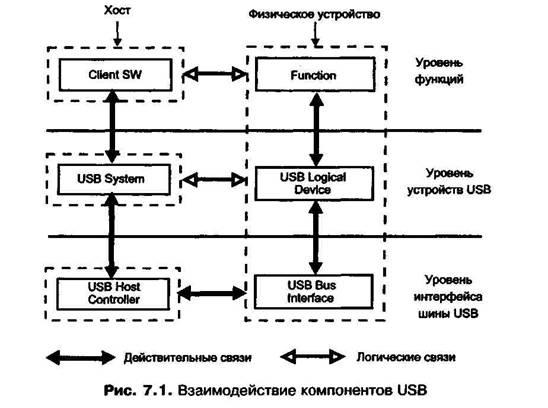

Тестовое оборудование для интерфейса RS-232C. Соединители. Эти дешевые устройства упрощают перекрестные соединения сигнальных линий интерфейса RS–232C. Они обычно оснащаются двумя разъемами типа D (или ленточными кабелями, имеющими розетку и вставку), и все линии проводятся к той области, куда можно вставить перемычки. Такие устройства включаются последовательно с линиями интерфейса RS–232C, и затем проверяются различные комбинации подключений. Трансформаторы разъема. Обычно эти приспособления имеют разъем RS–232C со штырьками на одной стороне и разъем с отверстиями на другой стороне. Пустые модемы. Как и предыдущие устройства, пустые модемы включаются последовательно в тракт данных интерфейса RS–232C. Их функции заключаются в изменении сигнальных линий таким образом, чтобы превратить DTE в DCE. Линейные мониторы. Мониторы индицируют логические состояния (в терминах MARK и SPACE) наиболее распространенных сигнальных линий данных и квитирования. С их помощью пользователь получает информацию о том, какие сигналы в системе присутствуют и активны. Врезки. Эти устройства обеспечивают доступ к сигнальным линиям. В них, как правило, совмещены возможности соединителей и линейных мониторов и, кроме того, предусмотрены переключатели или перемычки для соединения линий с обоих сторон устройства. Интерфейсные тестеры. По своей конструкции эти устройства несколько сложнее предыдущих простых устройств. Они позволяют переводить линии в состояния MARK или SPACE, обнаруживать помехи, измерять скорость передачи данных и индицировать структуру слова данных. Стандартный параллельный порт (SPP). Стандартный параллельный порт (Standard Parallel Port - SPP) представлен на задней стенке компьютера 25-контактным разъемом D-типа с отверстиями. Обычно кабель для этого разъема имеет на втором конце 34-контактный разъем, предназначенный для подключения к принтеру. Именно параллельный порт РС часто называется принтерным портом (printer port). В компьютере на разъем выведено четыре линии управления (CONTROL), пять линий состояния (STATUS) и восемь линий данных (DATA). Приведенные группы сигналов доступны через соответствующие регистры, которые часто тоже называются портами. Оставшиеся восемь контактов заземлены. При этом стандарт определяет пять режимов работы: 1. Режим совместимости (Compatibility Mode). 2. Режим тетрад (Nibble Mode). 3. Режим байтов (Byte Mode). 4. Режим улучшенного параллельного порта (Enhanced Parallel Port - EPP). 5. Режим порта с расширенными возможностями (Extended Capabilities Port -ECP). Аппаратные средства параллельного интерфейса. Стандарт IEEE 1284 определяет три разных разъема для использования с параллельным портом. Первый разъем 1284 Type A - это обычный 25-контактный разъем D-типа. Второй 36-контактный разъем 1284 Type B является разъемом Centronics. Третий разъем IEEE 1284 Type C представляет собой 36-контактный разъем, похожий на разъем Centronics, но меньше по размерам. Он имеет лучший фиксатор, лучшие электрические параметры и к нему проще подключать кабель. Два дополнительных сигнала можно использовать для проверки включенного состояния устройства. Этот разъем признан перспективным для применения в новых разработках Буква n перед названием сигнала означает сигнал с низким уровнем активности, например nError. Если в принтере возникла ошибка, на этой линии будет низкий уровень. Чтобы обеспечить нахождение принтера в известном начальном состоянии, выдаваемый компьютеру сигнал select говорит о том, что периферийное устройство находится в онлайновом режиме и готово принимать данные. Когда компьютер сформировал на линиях данных сигналы достоверных данных, то устройству необходимо сообщить о готовности данных, для этого предназначен импульсный сигнал строба nStrobe, который должен заставить устройство воспринять мои данные и сохранить его в буфере для последующей обработки. Компьютер должен ожидать до тех пор, пока принтер не будет готов к возобновлению приёма новых байтов. Принтеры используют сигнал занятости Busy для задержки компьютера до тех пор, пока принтер не будет в состоянии готовности к приему следующего байта. Сигнал Busy может задержать компьютер на любой временной интервал, если возникла серьезная ошибка, например, замятие бумаги. Когда принтер обработал байт, он запрашивает у компьютера следующий байт. Принтер снимает сигнал Busy и выдает короткий импульс подтверждения nAck. Таким образом с помощью сигналов nStrobe, Busy и nAck осуществляется управление (квитирование) передачей данных в параллельном порту. Линия nSelect-Printer позволяет компьютеру дистанционно переводить периферийное устройство в онлайновый или офлайновый режим. Сигнал высокого уровня на этой линии запрещает работу устройства. Сигнал nError от периферийного устройства сообщает компьютеру о возникшей проблеме, препятствующей печати, но не конкретизирует ее. Интерфейс Centronics. Centronics - это старый стандарт (его часто называют интерфейсом и протоколом) на передачу данных из компьютера (хоста - host) в принтер. Квитирование этого стандарта используется в большинстве принтеров и обычно реализуется программно. Приведём этапы работы протокола Centronics. Сначала на контакты 2-9 параллельного порта выдаются данные. Затем хост проверяет занятость принтера, т.е. на линии Busy должен действовать низкий уровень. После этого программа выдает строб, ожидает минимум 1 мкс и снимает строб. Данные обычно считываются устройством по нарастающему фронту строба. Принтер показывает свою занятость обработкой данных по линии Busy. Когда принтер воспринял данные, он подтверждает байт отрицательным импульсом длительностью около 5 мкс на линии nAck. Часто для экономии времени хост игнорирует сигнал на линии nAck. При рассмотрении порта с расширенными возможностями ЕСР реализация быстрого режима Centronics (Fast Centronics Mode) осуществляется схемным квитированием. Программист должен только записать байт данных в порт ввода-вывода. Схемы проверяют занятость принтера и формируют строб. Отметим, что в этом режиме линия nAck не контролируется. Параллельный порт (EPP). Улучшенный параллельный порт (Enhanced Parallel Port - ЕРР) разработан компаниями Intel, Xircom и Zenith Data Systems. Порты ЕРР были вначале определены в стандарте EPP 1.7, а затем включены в стандарт IEEE 1284 (1994 г.). Порт EPP имеет два стандарта EPP 1.7 и EPP 1.9. Скорость передачи данных составляет от от 500 КБ/с до 2 МБ/с. Она достигается тем, что квитирование, стробирование и другие операции формируются схемами порта, а не программно, как в интерфейсе Centronics. Порт ЕРР отличается от порта ЕСР тем, что порт ЕРР генерирует и управляет всеми передачами в/из периферийного устройства. С другой стороны, порт ЕСР требует, чтобы периферийное устройство подтверждало обратный канал и управляло квитированием. Порт состояния имеет одну небольшую модификацию. Бит 0, который зарезервирован в наборе регистров порта SPP, теперь стал битом таймаута (Timeout) порта EPP. Этот бит устанавливается, когда возникает таймаут порта ЕРР. Это происходит, когда сигнал на линии nWait не снимается через примерно 10 мкс (в зависимости от порта) после выдачи сигналов IOW или IOR. Линии сигналов IOW и IOR записи и считывания ввода-вывода имеются в шине ISA. Режим ЕРР очень сильно зависит от временной диаграммы (timing) шины ISA. Когда выполняется цикл считывания, порт должен предпринять соответствующее квитирование Read/Write и вернуть данные в этом цикле шины ISA. Конечно, этого не происходит в одном цикле ISA, поэтому порт использует сигнал готовности IOCHRDY (I/O Channel Ready) на шине ISA для введения состояний ожидания до завершения цикла. В порту ЕРР поддерживается таймер (watchdog), который настроен примерно на 10 мкс. Универсальный контроллёр UHC. Хост-контроллер UHC от Intel появился в микросхеме PIIX3 (мост PCI-ISA) чипсетов системных плат для процессоров Pentium и используется во многих последующих изделиях Intel. Это FS/LS хост-контроллер, который большую часть забот по планированию транзакций перекладывает на ПО, — драйвер контроллера UHC (UHCD). Контроллер UHC является активным устройством PCI (Bus-Master). Основное взаимодействие драйвера с хост-контроллером происходит с помощью дескрипторов, расположенных в памяти. Контроллер имеет регистры (в пространстве ввода/вывода), с помощью которых можно управлять его поведением: выполнять сброс, глобальную приостановку и пробуждение, подстраивать частоту кадров, управлять запросами прерываний, управлять портами встроенного корневого хаба. Контроллер позволяет работать в отладочном режиме, останавливаясь после выполнения каждой транзакции. Большое неудобство работы с UHC возникает из-за необходимости программного просмотра всех дескрипторов передач на предмет выявления завершенных. Дескрипторы завершенных передач необходимо программно извлекать из цепочек, сохраняя связанность элементов. Планирование транзакций (составление списков дескрипторов и заголовков) — тоже достаточно трудоемкая задача для драйвера. Очевидно, преследовалась цель упрощения аппаратных средств хост-контроллера. Однако это может обернуться зависимостью эффективной производительности шины USB от мощности и загрузки центрального процессора. Такой подход к организации ввода/вывода трудно назвать эффективным. Cтруктуры данных UHC. Драйвер в системной памяти создает список кадров Frame List, состоящий из 1024 элементов. Каждый элемент этого списка содержит 32-битный указатель на связанный список структур данных, по которым контроллер выполняет транзакции в данном кадре. Хост-контроллер имеет регистр базового адреса списка кадров, указывающий на начало списка. Текущий номер отрабатываемого элемента определяется десятью младшими битами счетчика кадров, находящегося в контроллере и инкрементируемого каждую миллисекунду. Период счета кадров можно немного варьировать, изменяя константу, занесенную в регистр модификации длительности кадра (SOF Modify Register), что обеспечивает возможность подстройки частоты кадров для синхронизации изохронных обменов. Элемент списка кадров может указывать либо на дескриптор изохронной передачи TD (Transfer Descriptor), либо (если в данном кадре изохронный обмен не планируется) на заголовок очереди QH (Queue Head). Если в данном кадре вообще не планируются передачи, то в элементе устанавливается признак-«заглушка» T (Terminate, конец связанного списка, в данном случае — пустого). Еще раз напомним, что здесь слово «передача» (Transfer, согласно спецификации UHCI) употребляется в узком смысле — она соответствует одной транзакции (передаче не более одного пакета данных). Элемент (32-битное слово) имеет формат, приведенный на рисунке ниже. Поле FLLP (Frame List Link Pointer) — указатель на элемент; бит T — признак последнего элемента (при T = 1 указатель FLLP недействителен). Бит Q задает класс связанного элемента, на который указывает FLLP (0 — TD, 1 — QH).  Для каждого кадра из списка устанавливается своя цепочка дескрипторов изохронных передач (возможно и пустая), последний из этой цепочки должен ссылаться на цепочку заголовков очередей. Цепочки заголовков QH могут быть общими для группы кадров или даже для всех кадров списка. Общая идея построения очередей состоит в том, чтобы создавать свою очередь для каждого установленного канала (для всех сконфигурированных точек, кроме изохронных). «Дежурный» метод обслуживания — по горизонтали, тогда после выполнения транзакции с одной точкой контроллер перейдет к другой точке (другой очереди). Связывание TD и QH через указатели позволяет формировать произвольные конфигурации переходов от одной очереди к другой и даже делать петли — в последнем случае возможно, что с одной точкой в кадре успеют пройти несколько транзакций. Если очередей много (установлено много каналов), то они распределяются по кадрам (из 1024-элементного списка) так, чтобы цепочка каждого кадра обязательно прошла по горизонтали до конца Структура хаба USB 2.0. USB (Universal Serial Bus — универсальная последовательная шина) является промышленным стандартом расширения архитектуры PC, ориентированным на интеграцию с телефонией и устройствами бытовой электроники. Архитектура USB определяется следующими критериями: 1) Легко реализуемое расширение периферии PC. 2) Дешевое решение, поддерживающее скорость передачи до 12 Mбит/с. 3) Полная поддержка в реальном времени передачи аудио и (сжатых) видеоданных. 4) Гибкость протокола смешанной передачи изохронных данных и асинхронных сообщений. 5)Интеграция с выпускаемыми устройствами. 6)Доступность в PC всех конфигураций и размеров. 7)Обеспечение стандартного интерфейса, способного быстро завоевать рынок. 8) Создание новых классов устройств, расширяющих PC. 9)С точки зрения конечного пользователя, привлекательны следующие черты USB: 10)Простота кабельной системы и подключений. 11)Скрытие подробностей электрического подключения от конечного пользователя. 12)Самоидентифицирующиеся ПУ, автоматическая связь устройств с драйверами и конфигурирование. 13)Возможность динамического подключения и конфигурирования ПУ. Хаб - ключевой элемент системы РпР в архитектуре USB. Хаб является кабельным концентратором. Точки подключения называются портами хаба. Каждый хаб преобразует одну точку подключения в их множество. Архитектура допускает соединение нескольких хабов. У каждого хаба имеется один восходящий порт (Upstream Port), предназначенный для подключения к хосту или хабу верхнего уровня. Остальные порты являются нисходящими (Downstream Ports), предназначенными для подключения функций или хабов нижнего уровня. Хаб может распознать подключение устройств к портам или отключение от них и управлять подачей питания на их сегменты. Каждый из портов может быть разрешен или запрещен и сконфигурирован на полную или ограниченную скорость обмена. Хаб обеспечивает изоляцию сегментов с низкой скоростью от высокоскоростных. Хабы могут управлять подачей питания на нисходящие порты; предусматривается установка ограничения на ток, потребляемый каждым портом. Взаимодействие компонентов USB.  Система USB разделяется на три уровня с определенными правилами взаимодействия. Устройство USB содержит интерфейсную часть, часть устройства и функциональную часть. Хост тоже делится на три части - интерфейсную, системную и ПО устройства. Каждая часть отвечает только за определенный круг задач, логическое и реальное взаимодействие между ними иллюстрирует рис. 7.1. В рассматриваемую структуру входят следующие элементы: - Физическое устройство USB - устройство на шине, выполняющее функции, интересующие конечного пользователя. - Client SW - ПО, соответствующее конкретному устройству, исполняемое на хост-компьютере. Может являться составной частью ОС или специальным продуктом. - USB System SW - системная поддержка USB, независимая от конкретных устройств и клиентского ПО. - USB Host Controller - аппаратные и программные средства для подключения устройств USB к хост-компьютеру. Все обмены (транзакции) по USB состоят из трех пакетов. Каждая транзакция планируется и начинается по инициативе контроллера, который посылает пакет-аркер (Token Packet). Он описывает тип и направление передачи, адрес устройства USB и номер конечной точки. В каждой транзакции возможен обмен только между адресуемым устройством (его конечной точкой) и хостом. Адресуемое маркером устройство распознает свой адрес и готовится к обмену. Источник данных (определенный маркером) передает пакет данных (или уведомление об отсутствии данных, предназначенных для передачи). После успешного приема пакета приемник данных посылает пакет подтверждения (Handshake Packet). Планирование транзакций обеспечивает управление поточными каналами. На аппаратном уровне использование отказа от транзакции (NAck) при недопустимой интенсивности передачи предохраняет буферы от переполнения сверху и снизу. Маркеры отвергнутых транзакций повторно передаются в свободное для шины время. Управление потоками позволяет гибко планировать обслуживание одновременных разнородных потоков данных. Устойчивость к ошибкам обеспечивают следующие свойства USB: - Высокое качество сигналов, достигаемое благодаря дифференциальным приемникам/передатчикам и экранированным кабелям. - Защита полей управления и данных CRC-кодами. - Обнаружение подключения и отключения устройств и конфигурирование ресурсов на системном уровне. - Самовосстановление протокола с тайм-аутом при потере пакетов. - Управление потоком для обеспечения изохронности и управления аппаратными буферами. - Независимость функций от неудачных обменов с другими функциями. |