|

|

Организация цифрового ввода-вывода. 4 лаб асм. Институт кибербезопасности и защиты информации

Министерство образования и науки Российской Федерации

Санкт-Петербургский политехнический университет Петра Великого

—

Институт кибербезопасности и защиты информации

Отчёт

по лабораторной работе №4

Организация цифрового ввода-вывода

Вариант 7

по дисциплине «Аппаратные средства вычислительной техники»

Выполнили:

|

студенты группы 4851004/90002

|

|

Е.И.Кирсанкин

|

|

|

(подпись, дата)

|

|

|

|

|

С.В.Логачева

|

|

|

(подпись, дата)

|

|

Проверил:

|

ассистент

|

|

А.С. Макаров

|

|

|

(подпись, дата)

|

|

Формулировка задания

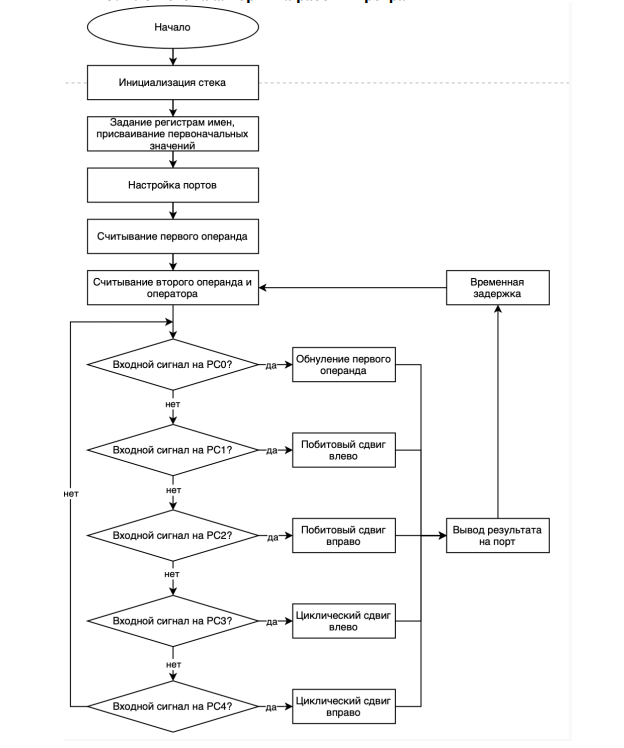

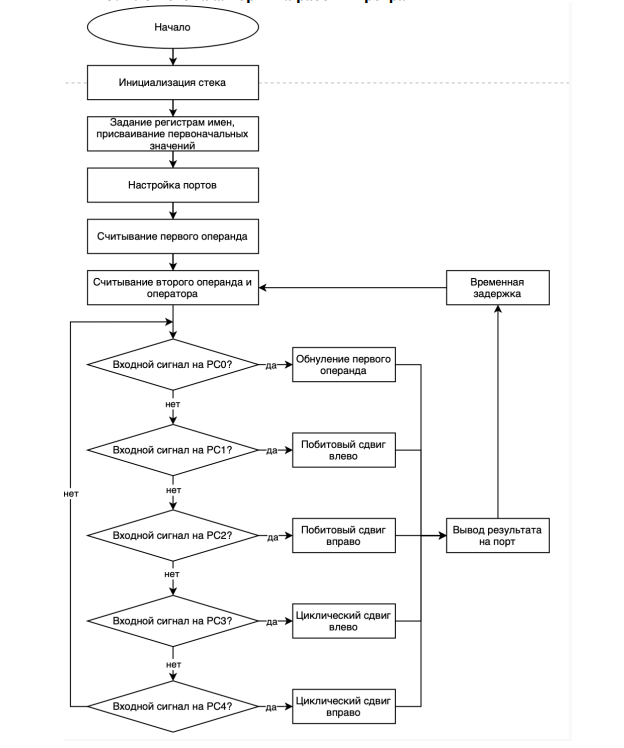

Реализовать простейший шестнадцатиразрядный калькулятор. Регистр PORTA отображает младшие разряды результата предыдущей операции или первый введённый операнд. Регистр PORTB отображает старшие разряды предыдущей операции. Регистр PORTD используется для ввода восьмиразрядного операнда в двоичной системе счисления (необходима временная задержка, позволяющая зажать несколько кнопок одновременно). Разряды регистра PORTC отвечают за указание математического действия (PC1 – логический сдвиг влево, PC2 – логический сдвиг вправо, PC3 – циклический сдвиг влево, PC4 – циклический сдвиг вправо) или обнуление регистров PORTA и PORTB – PC0. Ввод данных должен осуществляться в следующей последовательности: ввод первого операнда (восьмиразрядного), указание действия, ввод второго операнда (восьмиразрядного). После выполнения первой операции в качестве первого операнда может выступать результат предыдущей операции (шестнадцатиразрядный). Ввод второго операнда до указания действия приводит к замене первого операнда (на введённый, восьмиразрядный). Повторное указание действия перед вводом второго операнда приводит к замене выполняемого действия.

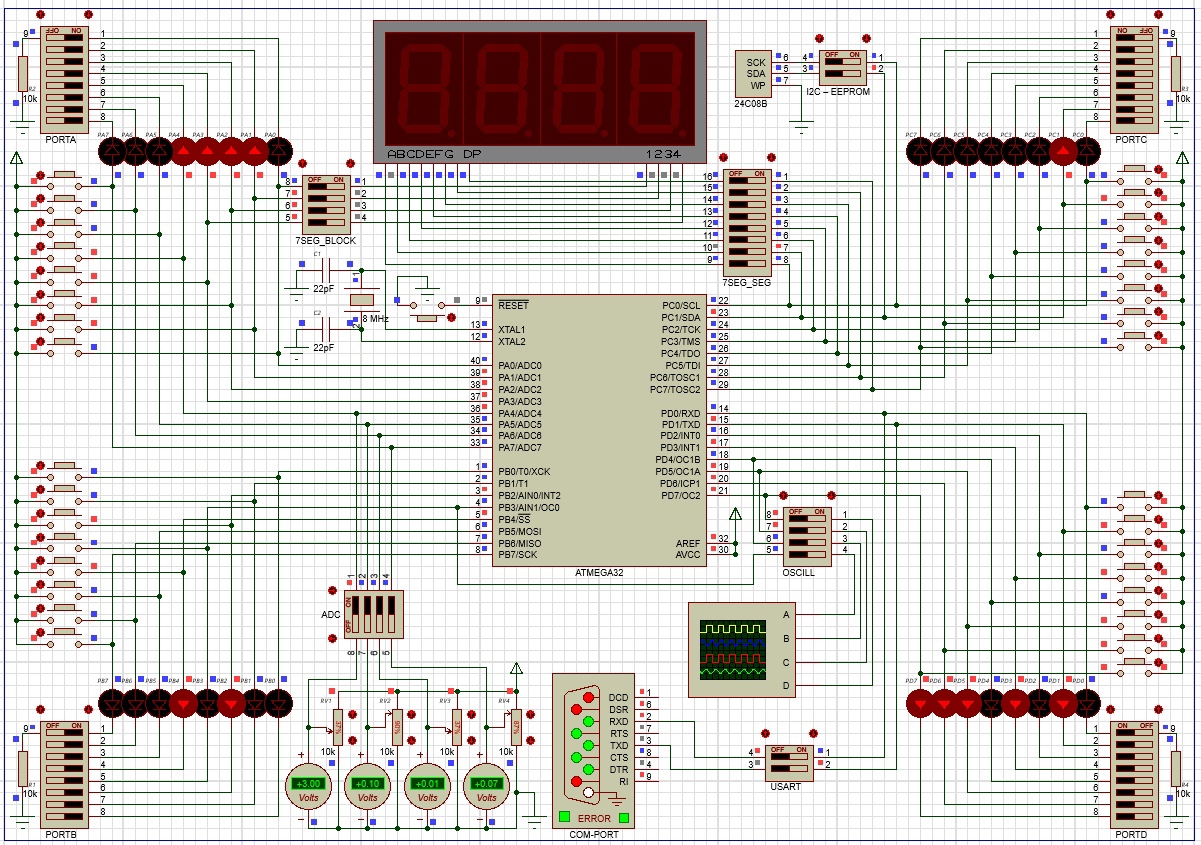

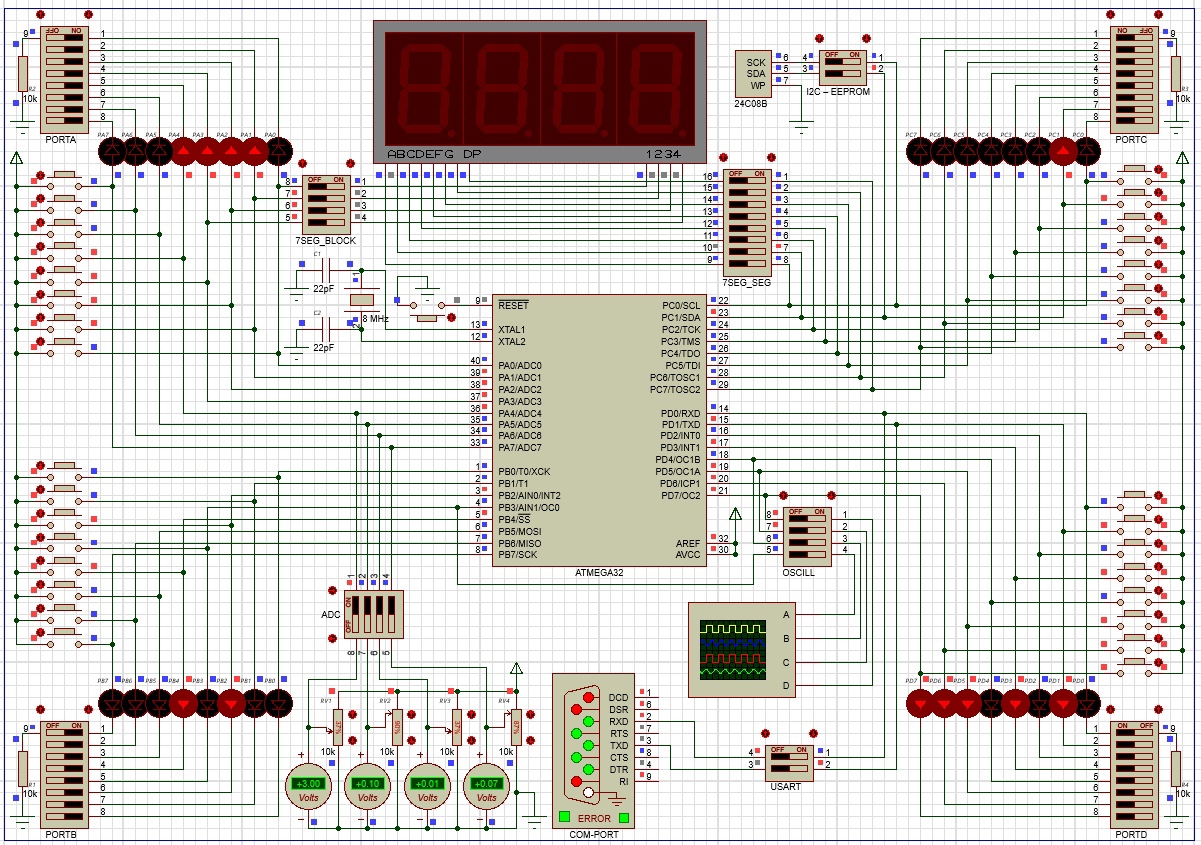

Схема лабораторной установки

Схема лабораторной установки

Блок-схема алгоритма работы программы

Результаты работы

Был реализован простейший шестнадцатиразрядный калькулятор, который может воспроизвести логический сдвиг влево, логический сдвиг вправо, циклический сдвиг влево, циклический сдвиг вправо или обнуление регистров PORTA и PORTB. Ввод данных осуществляется в следующей последовательности: ввод первого операнда (восьмиразрядного), указание действия, ввод второго операнда (восьмиразрядного). После выполнения первой операции в качестве первого операнда может выступать результат предыдущей операции (шестнадцатиразрядный).

Алгоритм выполнения задействованных команд (конструкций) ассемблера

Команда

|

Операнды

|

Описание

|

LDI

|

Rd, K

|

Загружает восьмиразрядную константу K в регистр Rd

|

OUT

|

P, Rr

|

Запись содержимого Rr в регистр ввода-вывода P

|

SER

|

Rd

|

Установка всех битов регистра

|

DEC

|

Rd

|

Декрементирует значение регистра Rd

|

BRNE

|

k

|

Условный относительный переход. Осуществляется в случае, когда бит Z установлен в ноль.

|

MOV

|

Rd, Rr

|

В регистр назначения Rd загружается копия содержимого регистра Rr

|

CPI

|

Rd, K

|

Сравнение содержимого регистра Rd с константой

|

BREQ

|

k

|

Условный относительный переход. Осуществляется в случае, когда бит Z установлен в единицу.

|

SER

|

Rd

|

Установка всех битов регистра

|

COM

|

Rd

|

Дополнение до 1

|

RCALL

|

k

|

Относительный Вызов подпр.

|

RJMP

|

k

|

Относительный безУсл. переход

|

IN

|

Rd, P

|

Считывание значения порта в регистр

|

ANDI

|

Rd, K

|

Логическое И с константой

|

RET

|

RET

|

Возврат из подпрограммы

|

LSL

|

Rd

|

Логический сдвиг влево

|

LSR

|

Rd

|

Логический сдвиг вправо

|

ROL

|

Rd

|

Циклический сдвиг влево (через флаг переноса)

|

ROR

|

Rd

|

Циклический сдвиг вправо (через флаг переноса)

|

Ответы на контрольные вопросы

Какими способами можно подключить внешние устройства (диод, кнопку) к контроллеру?

Связь микроконтроллера с внешними устройствами осуществляется через порты ввода-вывода. Каждый разряд порта соответствует одному из выводов микросхемы. Для кнопки надо выбранную ножку подключить через кнопку на землю. Сам же вывод надо сконфигурировать как вход с подтяжкой (DDRxy=0 PORTxy=1). Тогда, когда кнопка не нажата, через подтягивающий резистор, на входе будет высокий уровень напряжения, а из бит PINху будет при чтении отдавать 1. Если кнопку нажать, то вход будет положен на землю, а напряжение на нем упадет до нуля, а значит из PINxy будет читаться 0. По нулям в битах регистра PINх мы узнаем, что кнопки нажаты. Вывод порта для работы со светодиодом надо сконфигурировать на выход (DDRxy=1) и тогда в зависимости от значения в PORTxy на ножке будет либо высокий, либо низкий уровень напряжения.

Выводы по лабораторной работе

В ходе данной лабораторной работы была написана программа на языке ассемблер, которая представляет собой простейший калькулятор. Были получены навыки работы с микроконтроллерами, подключением светодиодов через регистры.

Приложение 1

Комментированный листинг программы для МК на языке ассемблера

//настройка стека

.CSEG

LDI R16,Low(RAMEND) //Старшие разряды адреса

OUT SPL,R16 ; Установка вершины стека в конец ОЗУ

LDI R16,High(RAMEND) ; Младшие разряды адреса

OUT SPH,R16 ; Установка вершины стека в конец ОЗУ

//присваивание символических имен константам

.equ WC = 8

.equ ZC = 10

.equ YC = 5

.equ XC = 1

//присваивание символических имен портам

.def FIRST_OPERAND = R16

.def SECOND_OPERAND = R17

.def RESULT = R18

.def OPERATION = R19

.def STEP = R21

//настройка портов на ввод и вывод и инициализация регистров

SER R20;

OUT DDRA, R20

COM R20

OUT DDRB, R20

LDI FIRST_OPERAND, 0

LDI SECOND_OPERAND, 0

LDI RESULT, 0

LDI OPERATION, 0

//начало работы программы

start:

RCALL scan_operands //считывание операндов

CPI OPERATION, 0b00000001

BRNE start_cond

LDI FIRST_OPERAND, 0

LDI OPERATION, 0

start_cond: //начальное состояние

CPI FIRST_OPERAND, 0

BREQ start

CPI SECOND_OPERAND, 0

BREQ start

CPI OPERATION, 0

BREQ start

LDI R20, 0

OUT PORTC, R20

RJMP start_calculation

wait_calc:

LDI R23, WC

LDI R22, ZC

LDI R21, YC

LDI R20, XC

delay_sub_calc: //задержка после вывода

DEC R20

CP R20, R23

BRNE delay_sub_calc

DEC R21

BRNE delay_sub_calc

DEC R22

BRNE delay_sub_calc

RET

start_calculation: //определение подсчетов

RCALL calculation

MOV FIRST_OPERAND, RESULT

LDI SECOND_OPERAND, 0

LDI RESULT, 0

LDI OPERATION, 0

RJMP start

scan_operands: //считывание операндов

IN R20, PINB

CPI R20, 0

BREQ scan_operation

CPI FIRST_OPERAND, 0

BRNE read_second_operand;

read_first_operand: //считывание первого операнда

RCALL wait

IN FIRST_OPERAND, PINB

RJMP scan_operation

read_second_operand: //считывание второго операнда

CPI OPERATION, 0

BREQ scan_operation

CPI SECOND_OPERAND, 0

BRNE scan_operation

RCALL wait

IN SECOND_OPERAND, PINB

scan_operation: //считывание операции

IN R20, PINC

ANDI R20, 0b00011111

CPI R20, 0

BREQ exit_scan

CPI FIRST_OPERAND, 0

BREQ exit_scan

RCALL wait

IN OPERATION, PINC

ANDI OPERATION, 0b00001111

exit_scan: //выход из считывания

RET

wait:

LDI R23, WC

LDI R22, ZC

LDI R21, YC

LDI R20, XC

delay_sub: //задержка

DEC R20

CP R20, R23

BRNE delay_sub

DEC R21

BRNE delay_sub

DEC R22

BRNE delay_sub

RET

calculation:

IN R20, PINC

CPI R20, 0

BRNE calculation

shift_to_left: //побитовый сдвиг влево

CPI OPERATION, 0b00000010

BRNE shift_to_right

MOV RESULT, FIRST_OPERAND

MOV STEP, SECOND_OPERAND

shift_to_left_start:

LSL RESULT

DEC STEP

CPI STEP, 0

BRNE shift_to_left_start

RJMP end_calculation

shift_to_right: //побитовый сдвиг вправо

CPI OPERATION, 0b00000100

BRNE cycle_shift_to_left

MOV RESULT, FIRST_OPERAND

MOV STEP, SECOND_OPERAND

shift_to_right_start:

LSR RESULT

DEC STEP

CPI STEP, 0

BRNE shift_to_right_start

RJMP end_calculation

cycle_shift_to_left: //циклический сдвиг влево

CPI OPERATION, 0b00001000

BRNE cycle_shift_to_right

MOV RESULT, FIRST_OPERAND

MOV STEP, SECOND_OPERAND

cycle_shift_to_left_start:

CLC

ROL RESULT

BRCC SKIP_INC

INC RESULT

SKIP_INC:

DEC STEP

CPI STEP, 0

BRNE cycle_shift_to_left_start

RJMP end_calculation

cycle_shift_to_right: //циклический сдвиг вправо

CPI OPERATION, 0b00010000

BRNE shift_to_left

MOV RESULT, FIRST_OPERAND

MOV STEP, SECOND_OPERAND

cycle_shift_to_right_start:

CLC

ROR RESULT

BRCC SKIP_ORI

ORI RESULT, 0b10000000

SKIP_ORI:

DEC STEP

CPI STEP, 0

BRNE cycle_shift_to_right_start

RJMP end_calculation

end_calculation:

OUT PORTA, RESULT

end:

RET

Алгоритм расчёта: MD5

|

Контрольная сумма:

|

|

Санкт-Петербург

2021

|

|

|

Скачать 0.7 Mb.

Скачать 0.7 Mb.