Курсовая работа (проект) по дисциплине эвм и периферийные устройства

Скачать 352.7 Kb. Скачать 352.7 Kb.

|

|

Минобрнауки России Юго-Западный государственный университет Кафедра вычислительной техники КУРСОВАЯ РАБОТА (ПРОЕКТ) по дисциплине «ЭВМ и периферийные устройства » (наименование дисциплины) на тему «Проектирование вычислительного устройства » Направление подготовки (специальность) Информатика и (код, наименование) вычислительная техника Автор работы (проекта) (инициалы, фамилия) (подпись, дата) Группа Руководитель работы (проекта) (инициалы, фамилия) (подпись, дата) Работа (проект) защищена (дата) Оценка Члены комиссии (подпись, дата) (инициалы, фамилия) (подпись, дата) (инициалы, фамилия) (подпись, дата) (инициалы, фамилия) Курск 2021 г Минобрнауки России Юго-Западный государственный университет Кафедра вычислительной техники ЗАДАНИЕ НА КУРСОВУЮ РАБОТУ (ПРОЕКТ) Студент шифр группа (фамилия инициалы) 1. Тема: «Проектирование вычислительного устройства» 2. Срок представления работы (проекта) к защите « 21 » май 2021 г. 3. Исходные данные (для проектирования, для научного исследования): Формат команд: SI, RgI; способ адресации: прямая и косвенная адресация; разрядностьданных-8 бит;организация памяти-2Кбит·8 бит; формат данных- целые числа; формат представления чисел-прямой код; операция сложения 4. Содержание пояснительной записки курсовой работы (проекта): 4.1. Проектирование вычислительного устройства 4.2. Разработка алгоритмов выполнения арифметических и логических операций 4.3. Разработка операционного автомата арифметико-логического устройства 4.4. Проектирование управляющего автомата устройства управления АЛУ 4.4. Разработка функциональной схемы вычислительного устройства 5. Перечень графического материала: Вычислительное устройство. Схема функциональная; Обобщенный размеченный алгоритм командного цикла вычислительного устройства; Обобщенный размеченный алгоритм АЛУ. Руководитель работы (проекта) (подпись, дата) (инициалы, фамилия) Задание принял к исполнению РЕФЕРАТ 33 стр., 14 рис., 9 табл., 5 использованных источников. Вычислительное устройство, арифметико-логическое устройство, операционный автомат, дешифратор, триггер,оперативная память. Объектом данного курсового проекта является функционально законченное вычислительное устройство. Цель проекта – разработка вычислительного устройства для работы с вещественными двоичными числами, а также создание технической документации, отвечающей правилам, рекомендованным едиными системами конструкторской документации. В процессе работы проведены разработка алгоритмы работы и функциональная схема вычислительного устройства, а также алгоритм работы арифметико-логического устройства. СОДЕРЖАНИЕ ВВЕДЕНИЕ 5 1 Проектирование вычислительного устройства 7 1.1 Исходные данные на проектирование 7 1.2 Определение форматов команд и формирование алгоритмов вычислительного устройства 7 2Разработка алгоритмов выполнения арифметических и логических операций 21 3Разработка операционного автомата арифметико-логического устройства 22 4Проектирование управляющего автомата устройства управления АЛУ 26 5Разработка функциональной схемы вычислительного устройства 29 ЗАКЛЮЧЕНИЕ 30 СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ 31 КП 09.03.01.21.81з.Б1.Б.11.2 Э2 – Вычислительное устройство. Схема функциональная КП 09.03.01.21.81з.Б1.Б.11.2 ТЧ – Обобщенный размеченный алгоритм командного циклавычислительного устройства КП 09.03.01.21.81з.Б1.Б.11.2 ТЧ1 – Обобщенный размеченный алгоритм АЛУ ВВЕДЕНИЕЭффективность применения современных средств вычислительной техники во всех сферах научной и производственной деятельности оказывает решающее влияние на увеличение производительности труда и ускорение научно-технического прогресса [1]. Вычислительные устройства широко применяются в области экономики, планирования, управления производственной деятельностью предприятия, автоматизации исследований и проектно-конструкторских работ, автоматизации технологических процессов и управления различными объектами. В них математические и логические операции производятся над числами, представленными в виде цифровых кодов, для чего в них имеются электронные устройства, с помощью которых и осуществляются эти операции [2]. Проектирование вычислительного устройства – это длительный процесс. В основе вычислительного устройства чаще всего используется структура фон Неймана. Обязательными элементами любого вычислительного устройства являются устройства ввода/вывода, запоминающее устройство, арифметико-логическое устройство, устройство управления. Объектом курсового проектирования является специализированное вычислительное устройство, включающее процессор и запоминающее устройство. Целью курсового проектирования является освоение методики проектирования и разработки операционных и управляющих устройств проектируемого вычислительного устройства, а также подготовки технической документации. В процессе работ над курсовым проектом необходимо: спроектировать форматы команд вычислительного устройства; разработать алгоритм командного цикла устройства; разработать алгоритмы выполнения арифметических, логических операций, операций передачи управления и операций работы со стеком; построить управляющий автомат арифметико-логического устройства; разработать функциональную схему вычислительного устройства. 1 Проектирование вычислительного устройства1.1 Исходные данные на проектированиеВ курсовом проекте необходимо разработать вычислительное устройство. Необходимо реализовать следующий набор операций: арифметические операции: сложение; вычитание; умножение; деление; логические операции: конъюнкция; дизъюнкция; импликация; инверсия; сложение по модулю два; операции со стеком: запись данных в стек; запись адреса в стек; извлечение данных из стека; извлечение адреса из стека; операции передачи управления: переход по адресу. При этом используются следующие форматы команд: A-I – «аккумулятор – непосредственный операнд»; Rg-I – «регистр – непосредственный операнд». Формирование исполнительного адреса операнда должно быть организовано следующими способами (типами) адресации (ТА): прямой адресации (ПА); косвенной адресации (КА). Данные представленыцелыми числами размером 8 бит. Организация памяти – 256 бит ∙ 8 бит. Операция для подробного описания – вычитаниев обратном коде. 1.2 Определение форматов команд и формирование алгоритмов вычислительного устройстваОсновная задача на данном этапе – это определение разрядностей основных шин и блоков, в частности – шины данных, шины адреса, шины управления, АЛУ, ОП, УУ, регистров (Rg), а также разрядностей команд и данных и количества регистров, обеспечивающих выполнение заданного набора операций. Первый этап – это определение разрядностей основных коммуникационных элементов разрабатываемого вычислительного устройства: шины данных (ШД), шины адреса (ША). В задании не задана шина данных, поэтому возьмем ее равной 8 бит, то есть ШД {7-0}. Для определения разрядности ША должны быть заданы параметры запоминающего устройства, в частности, разрядность слова и емкость. Оценку разрядности ША можно выполнить за два этапа. На первом этапе необходимо найти полноечисло ячеек памяти, оно задано в битах. Из задания узнаем, что имеется256ячеек памяти. На следующем этапе необходимо подобрать ближайшую наименьшую степень двойки, достаточную для того, чтобы записать в двоичной системе счисления полученное число ячеек. Такой степенью является число 8, то есть 28. Таким образом разрядность шины адреса должна быть равна 8. Получаем ША{7-0}. Далее необходимо составить формат команды (рис. 1). Рисунок1 – Формат команды На рисунке 1 обозначено: КОП – код операции; ТА – тип адресации; ФД – формат данных. Определим разрядность всех полей команды. Так как количество операций, которые необходимо реализовать в разрабатываемом устройстве, равно 14, то для того чтобы их закодировать, необходимо 4 двоичных разряда. После выбора количества разрядов КОП необходимо закодировать все операции системы команд. Для этого составляем следующую таблицу, в которой проставляем коды заданных команд (табл. 1). Таблица 1 – Кодирования команд

Чтобы закодировать содержимое поля ТА необходимодин разряд, так как задано два типа адресации. При этом необходимо выбрать коды всех заданных видов ТА. Примем: для прямой адресации: ТА = 0; для косвенной: ТА = 1. Для кодирования содержимого поля ФД необходим один разряд, так как задано 2 формата данных. Примем: дляA-I: ФД = 0; дляRg-I: ФД = 1. После кодирования содержимого этих полей необходимо переходить к выбору длин полей операндов. Для формата A-I: Поле Операнд 1 – аккумулятор, который имеет разрядность 16 бит и явно не адресуется. Последнее поле Операнд 2 – непосредственный операнд I, имеет разрядность, равную разрядности данных, т.е. 8 бит. Получаем следующий формат команды (рис. 2).  Рисунок 2 – Формат команды для варианта A-I Полученный формат команды имеет длину 13 бит, но, так как разрядность команды должна быть кратна разрядности ячейки памяти, ее необходимо дополнить до 2-х ячеек, т.е. 16-ти бит. Для команд формата Rg-I ситуация выглядит иначе. Поле Операнд 1 – номер регистра. Пусть регистров общего назначения будет 4 по 8 бит, тогда для кодирования номера регистра достаточно 2-х двоичных разрядов. Поле Операнд 2 – непосредственный операнд. Отсюда получаем следующий формат команды для варианта Rg-I (рис. 3).  Рисунок 3– Формат команды для варианта Rg-I Так же отметим, что размер регистра RgI, содержащего исполняемую команду будет равен 16 бит. И выделим один буферный регистр RgBufдля обращения с шиной адреса, размером 8 бит. Так же размер ячеек стека возьмем равным 8 бит. После определения форматов команд необходимо составить содержательную таблицу кодирования всех вариантов форматов команд. Для каждого формата командыоперанды будут загружаться в регистры общего назначения, как показано в таблице 2. Таблица 2 – Загрузка операндов в регистры общего назначения

В данной таблице приняты следующие сокращения наименований и условные обозначения содержимого полей, ячеек ОП и регистров: ОП – оперативная память; [address] – операнд из ячейки с адресом address; S – адрес памяти полученный из команды; {} – указание разрядности; BAZA – установленное значение, константа (начальный адрес памяти); A – акуумулятор; Rg[Rg] – регистр под номером [Rg]; I – непосредственный операнд; . – конкатенация бит. А содержательная таблица кодирования всех вариантов форматов команд представлена ниже. Таблица 3 – Содержательная таблица кодирования всех вариантов форматов команд

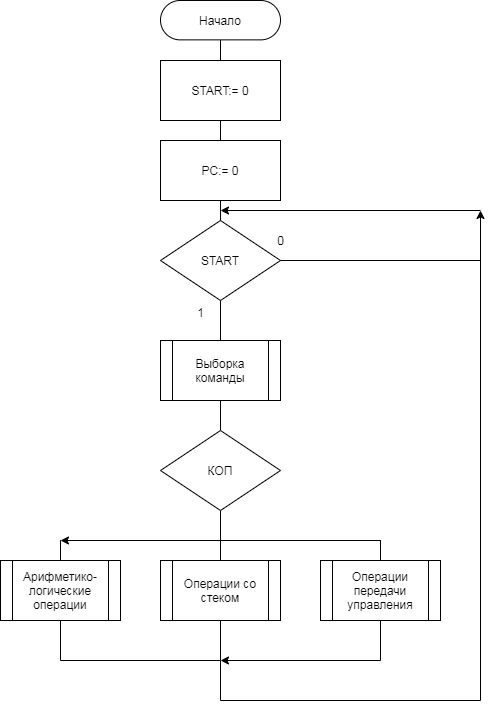

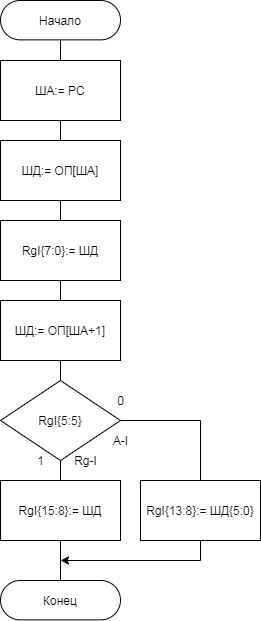

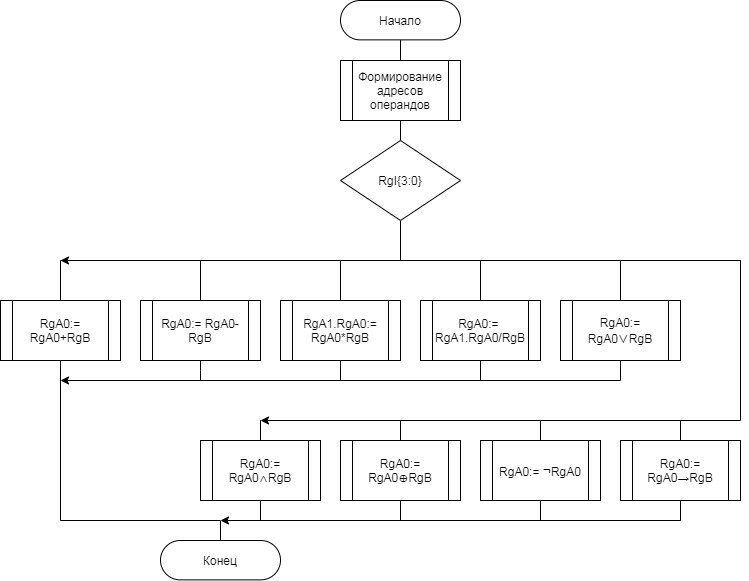

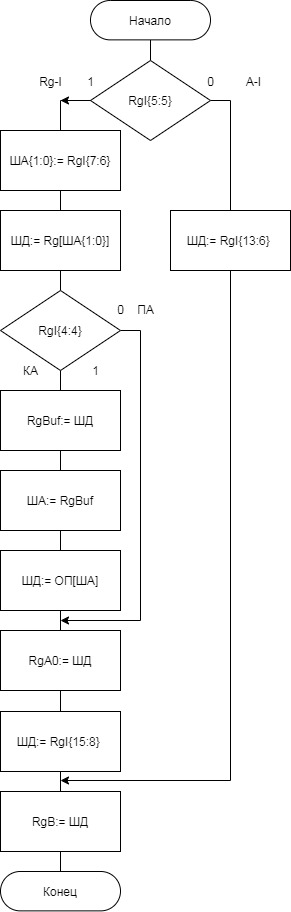

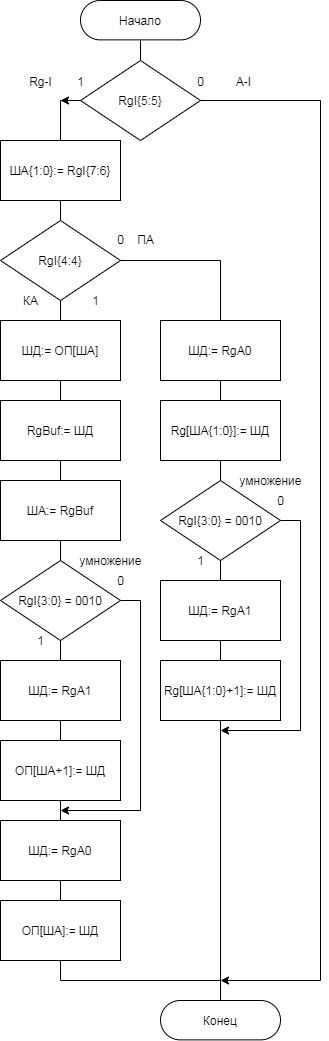

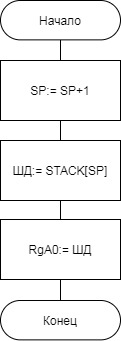

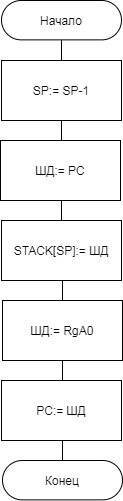

В данной таблице приняты следующие сокращения наименований и условные обозначения содержимого полей, ячеек ОП и регистров: SP – регистр указатель стека; PC – регистр программный счетчик. Ниже представлены алгоритмы вычислительного устройства.  Рисунок 4 – Обобщенный алгоритм командного цикла  Рисунок 5 – Алгоритм выборки команды  Рисунок 6 – Алгоритм выполнения арифметико-логических операций  Рисунок 7 – Алгоритм формирования операндов  Рисунок 8 – Алгоритм передачи данных после выполнения арифметико-логических операций  Рисунок 9 – Запись данных/адреса в стек  Рисунок 10 – Извлечение данных/адреса из стека  Рисунок 11 – Переход по адресу Список микроопераций для алгоритма выполнения команд УУ верхнего уровня ВУ представлен в таблице 4, а логических условий в таблице 5. Таблица 4 – Список микроопераций

Таблица 5 – Списоклогическихусловий

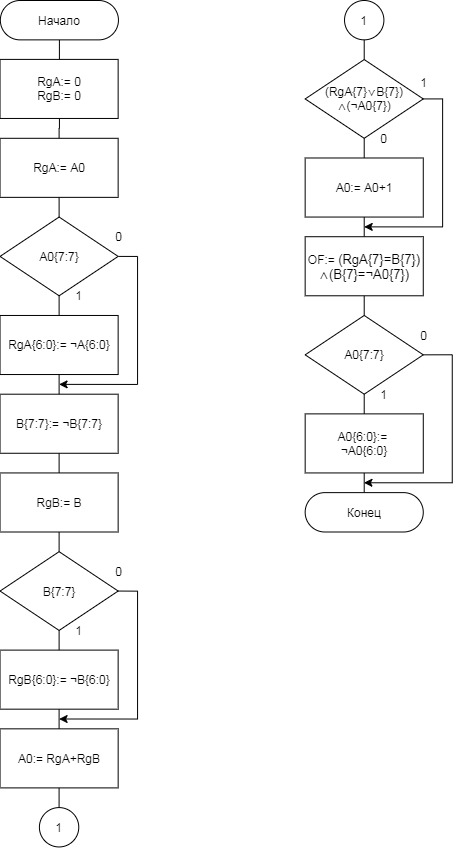

На основе алгоритма командного цикла, списков микроопераций и логических условий составляем обобщенный алгоритм командного цикла с размеченными состояниями.Он показан наКП 09.03.01.21.81з.Б1.Б.11.2 ТЧ. 2Разработка алгоритмов выполнения арифметических и логических операцийАрифметико-логическое устройство должно реализовывать следующие арифметические и логические операции: арифметические операции: сложение; вычитание; умножение; деление; логические операции: дизъюнкция; конъюнкция; импликация; инверсия; сложение по модулю два. Входные операнды АЛУ размещаются в одном сдвоенном 16-ти разрядном регистре A и одном 8-ми разрядном регистре B. Результат заносится в регистр A.Так же используются двастатических 8-ми разрядных вспомогательных регистраRgAи RgB и флаг переполнения OF. Отрицательные числа представляются в обратном коде. Алгоритм выполнения операции вычитания представлен ниже.  Рисунок 12 – Алгоритм выполнения операции вычитания 3Разработка операционного автомата арифметико-логического устройстваПри построении операционного автомата, как автомата выполнения команд, необходимо представить алгоритм командного цикла в виде последовательности микроопераций микропрограммного автомата (МПА) ведущего УУ АЛУ. Обозначим множество входных сигналов (логических условий) МПА ведущего УУ через  , а множество его выходных (управляющих) сигналов – через , а множество его выходных (управляющих) сигналов – через  . Выходные сигналы Y УУ управляют коммуникациями (передачей) операндов, адресов, флагов и т.п.) между регистрами и блоками, создавая тем самым необходимые предпосылки для выполнения команд. Его входными сигналами Х являются флаги, хранящиеся в регистре флагов, и унитарные коды, являющиеся результатами дешифрирования управляющих полей команды, хранящиеся в регистре команд. . Выходные сигналы Y УУ управляют коммуникациями (передачей) операндов, адресов, флагов и т.п.) между регистрами и блоками, создавая тем самым необходимые предпосылки для выполнения команд. Его входными сигналами Х являются флаги, хранящиеся в регистре флагов, и унитарные коды, являющиеся результатами дешифрирования управляющих полей команды, хранящиеся в регистре команд.Совокупность недетализированных основных блоков, регистров и счетчиков, а также коммуникаций между ними является операционным автоматом (иногда называемым устройством или автоматом выполнения команд). Входными сигналами операционного автомата являются выходные сигналы Y ведущего УУ, а выходными сигналами – входные сигналы Х ведущего УУ. В связи с этим оба автомата вычислительного устройства: и операционный, и управляющий могут быть разработаны на основании одного и того же алгоритма командного цикла, так как он реализуется в результате их взаимодействия. Список микроопераций для алгоритма выполнения команд УУ верхнего уровня АЛУ представлен в таблице 6, а логических условий в таблице 7. Таблица 6 – Список микроопераций и логических условий для АЛУ

Таблица 7 – Список логических условий для АЛУ

На основе алгоритма операции вычитания, списков микроопераций и логических условий АЛУ составляем обобщенный алгоритм работы АЛУ с размеченными состояниями.Он показан наКП 09.03.01.21.81з.Б1.Б.11.2 ТЧ1. 4Проектирование управляющего автомата устройства управления АЛУБудем проектировать автомат с жесткой логикой. Микропрограммный автомат с жесткой логикой реализуется в виде жестко закоммутированной (аппаратной) логической сети. Процесс синтеза схемы МПА с жесткой логикой называется структурным синтезом и разделяется на следующие этапы: выбор типа логических и запоминающих элементов; кодирование состояний автомата; синтез комбинационной схемы, формирующей выходные сигналы. Структурная схема управляющего автомата при реализации МПА на жесткой логике приведена на рисунке 13. В качестве закона функционирования управляющего автомата выберем закон функционирования автомата Мили. Множество состояний автомата обозначим через  . .В соответствии с обобщенным размеченным алгоритмом командного цикла, МПА ведущего УУ должен фиксировать 13 состояний (состояния s0…s12). Для хранения в памяти МПА кодов этих состояний воспользуемся D-триггерами, которые функционируют на основе таблицы истинности, представленной в таблице 8. Таблица 8 – Таблица истинности для D-триггера

Рисунок 13 – Структурная схема УУ АЛУ Выбираем количество триггеров, соответствующее числу, равному ближайшей наибольшей степени двойки. Этот показатель степени равен 4, следовательно, необходимо 4 D-триггеров. Комбинационная схема (КС) состоит из набора программируемых логических интегральных схем ПЛМ или ПЛИС, которые, в зависимости от значений логических сигналов  и элементов и элементов , определяющего текущее состояние устройства, вырабатывают множество выходных значений, состоящее из подмножества управляющих сигналов , определяющего текущее состояние устройства, вырабатывают множество выходных значений, состоящее из подмножества управляющих сигналов  и подмножества и подмножества , определяющего следующее состояние устройства. , определяющего следующее состояние устройства. На выходе КС образуется код следующего состояния S' автомата. Список кодов и таблица переходов автомата для ведущего УУ АЛУ, представлен в таблице 9. Таблица 9 – Список кодов состояний и таблица переходов ведущего управляющего автомата АЛУ

Каждая строка данной таблицы определяет набор входных данных, наличие которых на входе МПА необходимо для того, чтобы в выходном наборе МПА были истинными поименованные биты. Здесь индекс определяет номер бита во входном или выходном наборах. 5Разработка функциональной схемы вычислительного устройстваНа основе спроектированных операционных автоматов устройств управления вычислительного и арифметико-логического устройств следует разработать функциональную схему вычислительного устройства (приведена наКП 09.03.01.21.81з.Б1.Б.11.2 Э2). ЗАКЛЮЧЕНИЕВ ходе выполнения курсового проекта в соответствии с вариантом задания было спроектировано вычислительное устройство.Сформированы и обоснованы форматы команд, использующиеся в нем. Представлены принципы выполнения алгоритмов взаимодействия частей вычислительного устройства. Описан операционный автомат, регулирующий работу элементов устройства. Построены алгоритмы выполнения арифметико-логических операций и, как следствие, сформирован операционный автомат арифметико-логического устройства. Охарактеризован управляющий автомат арифметико-логического устройства на основе закона функционирования автомата Мили, сформированный на жесткой логике. Так же разработана функциональная схема вычислительного устройства. СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВЦилькер, Б.Я. Орлов С.А. Организация ЭВМ и систем [Текст]: Учебник для вузов / Б.Я. Цилькер, С.А. Орлов. – СПб.: Питер, 2015. – 668 с. Рыбальченко, М. В. Организация ЭВМ и периферийные устройства: учебное пособие / М. В. Рыбальченко. - Ростов-на-Дону; Таганрог : Издательство Южного федерального университета, 2017. – 85 с. – Текст : электронный. – Режим доступа: biblioclub.ru. Проектирование вычислительного устройства [Электронный ресурс] : методические рекомендации к курсовому проектированию по дисциплине «ЭВМ и периферийных устройств» для студентов специальности 090301 / Юго-Зап. гос. ун-т ; сост. Д. Б. Борзов. - Курск : ЮЗГУ, 2017. – 25. Корнеев В.В., Киселев А.В. Современные микропроцессоры. М.: НОЛИДЖ, 2016. - 320 с. ЕСПД. Схемы алгоритмов и программ. Правила выполнения. ГОСТ 19.002-80. М„ 1980. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||