СРЕДА ПРОЕКТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ QUARTUS. ЛР1. Лабораторная работа 1 среда проектирования цифровых устройств quartus

Скачать 1.2 Mb. Скачать 1.2 Mb.

|

|

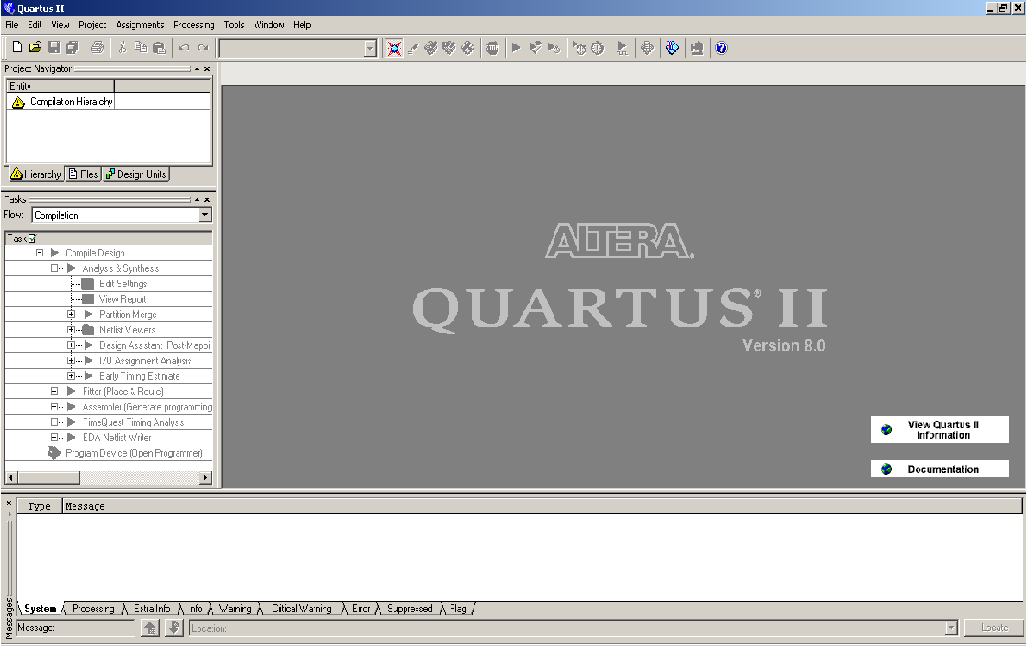

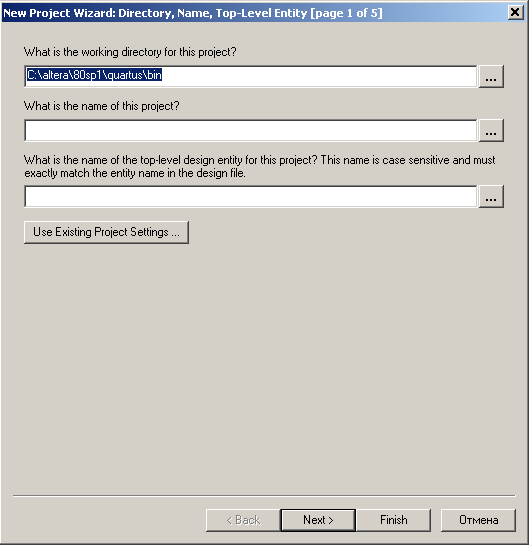

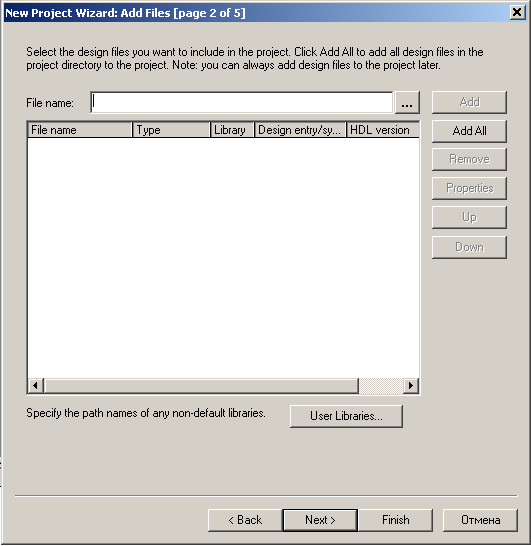

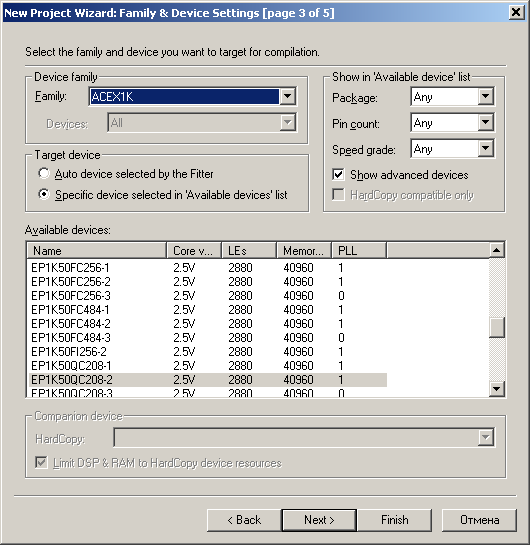

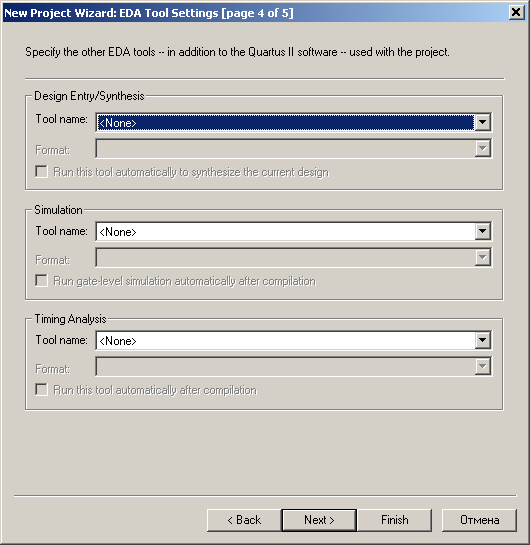

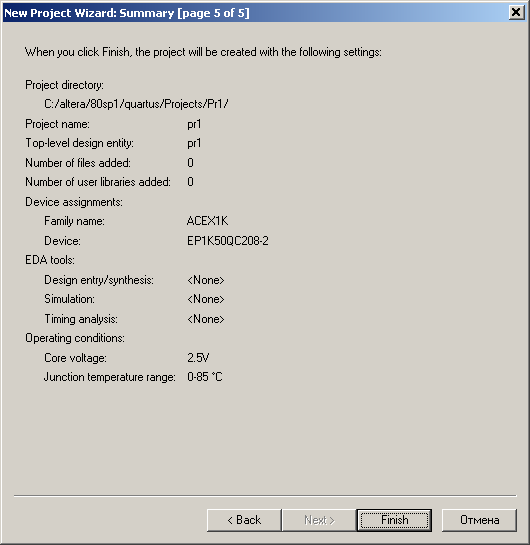

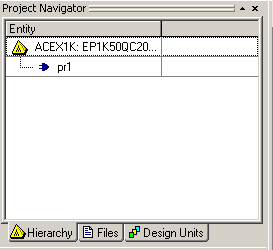

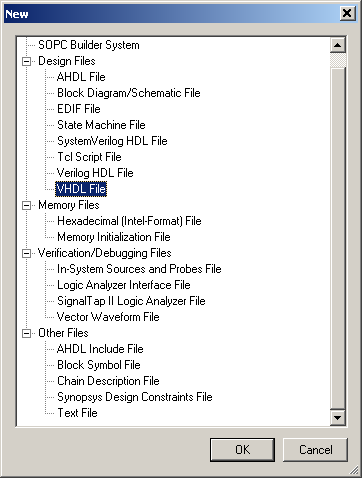

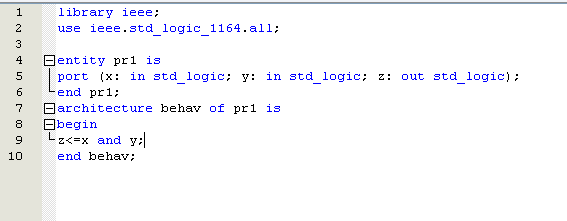

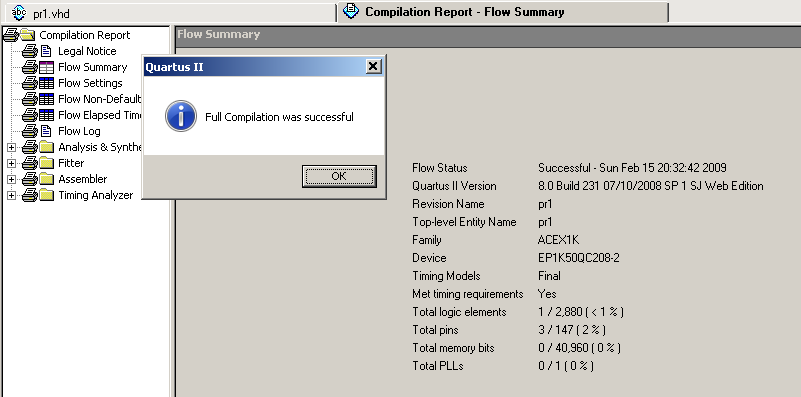

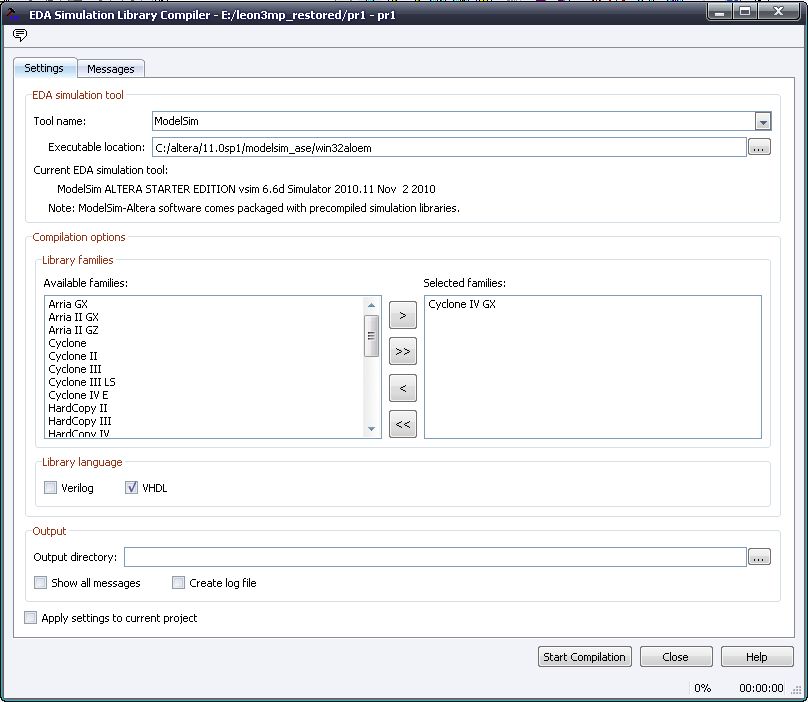

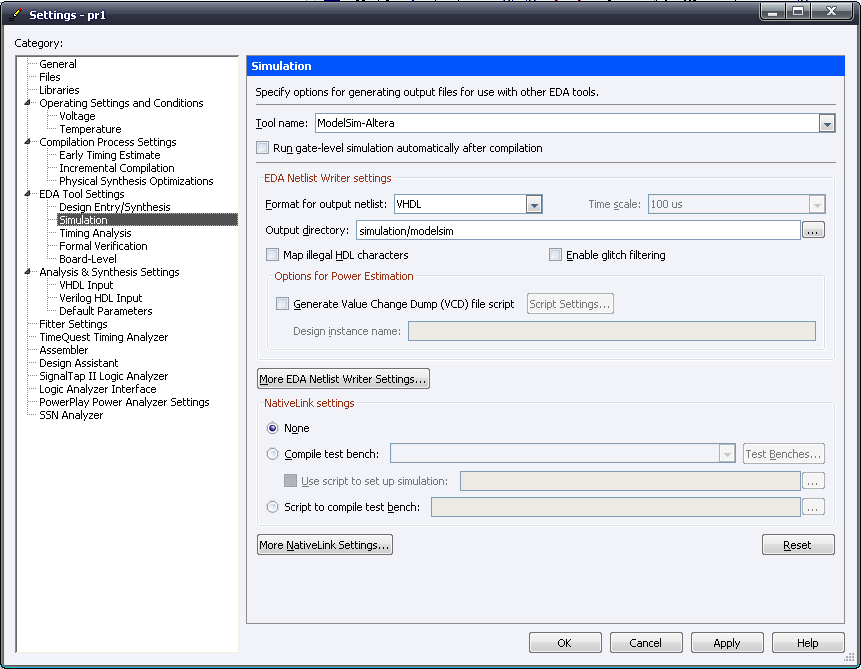

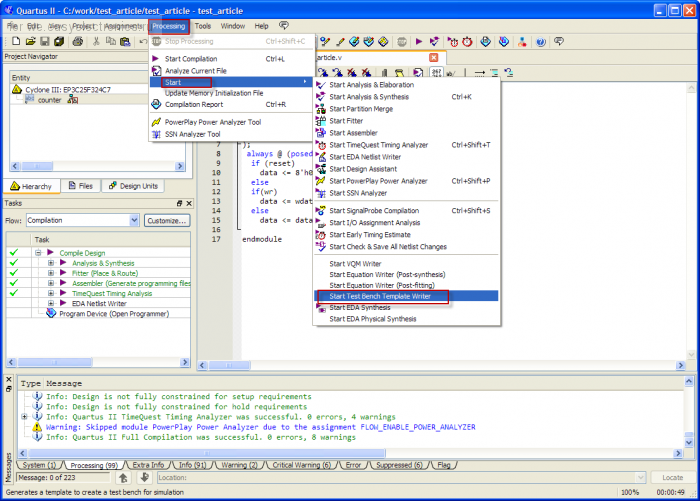

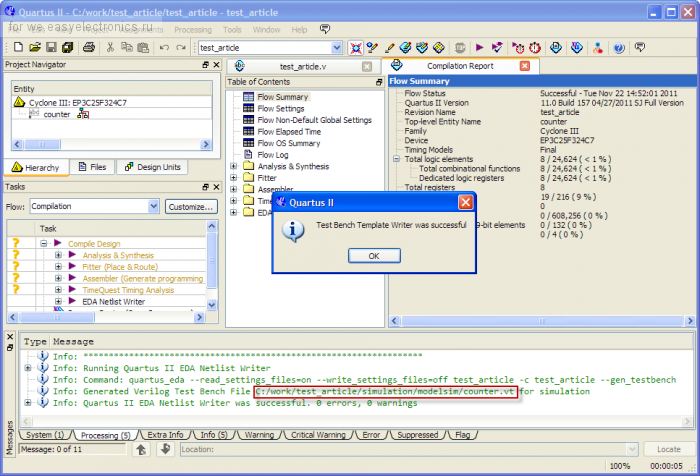

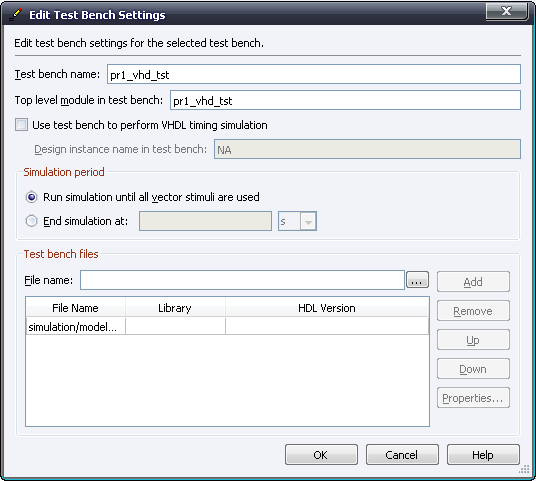

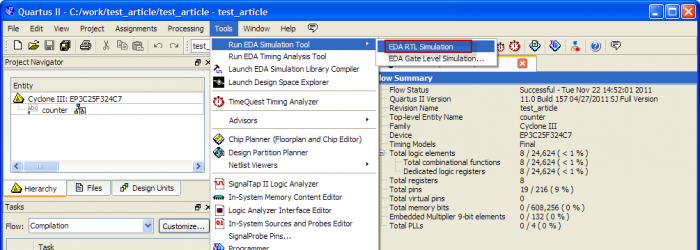

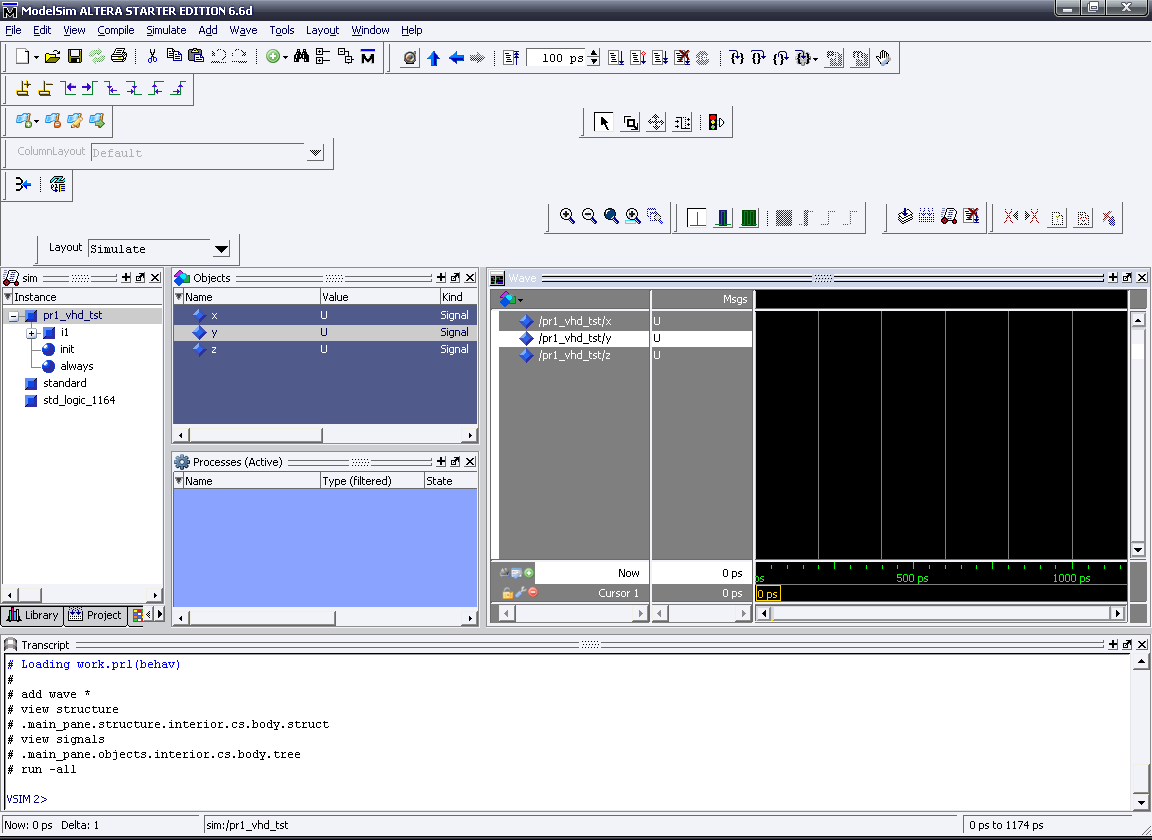

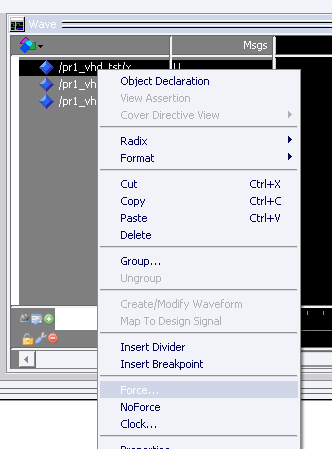

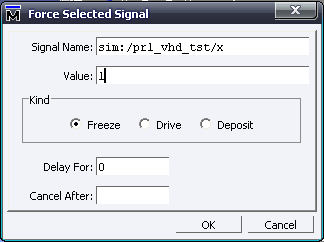

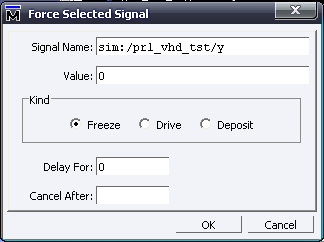

Лабораторная работа 1 СРЕДА ПРОЕКТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ QUARTUS (4 часа) Цель работы: изучение основных этапов проектирования цифровых устройств с помощью интегрированной среды проектирования цифровых устройств Quartus II. Задачи работы: 1. ознакомление с этапами проектирования цифровых устройств в среде Quartus II; 2. ознакомление со средой разработки; 3. создание первых моделей. ОглавлениеОглавление 1 1. ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ 1.1. Возможности пакета Quartus II Quartus II является интегрированным средством проектирования цифровых устройств на элементной базе сверхбольших интегральных схем (СБИС): полузаказных СБИС (ASIC) и перепрограммируемых логических интегральных схем ПЛИС (FPGA), имеющим следующие основные возможности: - текстовые и графические способы ввода проекта; - синтез (Logic synthesis); - трассировка СБИС (Place & route); - моделирование (Simulation); - анализ временных параметров и потребляемой мощности (Timing & power analysis); - программирование СБИС (Device programming). 1.2. Методология проектирования СБИС программируемой логики Проектирование цифровых устройств на элементной базе СБИС программируемой логики включает следующие основные этапы: 1. Задание входной спецификации (технического задания); 2. Создание проекта. Ввод описания проекта; 3. Функциональное моделирование; 4. Синтез; 5. Трассировка СБИС. Программирование СБИС. 1.3. Создание первого проекта в Quartus II Запустите Quartus II. По окончании загрузки общий вид экрана примет вид, представленный на рис.1.  Рис.1. Общий вид QuartusII Для создания проекта пункт New Project Wizard из меню File. Появится окно мастера создания проекта, состоящего из 5 страниц (рис.2).  Рис.2. Окно мастера создания нового проекта – первая страница На первой странице необходимо заполнить 3 строки ввода: В первой строке – расположение рабочей папки для проекта. Каждый проект должен быть выполнен в отдельной папке. Кроме того не стоит создавать рабочую папку в директории C:\altera\80sp1\quartus\bin. Во второй строке указать имя проекта. Обычно имя проекта совпадает с именем рабочей папки. В третьей строке необходимо указать имя верхней сущности главного файла проекта, созданного на VHDL. Данное имя должно обязательно совпадать с именем проекта, поэтому заполнение третьей строки данной страницы происходит автоматически при заполнении второй строки. Заполнив все три строки нажмите клавишу Next. Откроется окно второй страницы мастера создания проекта (рис. 3).  Рис.3. Окно мастера создания нового проекта – вторая страница Окно предназначено для добавления ранее созданных и находящихся в рабочей папке файлов. В нашем случае пока никаких файлов нет и поэтому заполнение данной страницы пропускаем и нажимаем кнопку Next. Появляется третье окно мастера создания проекта (рис. 4). Окно предназначено для выбора семейства, определенной интегральной схемы (ИС) с учетом ограничений на тип корпуса, количества выводов и скорости. Для определенности выберем семейство ACEX1, интегральную схему EP1K50QC208-2. Данная ИС установлена на отладочной плате, с которой придется познакомиться для выполнения последующий лабораторных работ.  Рис.4. Окно мастера создания нового проекта – третья страница Закончив выбор нажимаем Next. Появится следующее окно мастера создания проекта (рис. 5).  Рис.5. Окно мастера создания нового проекта – четвертая страница Данное окно позволяет подключить другие EDA-инструменты (других производителей) для синтеза, моделирования и временного анализа. В наших проектах будут использоваться только штатные инструменты Quartus II, поэтому пропускаем заполнение данного окна и нажимаем кнопку Next. Открывается последняя страница мастера.  Рис.6. Окно мастера создания нового проекта – пятая страница Окно показывает суммарную информацию по ранее выбранным пунктам. Если нас все устраивает – нажимаем кнопку Finish. Проект создан, о чем в Project Navigator появляются соответствующие записи (рис. 6.)  Рис. 7. Появление проекта pr1 в Project Navigator Создадим файл с описанием простейшего цифрового устройства – двухвходового логического элемента «И».  Рис. 8. Окно New Выберем пункт New в меню File. Появится окно New. Выберем в группе Disign Files строку VHDL File и нажмем OK. Появится редактор. В окне редактора наберем описание логического элемента «И».  Рис. 9. Окно с описанием логического элемента «И». Отметим, как уже упоминалось выше, верхнеуровневая сущность должна совпадать с именем указанным в соответствующей строке первой страницы мастера создания проекта New Project Wizard. Сохраним VHDL файл. Файл необходимо сохранить в рабочей папке проекта. Имя главного файла (а он главный раз единственный) должно совпадать с именем проекта. Для компиляции проекта выберем пункт Start Compilation меню Processing. В процессе компиляции будет появляться информация о ходе выполнения данного процесса. Если компиляция завершиться успешно – появится соответствующее сообщение.  Рис. 10. Завершение компиляции проекта. Переходим к симуляции – моделированию цифрового устройства. Конфигурирование NativeLink NativeLink – инструмент для налаживания связи между Quartus и Modelsim (программа, используемая для моделирования работы устройства) Сначало необходимо нажать Tools — Launch EDA Simulation Library Compiler и выставить следующие параметры  Все эти действия выполняется однократно для каждого проекта. Жмем Assignments — Settings — Simulation  Рис. 11. Настройка моделирования. Рис. 11. Настройка моделирования.Ставим настройки в точности как на рис 11. Генерация TestBench и привязка к проекту Собственно это ключевой момент лабораторной работы. Жмем Processing – Start – Start Test Bench Template Writter  Рис. 12. Генерирования файла testbench. Рис. 12. Генерирования файла testbench.В Message можно увидеть где же располагается ваш testbench.  Учтите, это всего лишь шаблон, а не готовый testbench. Quartus не ясновидец, придется все необходимые воздействия писать руками) Теперь надо testbench привязать к проекту.Для этого идем опять в Assignments — Settings — Simulation  Рис. 13. Настройка файла testbench. Делам все как на рис13  Testbench: произвольное имя нашего testbench Top Level in Test Bench: имя топ левел модуля testbench. Чтобы его узнать нужно посмотреть сгенерированный testbench. В моем случае Quartus дал имя pr1_vhd_tst. Test Bench Files: добавляем файл с testbench. В нашем случае pr1.vht Жмем ОК. Настройка закончена! Запуск симуляции Тут все просто: Tools – Run EDA Simulation Tools – EDA RTL Simulation  Дальше начинается не простой этап моделирования и вылавливания ошибок в среде Modelsim.  Зададим исходные значения сигналов x и y. По ходу моделирования их можно изменять.    Выполним моделирование нажав кнопку RUN   2. ЗАДАНИЯ ДЛЯ ВЫПОЛНЕНИЯ Самостоятельно выполните пункт 1.3. Пользуясь приведенным выше примером, промоделируйте работу устройства приведенного на рисунке  Промоделируйте работу устройства заданного следующим логическим выражением  Определите, какому устройству соответствует данное логическое выражение. Нарисуйте ее условное обозначение на электрических принципиальных схемах. 3. КОНТРОЛЬНЫЕ ВОПРОСЫ Определите основные этапы разработки проекта в Quartus. Какой тип моделирования является основным для цифровых устройств? Каким образом определяются задержки цифровых устройств? Каковы типичные задержки цифровых устройств зависимости от сложности (логического элемента, мультиплексора, триггера, статической памяти и т.д.) и вида технологии (ТТЛ, КМОП и др.) |