лабораторная тау. Лабораторная работа 2. Лабораторная работа 2 Исследование базовых схем логических элементов цифровых устройств цель работы

Скачать 120.61 Kb. Скачать 120.61 Kb.

|

|

Лабораторная работа № 2 Исследование базовых схем логических элементов цифровых устройств ЦЕЛЬ РАБОТЫ: Ознакомиться с принципами работы базовых логических элементов транзисторно-транзисторной логики (ТТЛ) и элементов на униполярных транзисторах (МОП), провести исследования логических элементов, приобрести навыки схемотехнического моделирования на персональных компьютерах. ХОД РАБОТЫ: Задание 1.Исследование логических элементов транзисторно-транзисторной логики. Шаг 1: Открыть файл Шаг 2: Запустить симуляцию и создать таблицу истинности (табл. 1) Шаг 3: По таблице истинности ЛЭ записать уравнение логической функции и дать ее условное графическое представление. Материалы задания: Таблица 1

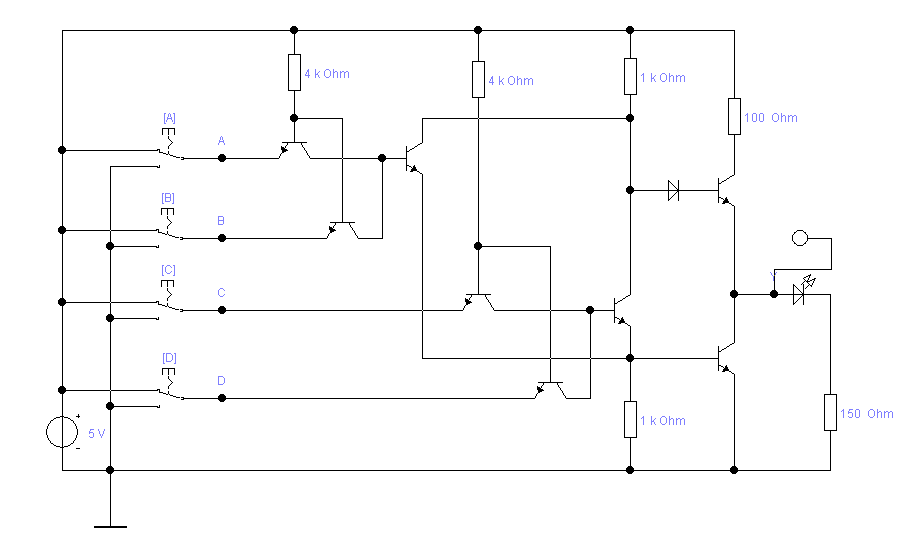

Изображение 1  Логическая функция:  Условное графическое изображение:  Задание 2. Исследование логических элементов на униполярных транзисторах: Шаг 1: Открыть файлы <МОП1.ewb> и <МОП2.ewb>. Выставить значения и обозначения элементов схем в соответствии с приведенными на рис. 2.4, 2.5. Подключить к точкам схемы А,В,Y индикаторы логического уровня. Шаг 2: Включить моделирование. Следить за состоянием индикаторов на входе и выходе схемы, нажимая клавиши А и В. Шаг 3: Составить таблицу истинности (табл. 1) Данный элемент является элементом И-НЕ Шаг 4: Включить моделирование. Следить за состоянием индикаторов на входе и выходе схемы, нажимая клавиши А и В. Шаг 5: Составьте таблицу истинности (табл. 2) Данный элемент является элементом ИЛИ-НЕ Материалы задания: Файл <МОП1.ewb>  Файл <МОП2.ewb>  Таблица 1

Таблица 2

Задание 3. Исследование логических схем ( ручной режим). Шаг 1: Открыть файл Шаг 2: Заполнить таблицу истинности на основе результатов, полученных подавая высокий и низкий логические уровни на входы изображенных логических схем. (табл. 1) Шаг 3: По логике работы исследуемых элементов дать название каждому из элементов и заполнить таблицу. (табл. 2) Материалы задания: файл  Таблица 1

Таблица 2

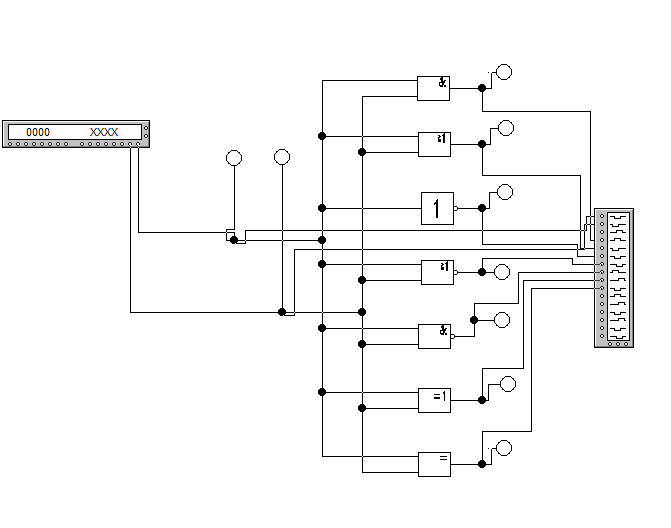

Задание 4. Исследование логических схем (автоматический режим). Шаг 1: На панели инструментов выбрать Word Generator и Loqis Analyzer. Замените источник питания и переключатели в схеме генератором слов Word Generator. Подключить к входам и выходам схемы анализатор логики Loqis Analyzer. (изобр. 1) Шаг 2: Отредактировать четыре первых слова генератора слов в окне Binary, выставив в двоичной системе счисления соответственно 0 (0000), 1 (0001), 2 (0010), 3 (0011). Выставить конечный адрес (Final) 0003. Установить частоту выдачи слов Frequency 1Hz (изобр. 2) Шаг 3: Зафиксировать осциллограммы логических сигналов и дать им интерпретацию. (изобр. 3) На рассмотренных осциллограммах логических сигналов отображена схема работы каждого из рассмотренных элементов Материалы задания: Изображение 1  Изображение 2  Изображение 3  РЕЗУЛЬТАТ РАБОТЫ: В ходе работы мы изучили принципы работы основных логических элементов транзисторно-транзисторной логики (ТТЛ) и элементов на униполярных транзисторах (MOП), изучили логические элементы, приобрели навыки моделирования схем на компьютерах. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||