электроника. 5fan_ru_Микропроцессорная техника. Микропроцессоры и микропроцес. Лекция 12 Микропроцессорная техника 1 Микропроцессоры и микропроцессорные комплекты 1 Определение микропроцессора

Скачать 388.5 Kb. Скачать 388.5 Kb.

|

|

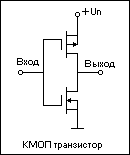

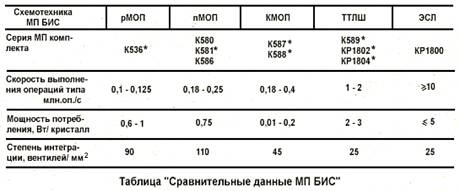

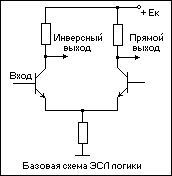

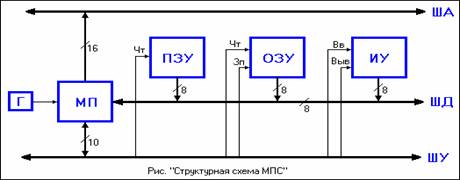

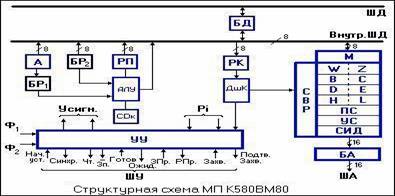

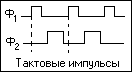

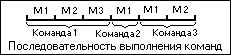

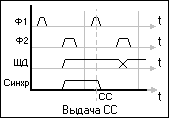

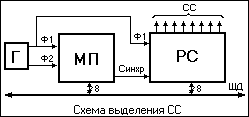

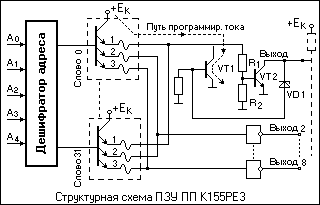

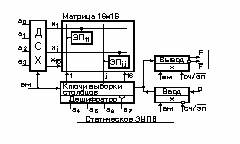

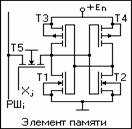

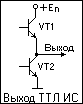

Лекция 12 Микропроцессорная техника 1 Микропроцессоры и микропроцессорные комплекты 1.1 Определение микропроцессора В начале 70-х годов успехи технологии в микроэлектронике привели к созданию новой элементной базы электроники - микроэлектронных больших интегральных схем (БИС) {модуль 1 глава 1.6.3}. По степени интеграции (количеству активных элементов: диодов и транзисторов) интегральные схемы (ИС) условно подразделяются на ИС малой степени интеграции - до 100 активных элементов, средней степени интеграции (СИС) - до 1000 активных элементов, БИС - свыше 1000 активных элементов, СБИС - свыше 10000 элементов. Выпуск новой БИС при современном уровне автоматизации проектирования - очень сложный и дорогой процесс из-за больших первоначальных затрат на разработку ее логической структуры и топологии, изготовления фотошаблонов и технологической подготовки производства. Это 0,5-1 год работы большого коллектива. Поэтому изготовление БИС экономически оправдано при их выпуске, исчисляемом десятками-сотнями тысяч штук в год. Выпускать специализированные БИС для каждого конкретного применения практически не реально. В результате поиска областей массового применения микросхем с высоким уровнем интеграции их разработчиками была предложена идея создания одной универсальной БИС или некоторого набора БИС, специализация которых для каждого конкретного случая применения достигается не схемно, а программно. Так появились стандартные универсальные элементы - микропроцессорные БИС со структурой, аналогичной структуре ЭВМ. Микропроцессор (МП) – это обрабатывающее и управляющее устройство, способное под программным управлением выполнять обработку информации, принятие решений, ввод и вывод информации и выполненное в виде одной или нескольких БИС. 1.2 Технология изготовления МП БИС Существуют два вида технологии изготовления БИС: биполярная - основанная на применении биполярных транзисторов и МОП (металл - окисел - полупроводник) - технология, основанная на использовании полевых транзисторов. БИС, изготавливаемые по биполярной технологии, различаются по схематическим способам реализации. В основном применяется транзисторно-транзисторная логика с диодами Шоттки (ТТЛШ) и эмиттерно-связанная логика (ЭСЛ). В логике ТТЛШ используются биполярные n-p-n транзисторы, дополненные диодами Шоттки (ДШ). ДШ представляет собой выпрямительный контакт на границе металл-полупроводник Al-nSi. В металле и кремнии основные носители одного и того же типа - электроны, а неосновных носителей нет. ДШ открываются при U=0,1-0,3 В и имеют крутую вольт-амперную характеристику. Они подключаются параллельно коллекторному переходу n-p-n транзистора и образуют транзистор Шоттки, изготавливаемый в едином технологическом процессе. Применение ДШ значительно повышает быстродействие транзистора, так как устраняется насыщение коллекторного перехода и нет рассасывания зарядов в нем. В  МОП технологии {модуль 1 глава 1.5.5} можно выделить 3 схемотехнических способа реализации БИС: МОП с проводимостью канала р- или n-типа (р-МОП или n-МОП) и комплементарная МОП технология (КМОП). КМОП технология использует пары МОП транзисторов n-типа и р-типа, соединенные последовательно (рис.1-1). При любом сигнале на входе один из транзисторов открыт, другой - закрыт. Поэтому ток, протекающий по цепи, очень мал. КМОП БИС имеют наименьшую потребляемую мощность по сравнению с другими видами. МОП технологии {модуль 1 глава 1.5.5} можно выделить 3 схемотехнических способа реализации БИС: МОП с проводимостью канала р- или n-типа (р-МОП или n-МОП) и комплементарная МОП технология (КМОП). КМОП технология использует пары МОП транзисторов n-типа и р-типа, соединенные последовательно (рис.1-1). При любом сигнале на входе один из транзисторов открыт, другой - закрыт. Поэтому ток, протекающий по цепи, очень мал. КМОП БИС имеют наименьшую потребляемую мощность по сравнению с другими видами.По МОП технологии первые МП БИС (р-МОП) были изготовлены в 1971 г. В них используется управление р-каналом, где основными носителями зарядов являются дырки. Поэтому быстродействие БИС сравнительно невелико. Позднее появились БИС типа n-МОП и КМОП, которые и сейчас широко применяются. ЭСЛ логика основана на применении дифференциального усилителя на двух транзисторах с соединенными эмиттерами (рис.1-2.). Она обеспечивает самое большое быстродействие, но потребляет большую мощность. Основные данные для некоторых МП БИС приведены в таблице.1   1.3 Структура микропроцессорных систем Все многообразие МПС основано на применении МП двух типов: а) однокристальных МП с фиксированной разрядностью слова и с фиксированной системой команд (с жестким управлением); б) многокристальных (секционных) МП с изменяемой разрядностью слова и с микропрограммным управлением. Рассмотрим особенности их структуры. 1.3.1 Структура МПС на основе МП с жестким управлением  Рис.1-3 Связь отдельных элементов МПС между собой и с внешними устройствами осуществляется с помощью трех шин. Каждая шина представляет собой магистраль, состоящую из нескольких (8-16) линий. ША - шина адреса, по которой передаются адреса ячеек памяти и внешних устройств; ШД - шина данных, по которой информация вводится в МП или выводится из него; ШУ - шина управления, по которой передаются управляющи сигналы, обеспечивающие нормальное функционирование МПС; МП - центральный элемент, управляющий функционированием всех остальных элементов; обращается ко всем остальным элементам системы, выставляя на ША их адрес; Г - генератор тактовых импульсов, синхронизирующий работу МП; ПЗУ - постоянное запоминающее устройство {модуль 2 глава 9.1}, в котором записаны команды программы, выполняемой МП, и константы, необходимые для работы. По ША поступает адрес ячейки памяти, в которой храниться необходимая команда или константа, и по сигналу Чт (чтение) от МП на ШД появляется информация, хранимая в данной ячейке; ОЗУ - оперативное запоминающее устройство {модуль 2 глава 9.2}, используемое для временного хранения информации в процессе работы МП. В отличие от ПЗУ, в ОЗУ возможно как считывание, так и запись информации (по сигналам Чт и Зап) в ячейку, адрес которой находится на ША. В простейших МПС ОЗУ может отсутствовать, и его роль выполняют внутренние регистры общего назначения (РОН) МП; ИУ - интерфейсное устройство (устройство связи), согласующее работу МПС и внешних устройств с учетом различий в скоростях их работы и уровнях сигналов. По сигналу Вв (ввод) на ШУ происходит передача информации от внешнего устройства на ШД, а по сигналу Выв (вывод) - в обратном направлении. Шина данных общая для всех элементов МПС, но элементы системы не должны мешать друг другу. Поэтому выход каждого из них подключен к ШД через так называемую схему с 3-мя состояниями. Она может находиться не только в активных состояниях («0» или «1»), что необходимо для передачи информации, но и в третьем состоянии, в котором элемент практически отключается от общей шины. Перевод из третьего состояния в активное осуществляется управляющими сигналами МП. В каждый момент времени к общей ШД оказывается подключенным только один элемент, передающий информацию, и «конфликт» на ШД исключается. Принимать информацию с ШД могут, при необходимости, сразу несколько элементов. Такая организация МПС с помощью общей ШД является вынужденной и обусловлена тем, что число выводов корпусов БИС ограничено, и одни и те же выводы используются для нескольких целей. 1.3.2 Структура МПС на основе МП с микропрограммным управлением МП с жестким управлением собирается из n отдельных БИС секций центрального процессорного элемента ЦПЭ, каждая из которых обрабатывает 2 (4, 8, 16) разрядов данных. При этим получается центральный процессор, имеющий 2n (или 4n, 8n, 16n) разрядов. ЦПЭ выполняет самые простые действия - микрооперации при подаче на управляющие входы приказов - микрокоманд (МК). Для выполнения команд, аналогичных командам МП с жестким управлением, требуется до 10-15 микроопераций и столько же микрокоманд. Организация команд из имеющихся микрокоманд предоставляется пользователю. Основным преимуществом МП с микропрограммным управлением при их появлении была большая скорость обработки информации, что позволяло управлять и контролировать очень быстро протекающие процессы, например, ядерные реакции. В настоящее время их роль существенно снизилась, так как современные многоразрядные МП с жестким управлением и высокой тактовой частотой позволяют обрабатывать информацию еще быстрее. 2 Микропроцессор 2.1 Структура МП К580ВМ80 Рассматриваемая БИС является однокристальным МП, выполненным на основе n-МОП технологии. Предназначена для построения вычислительных устройств, контроллеров, микро-ЭВМ. Разрядность МП - 8 бит, тактовая частота 2 МГц, время выполнения команды 2-9 мкс, напряжение питания +12,+5 и -5 В, потребляемая мощность 0,75 Вт. На рисунке приведена его структурная схема.  2.1.1 Основные элементы МП Обмен информацией осуществляется через восьмиразрядный буферный регистр {модуль 2 глава 7} БД, подключенный к внешней и внутренней ШД МП.РК - регистр команды. В него записывается код команды и хранится в течение времени ее выполнения.ДшК - дешифратор команды, выдает сигналы на устройство управления УУ и схему выбора регистров СВР. СВР - схема выбора регистров. Содержит: 6 программно доступных регистров общего назначения (РОН) B, C, D, E, H, L (существуют команды, в которых они рассматриваются парами B- B,C; D - D,E; H - H,L);2 программно недоступных регистра W и Z, предназначенных для хранения второго и третьего байта команды (первый байт всегда храниться в РК); М – мультиплексор {модуль 2 глава 5.2}, связывающий внутреннюю ШД с регистрами W, Z; ПС - 16 разрядный программный счетчик, позволяющий МП выполнять программы, содержащие до 216 = 65536 слов; УС - 16 разрядный указатель стека {глава 2.1.3}; СИД - схема инкремента-декремента (прибавления или вычитания 1); БА - 16 разрядный буфер адреса; А - регистр результата (аккумулятор); АЛУ - арифметико-логическое устройство, выполняет арифметические операции сложения - вычитания, инкремент - декремент, логические операции конъюнкции, дизъюнкции, инверсии и другие. Оно связано через буферные регистры БР1 и БР2 с аккумулятором и внутренней шиной данных; РП - регистр признаков, в котором в процессе выполнения команды появляются признаки результата (нулевой результат, положительный или отрицательный, четный или нечетный результат), используемые в последующих командах, например, условного перехода; СДК - схема десятичной коррекции, используется в том случае, когда информация обрабатывается не в двоичном, а в двоично-десятичном коде {модуль 2 глава 3.2}; УУ - устройство управления, обеспечивает управление работой МП и внешних устройств. Рассмотрим его работу и состав шины управления. 2.1.2 Устройство управления Устройство управления тактируется от внешнего генератора, вырабатывающего последовательность импульсов Ф1 и Ф2. Оно связано с остальной частью МП внутренними управляющими сигналами УС и сигналами признаков Pi. С внешней средой УУ связано шиной управления, содержащей 10 линий (4 сигнала поступают извне и 6 сигналов выдает МП). Состав шины управления. 1. Начальная установка (сброс). При подаче «1» на этот вход ПС сбрасывается в 0 и начинается выполнение программы сначала. 2. Синхронизация. Сигнал «1» на этом выходе вырабатывается в начале каждого цикла работы МП (перед каждым обращением МП к любому внешнему элементу). 3. Чтение. Сигнал «1» указывает, что МП готов принять информацию по ШД извне. Этот сигнал обычно подключается ко входу «чтение» ЗУ и устройств ввода. 4. /Зп. Сигнал «0» указывает, что МП выставил на шину данных информацию, подлежащую записи в ОЗУ или выдаче на устройства вывода. 5. Готов. Сигнал «1» на этом входе указывает МП на окончание цикла чтения или записи. Он вырабатывается внешними устройствами по окончании цикла их работы. Если сигнал «1» не поступил, то МП входит в состояние ожидания, в течение которого МП удерживает адрес на ША, управляющий сигнал «чтение» или «запись» и сохраняет открытыми цепи передачи информации через БД. Состояние ожидания сохраняется до поступления «1» - «готов». В случае, когда все внешние элементы работают со скоростью МП или большей, на вход «готов» постоянно подключается «1». 6. Ожидание. Сигнал «1» на этом выходе указывает, что МП в состоянии ожидания. Этот сигнал помогает установить неисправный блок, из-за которого МП остановился. 7. З.Пр. - вход запроса на прерывание {глава 7.2.7}. Сигнал «1» поступает извне при необходимости прервать работу МП. 8. Р.Пр. - разрешение прерывания. Сигнал «1» на этом выходе указывает, что прерывания разрешены. Разрешение и запрещение прерывания производится специальными командами. 9. Захват. При поступлении сигнала «1» МП останавливает работу, БА и БД переводятся в третье состояние. При этом МП отключается от ША и ШД. 10. Подтверждение захвата. Сигнал «1» указывает, что МП находится в состоянии захвата. 2.1.3 Магазинная память - стек При обращении к ячейкам памяти ОЗУ в МПС с процессором К580ВМ80 нужны длинные трехбайтные команды. В первом байте содержится сама команда обращения, а во втором и третьем указывается адрес ячейки памяти. Такая команда выполняется сравнительно долго и при частых обращениях к памяти работа МПС существенно замедляется. Для ускорения работы МПС применяется магазин памяти - стек. Он работает по принципу: первым читается число, записанное последним. Порядок обращения к стеку жесткий, но зато не нужно указывать адрес, и время обращения значительно уменьшается. Стек очень удобен для запоминания промежуточной информации в случае прерывания. Второе его назначение - обеспечение работы с программами. При переходе к подпрограмме содержание РОН пересылается в стек, после выполнения подпрограммы - вызывается из стека в РОН. Стек бывает автономный (встроенный в МП) и внешний (размещенный в ОЗУ). В МП К580ВМ80 используется внешний стек, а в кристалле размещается специальный регистр - указатель стека (УС), в котором хранится адрес первой свободной ячейки стека. Для стека обычно отводятся старшие ячейки памяти ОЗУ. Вначале устанавливается адрес 111 ... 1, при записи адрес декрементируется (А-1), при чтении - инкрементируется (А+1). При работе со стеком на ША выдается содержимое УС, при работе с основной памятью - содержимое РА. 2.2 2.2 Функционирование МП в составе МПС 2.2.1 Алгоритм выполнения команды При выполнении любой команды цикл работы МП всегда начинается с выборки первого байта команды - кода операции (КОп) в регистр команд {глава 2.1.1}. При этом адрес команды из ПС через БА поступает на ША, УУ вырабатывает сигнал чтения, КОп поступает через БД в РК. ДшК анализирует КОп и, если требуется, МП выбирает 2-й и 3-й байты команды в регистры W и Z соответственно. Адрес последующего байта команды формируется в ПС увеличением его содержимого на 1 с помощью СИД. Затем происходит выполнение команды. В конце производится анализ наличия запросов на прерывание (сигнал ЗПр). Если такой запрос имеется - состояние ПС запоминается и происходит переход к программе обработки прерывания. 2.2.2 Временная диаграмма работы МП Работа МП происходит под действием двух неперекрывающихся последовательностей тактовых импульсов Ф1и Ф2 (рис.2-2).  Большинство преобразований информации МП производит по Ф2. Временной интервал, в течение которого выполняется одна микрооперация, называется машинным тактом (обозначается Т1, Т2 и т.д.). Машинным циклом (МЦ) называется последовательность тактов, в течение которых осуществляется обмен информацией между МП и внешним по отношению к нему элементом (обозначается М1, М2 и т.д.). МЦ содержит 3-5 тактов. Выполнение команды происходит за 1-5 МЦ. На рисунке 2-3 условно показана последовательность выполнения трех команд, содержащих различное число МЦ. В цикле М1 всегда происходит выборка первого байта команды. Большинство МП являются тактируемыми цифровыми схемами, работающими под воздействием генератора тактовых импульсов (ГТИ). МП К580ВМ80тактируется ГТИ, вырабатывающим две последовательности не перекрывающихся импульсов Ф1 и Ф2 с периодом Ттакт = 0,5 - 2 мкс.  2.2.3 Слово состояния МП Ш  Д МП не используется в Т1 и начале Т2 для приема и выдачи основной информации. В МП предусмотрены схемы, обеспечивающие выдачу в это время на ШД восьмиразрядного слова состояния (СС). Эти 8 признаков могут использоваться внешними элементами и , в общем случае, позволяют упростить организацию МПС. Слово состояния выдается в начале каждого цикла в такте Т2 во время импульса Ф1 (рис.2-4). Признаки СС характеризуют только данный МЦ. СС выделяется с помощью регистра состояний РС (рис.2-5), в который записывается информация с ШД в момент t, в который одновременно имеются импульсы Ф1 и «Синхр.». МП К580ВМ80 имеет десять типов МЦ и, соответственно, 10 СС, идентифицирующих эти циклы. В таблице 2 приведены СС, соответствующие всем типам МЦ. Д МП не используется в Т1 и начале Т2 для приема и выдачи основной информации. В МП предусмотрены схемы, обеспечивающие выдачу в это время на ШД восьмиразрядного слова состояния (СС). Эти 8 признаков могут использоваться внешними элементами и , в общем случае, позволяют упростить организацию МПС. Слово состояния выдается в начале каждого цикла в такте Т2 во время импульса Ф1 (рис.2-4). Признаки СС характеризуют только данный МЦ. СС выделяется с помощью регистра состояний РС (рис.2-5), в который записывается информация с ШД в момент t, в который одновременно имеются импульсы Ф1 и «Синхр.». МП К580ВМ80 имеет десять типов МЦ и, соответственно, 10 СС, идентифицирующих эти циклы. В таблице 2 приведены СС, соответствующие всем типам МЦ.Рис.2-4  Рис.2-5  Таблица 2 Слова состояния МП К580ВМ80 Здесь: MEMR - чтение из памяти; INP - признак команды ввода (вырабатывается в МЦ3); М1 - признак МЦ1 (идет выборка КОп, начало выполнения команды); OUT - признак команды ввода, вырабатывается в МЦ3. Аналогичен сигналу /Зп МП, но появляется несколько раньше и держится в РС до конца цикла; HLTA - подтверждение останова; STACK - признак работы со стеком, вырабатывается при обращении к ЗУ по командам работы со стеком, что позволяет иметь 216 ячеек ОЗУ и 216 ячеек стека; /WO - признак записи или вывода; INTA - признак начала работы в режиме прерывания. Например, в команде вывода в трех МЦ выдаются СС № 1,2,7. Использование СС позволяет лучше организовать управление МПС. Для работы с внешними устройствами МП имеет только 2 управляющих сигнала Чт и /Зп, в которых не различаются ПЗУ, ОЗУ и другие внешние устройства. Поэтому приходится использовать некоторые разряды ША для указания конкретного объекта. В СС сигнал MEMR позволяет отделить память от других устройств, что упрощает организацию взаимосвязи отдельных частей МПС. 3 Запоминающие устройства Запоминающее устройство, или, сокращенно, память служит для хранения цифровой информации. Память МПС подразделяется на: программную память, предназначенную для хранения программ и реализованную обычно в виде постоянного запоминающего устройства (ПЗУ); память данных, или оперативную память (ОЗУ) {модуль 2 глава 9}; внешнюю память для хранения больших массивов информации, обычно реализованную в виде накопителя на магнитном диске (винчестере). Чаще всего в МПС применяются полупроводниковые ПЗУ и ОЗУ. Они обладают такими достоинствами, как высокое быстродействие, малое потребление энергии, высокая надежность, дешевизна, электрическая совместимость с другими компонентами МПС. Основной недостаток полупроводникового ОЗУ - его энергозависимость. Оно не сохраняет информацию при выключении питания. Когда это недопустимо ОЗУ имеет резервное питание от батарей или аккумуляторов , но это усложняет и удорожает систему. В функциональном отношении память состоит из однотипных ячеек (регистров), рассчитанных на хранение одного слова. Каждой ячейке присвоен адрес, представленный двоичным кодом. Емкость ИС памяти обычно выражается в битах или байтах- т, 1024 байта (или 1 Кбайт), 4 К бита и т.д. Информационная организация (или формат) памяти определяется произведением m (слов) х n (длина слова). Например, ИС с емкостью 1024 бит может иметь огранизацию 1024х1 (1Кх1), 256х4, 128х8. Длина слов памяти (nпам) обычно выбирается равной длине слова (разрядности) центрального процессора МПС nцп. Если nпам< nцп, то применяется несколько корпусов ИС. Например, с помощью 2-х ИС памяти 256х4 можно организовать ЗУ с форматом 256х8. Память может выполнять две операции: ввод информации в адресуемую ячейку - запись (Зп); и вывод информации из адресуемой ячейки - считывание или чтение (Чт). Обе операции носят общее название обращения или, по-другому, доступа к памяти. 3.1 Постоянная память Если в работающей системе память выполняет только операцию считывания, то ее называют постоянной памятью или ПЗУ. Запись информации в ПЗУ может осуществляться разными способами. В кристаллы ПЗУ, программируемых маской (ПЗУ-ПМ), запись производится только один раз в процессе изготовления с помощью специальной маски (фотошаблона). Изменить хранящуюся информацию невозможно. ПЗУ-ПМ имеют высокую надежность и быстродействие, большую плотность упаковки, энергонезависимость. Стоимость их при массовом производстве низка. Они применяются для хранения неизменяющихся программ и различных констант. Если однократную запись в память производит пользователь с помощью специального устройства - программатора, а затем она работает только на считывание, то такую память называют ПЗУ, программируемое пользователем (ПЗУ-ПП). Они применяются при макетировании и отладке МПС, а также при производстве малыми сериями. Применяются также перепрограммируемые ПЗУ (ППЗУ). Запись информации в них может производиться пользователем неоднократно с помощью программатора, но в работающей системе они выполняют только операцию считывания. Информацию в ППЗУ можно стереть, а затем записать в них новую информацию. Стирание производится с извлечением ИС из системы и выполняется либо электрическими импульсами амплитудой 30-50 В, либо с помощью ультрафиолетового излучения, ППЗУ дороже ПЗУ-ПМ и ПЗУ-ПП и имеют меньшую плотность упаковки. Рассмотрим подробнее внутреннюю структуру ПЗУ ПП на примере простейшей ИС К155РЕ3 (рис.3-1), имеющей организацию 32х8. Для адресации 32-х слов имеются 5 адресных входов А0...А4 (т.к. 25=32). Хранимое слово из 8-ми бит образовано многоэмиттерным транзистором, в каждой эмиттерной цепи которого находится плавкая перемычка из нихрома толщиной 200 Ангстрем. Когда дешифратор адреса выбирает определенное слово, то открывается один из многоэмиттерных транзисторов. При наличии перемычки на соответствующей битовой линии устанавливается высокий уровень напряжения и выходной транзистор VT2 также открывается, и потенциал выхода 1 близок к нулю (логический «0»). Если перемычка расплавлена, то соответствующая битовая линия никуда не подключена («плавающая») и транзистор VT2 закрыт (логическая «1»). Выходы ПЗУ ПП представляют собой схемы с открытым коллектором .Для нормальной работы их надо подключить к источнику питания +Ек через резисторы Rн (на рисунке показано пунктиром).  В незапрагроммированной ИС все перемычки целые, транзисторы VT2 открыты во всех словах, на выходах уровни логического «0». Для программирования некоторого бита (состояние которого необходимо изменить с «0» на «1») на линии А0...А4 подаются сигналы нужного адреса и на базе выбранного многоэмиттерного транзистора появляется высокий уровень. Внешней схемой на выходе программируемого бита устанавливается напряжение около 8 В. Этого напряжения достаточно для включения стабилитрона VD1 с порогом около 7 В, что приводит к включению транзистора VT1, и первый вывод перемычки заземляется. Затем напряжение питания многоэмиттерных транзисторов увеличивается до 12 В, и тогда между выводами перемычки приложено напряжение около 5 В. Возникающий ток нагревает и расплавляет перемычку. В ПЗУ ПП такого типа иногда возможны отказы из-за повторных замыканий разрушенных перемычек. Зазор очень узкий и иногда «заплывает». Для повышения надежности запрограммированные ПЗУ выдерживают в термостате 24 часа при температуре 100oС и повторно проверяют записанную информацию. Если обнаружено «заплывание» перемычек (некоторые записанные «1» превратились в «0»), то их прожигают повторно. На практике широко применяются ППЗУ, стираемые ультрафиолетовым облучением. Они строятся на МОП-транзисторах, отличающихся от обычных тем, что между затвором и полупроводником (подложкой) помещают еще один «плавающий» затвор, полностью изолированный со всех сторон окислом кремния. Если при записи информации к затворам таких транзисторов приложить положительное напряжение около 25 В и длительностью в несколько десятков миллисекунд, то под его воздействием электроны, перемещаясь в сторону основного затвора, оседают на плавающем затворе. При считывании к затвору прикладывается положительное напряжение не более 5 В. Если на плавающем затворе нет электронов, то канал исток-сток становится проводящим, что соответствует хранению логической единицы. Если на плавающем затворе имеются электроны, то они своим зарядом экранируют затвор и промежуток исток-сток остается непроводящим, что соответствует хранению логического «0». Так как плавающий затвор окружен изолирующим слоем, электроны, попавшие в область плавающего затвора, не могут ее покинуть. В действительности же существует утечка электронов, что приводит к постепенной потере информации. По данным ряда фирм это время составляет не менее 10 лет. Стирается информация ультрафиолетовым облучением в течение нескольких десятков минут во всех элементах сразу. При этом электроны возбуждаются излучением и стекают в подложку. В результате все плавающие затворы освобождаются от электронов, то есть во все элементы записывается логическая «1». К таким ППЗУ относятся широко применяемые ИС К573РФ2 (РФ4,РФ5 и др.). 3.2 Оперативная память Оперативная память или оперативное запоминающее устройство (ОЗУ) {модуль 2 глава 9.2} применяется для хранения оперативной информации, требующейся в процессе обработки. ОЗУ, в отличие от ПЗУ, позволяет: как вводить информацию в адресуемую ячейку (операция Зп), так и выводить (операция Чт) Так как обращение возможно к любой адресуемой ячейке в произвольном порядке, то такие ЗУ называют запоминающими устройствами с произвольной выборкой (ЗУПВ). Возможны различные способы обмена информацией между ОЗУ и МП. Чаще всего используются запоминающие устройства с произвольной выборкой, позволяющие обращаться по любому адресу в произвольном порядке. Различают статические и динамические ОЗУ. Статическое ОЗУ реализуется на триггерах с непосредственной связью, которые при включенном питании могут хранить информацию неограниченно долго без дополнительных управляющих сигналов. Большинство ЗУПВ изготовляются на основе МОП транзисторов и имеют так называемую матричную организацию. Функциональная схема ЗУПВ 256х1 с матричной организацией типа 16х16 приведена на рисунке (3-2). После дешифрирования младших битов адреса А0-А3 возникает сигнал Xi, подключающий i-ю строку матрицы. Столбец матрицы Yj выбирается дешифратором старших битов адреса А4-А7 и элемент памяти ЭПij подключается к схеме вывода или ввода информации в зависимости от значения сигнала Сч//Зп. При Сч//Зп=1 происходит считывание информации из памяти; при Сч//Зп=0 - запись в память. Разрешающий сигнал ВМ (выбор микросхемы) активизирует данную ИС. При запрещающем значении сигнала ВМ матрица изолирована от выходов дешифратора и шины ввода-вывода. Статические ЗУПВ могут быть построены на полупроводниковых приборах различного типа. В настоящее время наиболее распространенными являются ИС статической памяти на МОП транзисторах. КМОП запоминающий элемент состоит из 5-ти транзисторов, четыре из которых (VT1-VT4) образуют триггер. Управление триггером для записи и считывания осуществляется с помощью ключа - транзистора VT5 (рис.3-3).   В динамических ОЗУ информация хранится в виде некоторого заряда на емкости между затвором информационного МОП-транзистора и общей точкой схемы - землей и паразитной емкости. При комнатной температуре на этой емкости заряд сохраняется в течение десятков миллисекунд. С увеличением температуры ток разряда через МОП транзисторы быстро увеличивается и при 100oС допустимое время сохранения заряда составляет около 2 мс. Для восстановления заряда на запоминающей емкости ее надо периодически подключать к источнику питания, то есть производить регенерацию хранимых данных, что значительно усложняет схему управления. Но количество транзисторов в запоминающем элементе уменьшается до 2-3. Это позволяет значительно увеличить плотность упаковки и уменьшить потребляемую мощность, особенно в режиме хранения. Динамическая память применяется в системах, требующих больших объемов хранимой информации. 3.3 Подключение ЗУ к шине данных Так как шина данных (ШД) является общей для многих устройств, то при их одновременной работе неизбежен «конфликт». Необходимо, чтобы в каждый момент времени к ШД было подключено только одно устройство - источник информации. приемников же информации может быть одновременно подключено несколько. Важно лишь, чтобы мощность выхода источника информационных сигналов была достаточной для подключения нескольких приемников. Оперативное подлючение и одключение выхода какого-либо устройства осуществляется с помощью схемы выхода, имеющей 3 возможных состояния: 1, 0 и «отключено». Выход любой ТТЛ ИС упрощенно можно представить в виде двух последовательно включенных транзисторов (см. рис.3-4). Если транзистор VT1 открыт и закрыт VT2, то на выходе высокий уровень сигнала («1»). Если наоборот: VT2 открыт, VT1 закрыт, то на выходе низкий уровень («0»). Если одновременно закрыты оба транзистора, то выход ИС оказывается отключенным от источника питания и не оказывает никакого влияния на работу других устройств, подключенных к общей шине.  Рис.3-4 Выход с тремя состояниями 4. Интерфейсные устройства Интерфейсные устройства (ИУ) служат для сопряжения внешних устройств с МПС. Они обычно реализуются в виде одной или нескольких СИС или БИС. |